# **Enpirion® Power Datasheet**

EP5368QI 600mA PowerSoC Synchronous Buck Regulator With Integrated Inductor

### **Description**

The EP5368QI is a synchronous buck converter integrated Inductor. PWM controller. with MOSFETS, and Compensation providing the smallest possible solution size. The EP5368QI requires only two small MLCC capacitors to make a complete solution. Integration of the inductor greatly simplifies design, contains noise, reduces part count, and reduces solution footprint. Low output ripple ensures compatibility with RF systems.

The EP5368QI operates at a switching frequency of 4 MHz, enabling this unprecedented level of integration and small external components. Type III voltage mode control is used to provide high noise immunity and wide control loop bandwidth. The device can source 600mA of current over the industrial temperature range and up to 700mA over the commercial temperature range.

The small footprint makes this part ideal for space constrained applications. Output voltage is programmed via a 3-pin VID selector providing seven pre-programmed output voltages along with an option for external resistor divider.

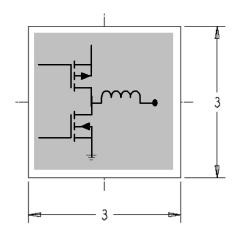

Figure 1: Features INTEGRATED INDUCTOR TECHNOLOGY

#### **Features**

- Integrated Inductor

- 3mm x 3mm x 1.1mm QFN package

- Only two low cost MLCC caps required

- 4 MHz switching frequency

- High efficiency, up to 94%

- Up to 700mA continuous output current

- Wide 2.4V to 5.5V input range

- V<sub>OUT</sub> Range 0.603V to V<sub>IN</sub> 0.4V

- 100% duty cycle capable

- Less than 1 μA standby current

- Low V<sub>OUT</sub> ripple for RF compatibility

- Short circuit and over current protection

- UVLO and thermal protection

- Stable over entire operating range

- RoHS compliant; MSL 3 260°C reflow

### **Application**

- Noise sensitive RF applications

- Area constrained applications

- Smart phones and PDAs

- Personal Media Players

- Advanced Mobile Processors, DSP, IO, Memory, Video, Multimedia Engines

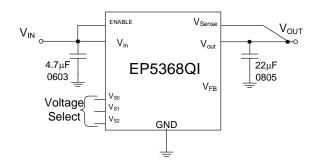

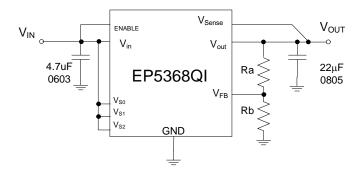

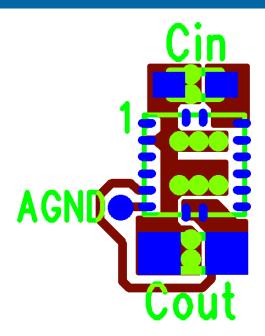

**Figure 2: Typical Application Schematic**

Rev H

## Ordering Information

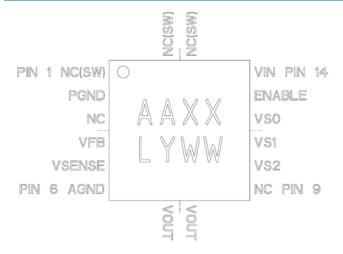

# Pin Assignments (Top View)

| Part Number  | Temp Rating<br>(°C)       | Package        |  |  |

|--------------|---------------------------|----------------|--|--|

| EP5368QI     | -40 to +85                | 16-pin QFN T&R |  |  |

| EVB-EP5368QI | EP5368QI Evaluation Board |                |  |  |

Figure 3: Pin Out Diagram (Top View)

# **Pin Description**

| PIN           | NAME             | FUNCTION                                                                                                                                                                                                                                                                                                                                                                             |

|---------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 15,<br>16  | NC (SW)          | NO CONNECT – These pins are internally connected to the common switch node of the internal MOSFETs. NC(SW) pins are not to be electrically connected to any external signal, voltage, or ground. These pins must be soldered to the PCB. Failure to follow this guideline may result in part malfunction or damage.                                                                  |

| 2             | PGND             | Power Ground                                                                                                                                                                                                                                                                                                                                                                         |

| 3,9           | NC               | NO CONNECT - These pins are not electrically connected internally. They may be connected to ground externally if necessary to increase trace width in layout. These pins must be soldered to the PCB.                                                                                                                                                                                |

| 4             | $V_{FB}$         | Feed back pin for external divider option. When using the external divider option (VS0=VS1=VS2= high) connect this pin to the center of the external divider. Set the divider such that VFB = 0.6V. The "ground" side of the external divider should be connected to AGND.                                                                                                           |

| 5             | $V_{SENSE}$      | Sense pin for preset output voltages. Connect to the output capacitor.                                                                                                                                                                                                                                                                                                               |

| 6             | AGND             | Analog ground. This is the quiet ground for the internal control circuitry.                                                                                                                                                                                                                                                                                                          |

| 7, 8          | V <sub>OUT</sub> | Regulated Output Voltage                                                                                                                                                                                                                                                                                                                                                             |

| 10, 11,<br>12 | VS2, VS1,<br>VS0 | Output voltage select. VS2=pin10 VS1=pin11, VS0=pin12. Selects one of seven preset output voltages or choose external divider by connecting pins to logic high or low. Logic low is defined as $V_{LOW} \le 0.4V$ . Logic high is defined as $V_{HIGH} \ge 1.4V$ . Any level between these two values is indeterminate. (Refer to section on output voltage select for more detail). |

| 13            | ENABLE           | Output enable: Enable = logic high, disable = logic low. Logic low is defined as $V_{LOW} \le 0.4V$ . Logic high is defined as $V_{HIGH} \ge 1.4V$ . Any level between these two values is indeterminate.                                                                                                                                                                            |

| 14            | $V_{IN}$         | Input voltage pin. Supplies power to the IC.                                                                                                                                                                                                                                                                                                                                         |

### **Absolute Maximum Ratings**

CAUTION: Absolute Maximum ratings are stress ratings only. Functional operation beyond the recommended operating conditions is not implied. Stress beyond the absolute maximum ratings may cause permanent damage to the device. Exposure to absolute maximum rated conditions for extended periods may affect device reliability.

| PARAMETER                                                                   | SYMBOL           | MIN  | MAX                  | UNITS |

|-----------------------------------------------------------------------------|------------------|------|----------------------|-------|

| Input Supply Voltage                                                        | V <sub>IN</sub>  | -0.3 | 7.0                  | ٧     |

| Voltages on: ENABLE, V <sub>SENSE</sub> , V <sub>S0</sub> – V <sub>S2</sub> |                  | -0.3 | V <sub>IN</sub> +0.3 | V     |

| Voltage on: V <sub>FB</sub>                                                 |                  | -0.3 | 2.7                  | V     |

| Storage Temperature Range                                                   | T <sub>STG</sub> | -65  | 150                  | °C    |

| Reflow Temp, 10 Sec, MSL3 JEDEC J-STD-020C                                  |                  |      | 260                  | °C    |

| ESD Rating (based on Human Body Mode)                                       |                  |      | 2000                 | V     |

### **Recommended Operating Conditions**

| PARAMETER                      | SYMBOL         | MIN  | MAX | UNITS |

|--------------------------------|----------------|------|-----|-------|

| Input Supply Voltage           | $V_{IN}$       | 2.4  | 5.5 | V     |

| Operating Ambient Temperature  | T <sub>A</sub> | - 40 | 85  | °C    |

| Operating Junction Temperature | TJ             | - 40 | 125 | °C    |

### **Thermal Characteristics**

| PARAMETER                                       | SYMBOL            | TYP | UNITS |

|-------------------------------------------------|-------------------|-----|-------|

| Thermal Resistance: Junction to Ambient (0 LFM) | $\theta_{\sf JA}$ | 85  | °C/W  |

| Thermal Overload Trip Point                     | T <sub>J-TP</sub> | 150 | °C    |

| Thermal Overload Trip Point Hysteresis          |                   | 15  | °C    |

### **Electrical Characteristics**

NOTE:  $T_A$ = -40°C to +85°C unless otherwise noted. Typical values are at  $T_A$  = 25°C,  $V_{IN}$  = 3.6V  $C_{IN}$  = 4.7 $\mu$ F 0603 MLCC,  $C_{OUT}$  = 22 $\mu$ F 0805 MLCC

| PARAMETER                                                                                      | SYMBOL                          | TEST CONDITIONS                                                                                                                                                                                                                                       | MIN          | TYP  | MAX                                       | UNITS |

|------------------------------------------------------------------------------------------------|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------|-------------------------------------------|-------|

| Operating Input Voltage Range                                                                  | V <sub>IN</sub>                 |                                                                                                                                                                                                                                                       | 2.4          |      | 5.5                                       | V     |

| Under Voltage Lock-out –<br>V <sub>IN</sub> Rising                                             | $V_{\text{UVLO}_{R}}$           |                                                                                                                                                                                                                                                       |              | 2.2  | 2.3                                       | V     |

| Under Voltage Lock-out – V <sub>IN</sub> Falling                                               | $V_{\text{UVLO}_{\text{F}}}$    |                                                                                                                                                                                                                                                       |              | 2.1  | 2.2                                       | V     |

| Drop Out Resistance                                                                            | R <sub>DO</sub>                 | Input to Output Resistance in 100% duty cycle operation.                                                                                                                                                                                              |              | 400  | 500                                       | mΩ    |

| Output Voltage Range                                                                           | V <sub>OUT</sub>                | External Feedback Mode<br>VID Mode                                                                                                                                                                                                                    | 0.603<br>0.8 |      | V <sub>IN</sub> -V <sub>DO</sub> *<br>3.3 | V     |

| Dynamic Voltage Slew<br>Rate (VID Change)                                                      | V <sub>SLEW</sub>               |                                                                                                                                                                                                                                                       | 0.975        | 1.5  | 2.025                                     | V/mS  |

| V <sub>OUT</sub> Initial Accuracy (VID<br>Preset Mode)                                         | $\Delta V_{	ext{OUT\_INITIAL}}$ | $T_A = 25^{\circ}C$ , $V_{IN} = 3.6V$ ;<br>$I_{LOAD} = 100mA$ ;<br>$0.8V \le V_{OUT} \le 3.3V$                                                                                                                                                        | -2           |      | +2                                        | %     |

| V <sub>OUT</sub> Accuracy (VID<br>Preset Mode)<br>over line, load and<br>temperature variation | $\Delta V_{OUT\_ALL}$           | $-40^{\circ}\text{C} \le \text{T}_{\text{A}} \le +85^{\circ}\text{C}$<br>$2.4\text{V} \le \text{V}_{\text{IN}} \le 5.5\text{V};$<br>$0.8\text{V} \le \text{V}_{\text{OUT}} \le 3.3\text{V}$<br>$0\text{A} \le \text{I}_{\text{LOAD}} \le 700\text{A}$ | -3           |      | +3                                        | %     |

| Feedback Pin Voltage<br>Initial Accuracy                                                       | $\Delta V_{FB\_INITIAL}$        | $T_A = 25^{\circ}C$ , $V_{IN} = 3.6V$ ;<br>$I_{LOAD} = 100mA$ ;<br>$0.8V \le V_{OUT} \le 3.3V$                                                                                                                                                        | 0.591        | .603 | 0.615                                     | V     |

| Feedback Pin Voltage<br>Accuracy over line, load,<br>and temperature variations                | $\Delta {\sf V}_{\sf FB\_ALL}$  | $-40^{\circ}\text{C} \le \text{T}_{\text{A}} \le +85^{\circ}\text{C}$<br>$2.4\text{V} \le \text{V}_{\text{IN}} \le 5.5\text{V};$<br>$0.8\text{V} \le \text{V}_{\text{OUT}} \le 3.3\text{V}$<br>$0\text{A} \le \text{I}_{\text{LOAD}} \le 700\text{A}$ | 0.585        | .603 | 0.621                                     | V     |

| Feedback Pin Input<br>Current                                                                  | I <sub>FB</sub>                 |                                                                                                                                                                                                                                                       |              |      | 100                                       | nA    |

| Continuous Output Current                                                                      | l <sub>out</sub>                | $V_{IN} = 5V$ , 0.603V $< V_{OUT} < 3.3V$ ,<br>$T_A = -40$ °C to $+85$ °C                                                                                                                                                                             | 600          |      |                                           | mA    |

| Continuous Output Current                                                                      | I <sub>OUT</sub>                | $V_{IN}$ = 5V, 0.603V < $V_{OUT}$ < 3.3V,<br>$T_A$ = -10°C to +85°C<br>(Application Circuit Figure 6)                                                                                                                                                 | 700          |      |                                           | mA    |

| Shut-Down Current                                                                              | I <sub>SD</sub>                 | Enable = Low                                                                                                                                                                                                                                          |              | 0.75 |                                           | μΑ    |

| PFET OCP Threshold                                                                             | I <sub>ILM</sub>                | $2.4V \le V_{IN} \le 5.5V$ , $0.6V \le V_{IN} \le 3.3V$                                                                                                                                                                                               | 1.4          | 2    |                                           | Α     |

| VS0-VS2, Enable Voltage<br>Threshold                                                           | $V_{TH}$                        | Pin = Low                                                                                                                                                                                                                                             | 0.0          |      | 0.4                                       |       |

|                                                                                                |                                 | Pin = High                                                                                                                                                                                                                                            | 1.4          | 4    | V <sub>IN</sub>                           | ^     |

| VS0-VS2 Pin Input Current                                                                      | I <sub>VSX</sub>                |                                                                                                                                                                                                                                                       |              | 1    |                                           | nA    |

| Operating Frequency                                                                            | Fosc                            |                                                                                                                                                                                                                                                       | 0.075        | 4    | 0.005                                     | MHz   |

| Soft-Start Slew Rate                                                                           | V <sub>SS</sub>                 | VID programming mode                                                                                                                                                                                                                                  | 0.975        | 1.5  | 2.025                                     | V/mS  |

| V <sub>OUT</sub> Rise Time                                                                     | T <sub>SS</sub>                 | VFB programming mode                                                                                                                                                                                                                                  | 0.784        | 1.2  | 1.628                                     | mS    |

<sup>\*:</sup>  $V_{DO} = I_{OUT} \times R_{DO}$

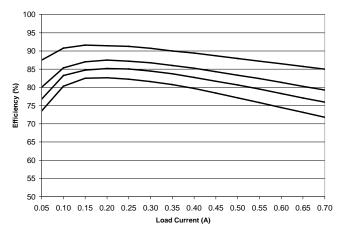

### Typical Performance Characteristics

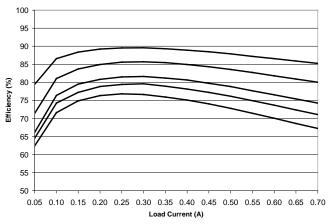

Efficiency Versus Load;  $V_{IN} = 3.3V$ ,  $V_{OUT}$  (from top to bottom) 2.5V, 1.8V, 1.5V, 1.2V.

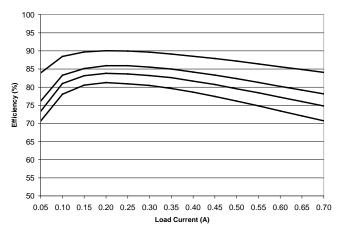

Efficiency Versus Load;  $V_{IN} = 5V$ ,  $V_{OUT}$  (from top to bottom) 3.3V, 2.5V, 1.8V, 1.5V, 1.2V.

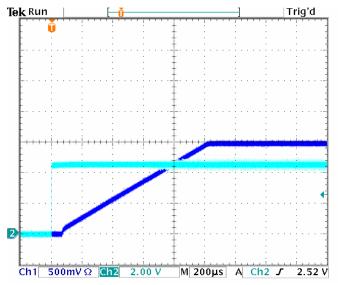

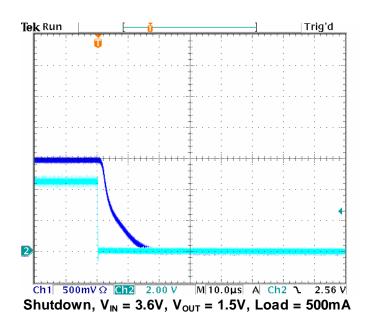

Startup,  $V_{IN} = 3.6V$ ,  $V_{OUT} = 1.5V$ , Load = 500mA

Efficiency Versus Load;  $V_{IN} = 3.7V$ ,  $V_{OUT}$  (from top to bottom) 2.5V, 1.8V, 1.5V, 1.2V.

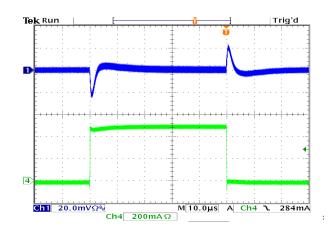

Transient,  $V_{IN} = 3.6V$ ,  $V_{OUT} = 1.2V$ , Load = 0-500mA

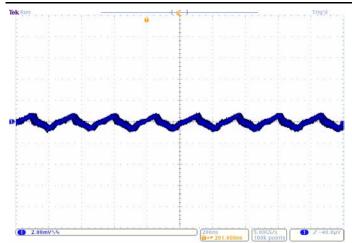

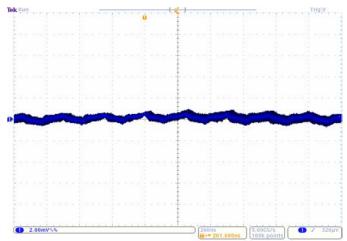

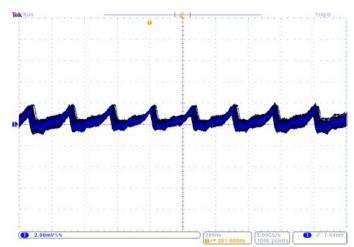

Voltage Ripple,  $V_{IN} = 3.3V$ ,  $V_{OUT} = 1.8V$ , Load = 0mA  $C_{OUT} = 1x \ 22\mu F$ , 0805, 2.0mV/Div.

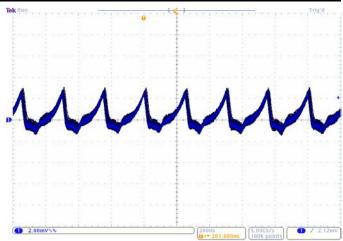

Voltage Ripple,  $V_{IN} = 3.3V$ ,  $V_{OUT} = 1.8V$ , Load = 600mA  $C_{OUT} = 1x\ 22\mu F$ , 0805, 2.0mV/Div.

Voltage Ripple,  $V_{IN}$  = 3.3V,  $V_{OUT}$  = 1.8V, Load = 0mA  $C_{OUT}$  = 2x 10 $\mu$ F, 0805, 2.0mV/Div.

Voltage Ripple,  $V_{IN} = 3.3V$ ,  $V_{OUT} = 1.8V$ , Load = 600mA  $C_{OUT} = 2x \ 10\mu F$ , 0805, 2.0mV/Div.

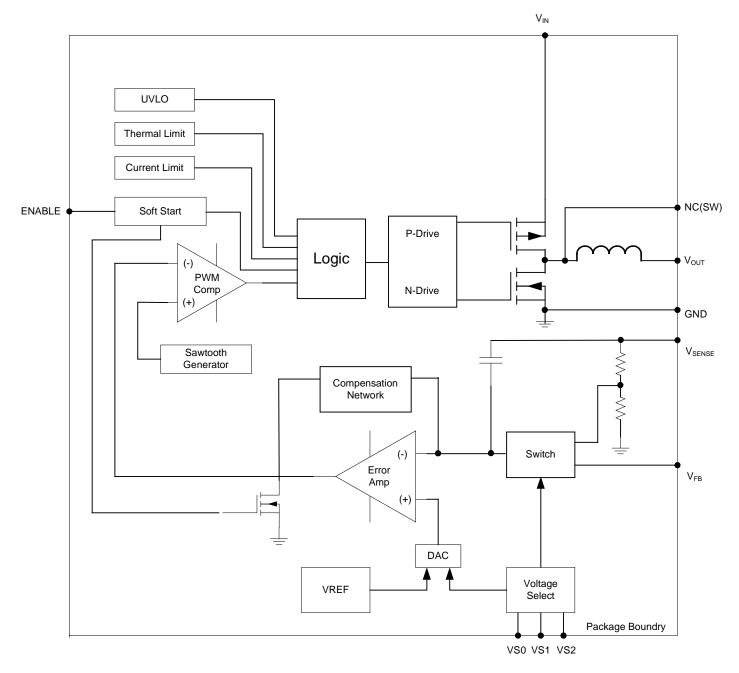

# **Functional Block Diagram**

Figure 4: Functional Block Diagram

### **Detailed Description**

#### **Functional Overview**

The EP5368QI is a complete DCDC converter solution requiring only two low cost MLCC MOSFET capacitors. switches. controller, Gate-drive. compensation, and inductor are integrated into the tiny 3mm x 3mm x 1.1mm package to provide the smallest footprint possible while maintaining efficiency, low ripple, and high performance. The converter uses voltage mode control to provide the simplest implementation and high noise immunity. The device operates at a 4MHz switching frequency. The high switching frequency allows for a wide control loop bandwidth providing excellent transient performance. The high switching frequency further enables the use of verv possible components making this unprecedented level of integration.

Altera Enpirion's proprietary power MOSFET technology provides very low switching loss at frequencies of 4 MHz and higher, allowing for the use of very small internal components, and high performance. Integration of the magnetics virtually eliminates the design/layout issues normally associated with switch-mode DCDC All of this enables much easier converters. and faster incorporation into various applications to meet demanding EMI requirements.

Output voltage is chosen from seven preset values via a three pin VID voltage select An external divider option enables scheme. the selection of any voltage in VIN to 0.603V range. number This reduces the components that must be qualified and reduces inventory burden. The VID pins can be toggled on the fly to implement glitch free dynamic voltage scaling.

Protection features include under-voltage lockout (UVLO), over-current protection (OCP), short circuit protection, and thermal overload protection.

#### Integrated Inductor

Altera has introduced the world's first product

family featuring integrated inductors. The EP5368QI utilizes a proprietary low loss The use of an internal integrated inductor. inductor localizes the noises associated with the output loop currents. The inherent shielding and compact construction of the integrated inductor reduces the radiated noise that couples into the traces of the circuit board. Further, the package layout is optimized to reduce the electrical path length for the AC ripple currents that are a major source of radiated emissions from DCDC converters. The integrated inductor significantly reduces parasitic effects that can harm loop stability, and makes layout very simple.

# Stable Over Wide Range of Operating Conditions

The EP5368QI utilizes an internal type III compensation network and is designed to provide a high degree of stability over a wide range of operating conditions. The device operates over the entire input and output voltage range with no external modifications required. The very high switching frequency allows for a very wide control loop bandwidth.

#### Soft Start

Internal soft start circuits limit in-rush current when the device starts up from a power down condition or when the "ENABLE" pin is asserted "high". Digital control circuitry limits the  $V_{\text{OUT}}$  ramp rate to levels that are safe for the Power MOSFETS and the integrated inductor.

The EP5368QI has two soft start operating modes. When VOUT is programmed using a preset voltage in VID mode, the device has a constant slew rate. When the EP5368QI is configured in external resistor divider mode, the device has a constant VOUT ramp time. Output voltage slew rate and ramp time is given in the Electrical Characteristics Table.

Excess bulk capacitance on the output of the device can cause an over-current condition at startup.

When operating in VID mode, the maximum total capacitance on the output, including the output filter capacitor and bulk and decoupling capacitance, at the load, is given as:

$$C_{\text{OUT\_TOTAL\_MAX}} = C_{\text{OUT\_Filter}} + C_{\text{OUT\_BULK}} = 700 uF$$

When the EP5368QI output voltage is programmed using and external resistor divider the maximum total capacitance on the output is given as:

$$C_{OUT\_TOTAL\_MAX} = 1.251x10^{-3}/V_{OUT}$$

Farads

The above number and formula assume a no load condition at startup.

#### Over Current/Short Circuit Protection

The current limit function is achieved by sensing the current flowing through a sense P-MOSFET which is compared to a reference current. When this level is exceeded the P-FET is turned off and the N-FET is turned on, pulling  $V_{\text{OUT}}$  low. This condition is maintained for a period of 1mS and then a normal soft start is initiated. If the over current condition still persists, this cycle will repeat in a "hiccup" mode.

#### **Under Voltage Lockout**

During initial power up an under voltage lockout circuit will hold-off the switching circuitry until the input voltage reaches a sufficient level to insure proper operation. If the voltage drops below the UVLO threshold, the lockout circuitry will again disable the switching. Hysteresis is included to prevent chattering between states.

#### **Enable**

The ENABLE pin provides a means to shut down the converter or enable normal operation. A logic low will disable the converter and cause it to shut down. A logic high will enable the converter into normal operation. In shutdown mode, the device quiescent current will be less than 1 uA.

**NOTE:** This pin must not be left floating.

#### Thermal Shutdown

When excessive power is dissipated in the chip, the junction temperature rises. Once the junction temperature exceeds the thermal shutdown temperature the thermal shutdown circuit turns off the converter output voltage thus allowing the device to cool. When the junction temperature decreases by 15C, the device will go through the normal startup process.

### **Application Information**

### **Output Voltage Select**

To provide the highest degree of flexibility in choosing output voltage, the EP5368QI uses a 3 pin VID, or Voltage ID, output voltage select arrangement. This allows the designer to choose one of seven preset voltages, or to use an external voltage divider. Internally, the output of the VID multiplexer sets the value for the voltage reference DAC, which in turn is connected to the non-inverting input of the error amplifier. This allows the use of a single feedback divider with constant loop gain and optimum compensation, independent of the output voltage selected.

Table 1 shows the various VS0-VS2 pin logic states and the associated output voltage levels. A logic "1" indicates a connection to VIN or to a "high" logic voltage level. A logic "0" indicates a connection to ground or to a "low" logic voltage level. These pins can be either hardwired to VIN or GND or alternatively can be driven by standard logic levels. Logic low is defined as VLOW ≤ 0.4V. Logic high is defined as VHIGH ≥ 1.4V. Any level between these two values is indeterminate. These pins must not be left floating.

**Table 1 VID Voltage Select Settings**

| VS2 | VS1 | VS0 | $V_{OUT}$          |

|-----|-----|-----|--------------------|

| 0   | 0   | 0   | 3.3V               |

| 0   | 0   | 1   | 2.5V               |

| 0   | 1   | 0   | 1.8V               |

| 0   | 1   | 1   | 1.5V               |

| 1   | 0   | 0   | 1.25V              |

| 1   | 0   | 1   | 1.2V               |

| 1   | 1   | 0   | V8.0               |

| 1   | 1   | 1   | User<br>Selectable |

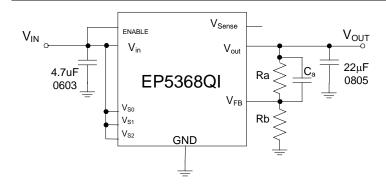

#### **External Voltage Divider**

As described above, the external voltage divider option is chosen by connecting the VS0, VS1, and VS2 pins to  $V_{\rm IN}$  or logic "high". The EP5368QI uses a separate feedback pin,  $V_{\rm FB}$ , when using the external divider.  $V_{\rm SENSE}$  must be connected to  $V_{\rm OUT}$  as indicated in Figure 5.

Figure 5: External Divider Application Circuit

The output voltage is selected by the following formula:

$$V_{OUT} = 0.603V \left(1 + \frac{Ra}{Rb}\right)$$

$R_a$  must be chosen as  $200k\Omega$  to maintain loop gain. Then  $R_b$  is given as:

$$R_b = \frac{1.206 \times 10^5}{V_{OUT} - 0.603} \Omega$$

$V_{\mbox{\tiny OUT}}$  can programmed over the range of 0.603V to  $V_{\mbox{\tiny IN}}\mbox{-}0.4V.$

#### **Dynamically Adjustable Output**

The EP5368QI is designed to allow for dynamic switching between the predefined VID voltage levels. The inter-voltage slew rate is optimized to prevent excess undershoot or overshoot as the output voltage levels transition. The slew rate is identical to the soft-start slew rate and is provided in the electrical characteristics table.

Dynamic transitioning between internal VID settings and the external divider is not allowed.

#### **Input and Output Capacitors**

The **input** capacitance requirement is 4.7uF 0603 MLCC. The input capacitor must be a X5R/X7R MLCC. Y5V or equivalent dielectric formulations lose capacitance with frequency, bias, and with temperature, and are not suitable for switch-mode DC-DC converter input filter applications.

The **output** capacitance requirement is approximately 20uF. Altera recommends a single 22uF 0805 MLCC. Ripple performance can be improved by using 2 x 10uF 0805 MLC capacitors.

As described in the Soft Start section, there is a limitation on the maximum bulk capacitance that can be placed on the output of this device. Please refer to that section for more details.

The output capacitor must be a X5R/X7R or equivalent MLCC. Y5V or equivalent dielectric formulations lose capacitance with frequency, bias, and temperature and are not suitable for switch-mode DC-DC converter output filter applications.

Please consult Power Applications support for other capacitor case size combinations.

### Operation at 700mA Output Current

Operation at 700mA is supported by using the application circuit shown in Figure 6. The modification in the compensation is to ensure stability over the entire set of input and output voltage conditions.

Figure 6: Applications Circuit for Operation at 700mA

For 700mA operation, use the following component values:

- 1)  $R_a = 249k\Omega$

- 2)  $C_a = 15pF 0402 MLCC$  capacitor.

- 3) Then R<sub>b</sub> is given as:

$$R_b = \frac{1.501x10^5}{V_{OUT} - 0.603} \Omega$$

$V_{\mbox{\tiny OUT}}$  can be programmed over the range of 0.603V to  $V_{\mbox{\tiny IN}}\mbox{-}0.4V.$

4) Do not connect the sense line.

**NOTE:** Stability cannot be assured if these guidelines are not followed.

### Layout Recommendation

Figure 7 shows critical components and layer 1 traces of a recommended minimum footprint EP5368QI layout. ENABLE configurations and other small signal pins need to be connected and routed according to specific customer application. Please see the Gerber files on the Altera website <a href="www.altera.com/enpirion">www.altera.com/enpirion</a> for exact dimensions and other layers. Please refer to Figure 7 while reading the layout recommendations in this section.

Recommendation 1: Input and output filter capacitors should be placed on the same side of the PCB, and as close to the EP5368QI package as possible. They should be connected to the device with very short and wide traces. Do not use thermal reliefs or spokes when connecting the capacitor pads to the respective nodes. The +V and GND traces between the capacitors and the EP5368QI should be as close to each other as possible so that the gap between the two nodes is minimized, even under the capacitors.

**Recommendation 2:** Input and output grounds are separated until they connect at the PGND pins. The separation shown on Figure 7 between the input and output GND circuits helps minimize noise coupling between the converter input and output switching loops.

**Recommendation 3:** The system ground plane should be the first layer immediately below the surface layer. This ground plane should be continuous and un-interrupted below the converter and the input/output capacitors. Please see the Gerber files on the Altera website www.altera.com/enpirion.

Figure 7: Top PCB Layer Critical Components and Copper for Minimum Footprint

Recommendation **4**: Multiple small should be used to connect the ground traces under the device to the system ground plane on another layer for heat dissipation. The drill diameter of the vias should be 0.33mm, and the vias must have at least 1 oz. copper plating on the inside wall, making the finished hole size around 0.20-0.26mm. Do not use thermal reliefs or spokes to connect the vias to the ground plane. It is preferred to put these vias under the capacitors along the edge of the GND copper closest to the +V copper. Please Figure 7. These vias connect the input/output filter capacitors to the GND plane and help reduce parasitic inductances in the input and output current loops. If the vias cannot be placed under C<sub>IN</sub> and C<sub>OUT</sub>, then put them just outside the capacitors along the GND. Do not use thermal reliefs or spokes to connect these vias to the ground plane.

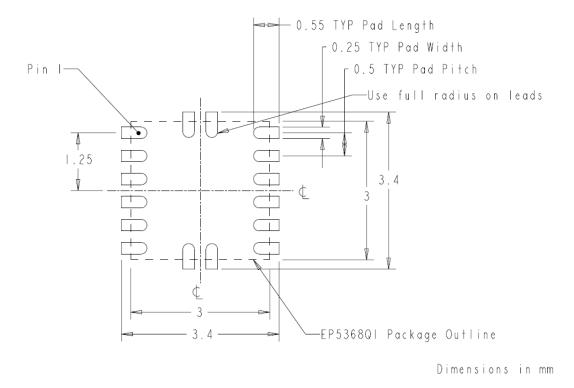

# Recommended PCB Footprint

Figure 8: EP5368QI Package PCB Footprint

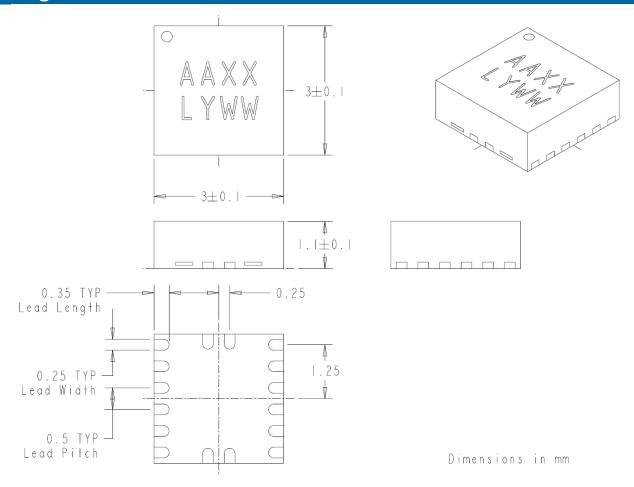

### **Package Dimensions**

Figure 9: EP5368QI Package Dimensions

**NOTE:** for details on product marking, please refer to the product marking guide which can be found at www.altera.com/support/reliability/packing/rel-packing-and-marking.html.

#### **Contact Information**

Altera Corporation 101 Innovation Drive San Jose, CA 95134 Phone: 408-544-7000 www.altera.com

© 2013 Altera Corporation—Confidential. All rights reserved. ALTERA, ARRIA, CYCLONE, ENPIRION, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Altera: EP5368QI