# EZ-USB<sup>®</sup> CX3: MIPI CSI-2 to SuperSpeed USB Bridge Controller

#### **Features**

- Universal Serial Bus (USB) integration

- □ USB 3.0 and USB 2.0 peripherals, compliant with USB 3.0 specification 1.0

- □ 5-Gbps USB 3.0 PHY compliant with PIPE 3.0

- □ Thirty-two physical endpoints

- MIPI CSI-2 RX interface

- ☐ MIPI CSI-2 compliant (Version 1.01, Revision 0.04 2<sup>nd</sup> April 2009)

- □ Supports up to four data lanes (CYUSB3065 supports up to four lanes; CYUSB3064 supports up to two lanes)

- □ Each lane supports up to 1 Gbps (CYUSB3065 supports up to four lanes; CYUSB3064 supports up to two lanes)

- CCI interface for image sensor configuration

- Supports the following video data formats:

- □ User-defined 8-bit

- □ RAW8/10/12/14

- □ YUV422 (CCIR/ITU 8/10bit), YUV444

- □ RGB888/666/565

- Fully accessible 32-bit CPU

- □ ARM926EJ-S core with 200-MHz operation

- □ 512-KB or 256-KB embedded SRAM

- Additional connectivity to the following peripherals:

- □ I<sup>2</sup>C master controller at 1 MHz

- □ I<sup>2</sup>S master (transmitter only) at sampling frequencies of 32 kHz, 44.1 kHz, and 48 kHz

- □ UART support of up to 4 Mbps

- □ SPI master at 33 MHz

- Twelve GPIOs

- Ultra-low-power in core power-down mode

- Independent power domains for core and I/O

- □ Core operation at 1.2 V

- □ I<sup>2</sup>S, UART, and SPI operation at 1.8 to 3.3 V

- □ I<sup>2</sup>C, I/O operation at 1.8 to 3.3 V

- 10 × 10 mm, 0.8-mm pitch Pb-free ball grid array (BGA) package

- EZ-USB<sup>®</sup> software development kit (SDK) for easy code development

# **Applications**

- Digital video cameras

- Digital still cameras

- Webcams

- Scanners

- Video conference systems

- Gesture-based control

- Surveillance cameras

- Medical imaging devices

- Video IP phones

- USB microscopes

- Industrial cameras

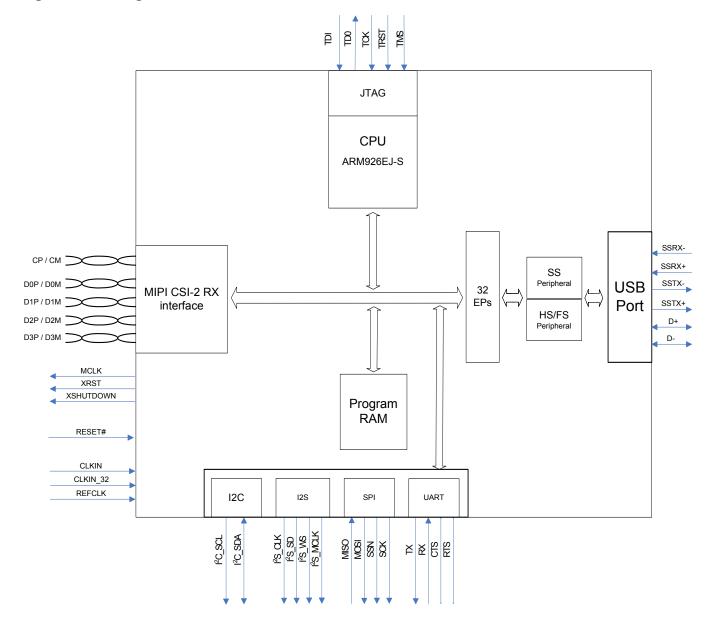

# **Logic Block Diagram**

#### More Information

Cypress provides a wealth of data at <a href="https://www.cypress.com">www.cypress.com</a> to help you to select the right device for your design, and to help you to quickly and effectively integrate the device into your design. For a comprehensive list of resources refer to the cypress web page for CX3 at <a href="https://www.cypress.com/CX3">www.cypress.com/CX3</a>.

- Overview: USB Portfolio, USB Roadmap

- USB 3.0 Product Selectors: FX3, FX3S, CX3, GX3, HX3, West Bridge Benicia

- Application notes: Cypress offers a large number of USB application notes covering a broad range of topics, from basic to advanced level. Recommended application notes for getting started with CX3 are:

- □ AN75705 Getting Started with EZ-USB FX3

- □ AN90369 How to Interface a MIPI CSI-2 Image Sensor With EZ-USB® CX3

- □ AN75779 How to Implement an Image Sensor Interface with EZ-USB® FX3™ in a USB Video Class (UVC) Framework

- □ AN76405 EZ-USB FX3 Boot Options

- □ AN70707 EZ-USB FX3/FX3S Hardware Design Guidelines and Schematic Checklist

- □ AN86947 Optimizing USB 3.0 Throughput with EZ-USB FX3

- Code Examples:

- USB SuperSpeed

- Technical Reference Manual (TRM):

- □ EZ-USB® CX3 Technical Reference Manual

#### ■ Knowledge Base Articles:

- CX3 Firmware: Frequently Asked Questions KBA91297

- □ CX3 Hardware: Frequently Asked Questions KBA91295

- CX3 Application Software / USB Driver: Frequently Asked Questions - KBA91298

- □ Knowledge Base Cypress Semiconductor Cage Code -KBA89258

#### ■ Development Kits:

- □ Ascella Cypress® CX3™ THine® ISP 13MP reference design kit (RDK)

- □ Denebola USB 3.0 UVC Reference Design Kit (RDK)

#### ■ Models

- □ CX3 Device OrCad Schematic Symbol

- □ CYUSB306x IBIS

# **EZ-USB Software Development Kit**

Cypress delivers the complete firmware stack for CX3, in order to easily integrate SuperSpeed USB into any embedded MIPI image sensor application. The Software Development Kit (FX3 SDK) comes with tools, drivers and application examples, which help accelerate application development. The FX3 SDK Setup includes CX3 APIs and example firmware for OmniVision OV5640 and Aptina AS0260 image sensor interface. The eclipse plugin for the FX3 SDK accelerates CX3 firmware development for any other image sensor.

# Contents

| Functional Overview               | J  |

|-----------------------------------|----|

| Application Examples              | 5  |

| USB Interface                     | 6  |

| ReNumeration                      | 6  |

| VBUS Overvoltage Protection       | 6  |

| MIPI CSI-2 RX Interface           | 7  |

| Additional Outputs                | 7  |

| CPU                               | 7  |

| JTAG Interface                    |    |

| Other Interfaces                  | 7  |

| UART Interface                    | 7  |

| I2C Interface                     | 7  |

| I2S Interface                     | 8  |

| SPI Interface                     | 8  |

| Boot Options                      | 8  |

| Reset                             | 8  |

| Hard Reset                        | 8  |

| Soft Reset                        |    |

| Clocking                          | 9  |

| 32-kHz Watchdog Timer Clock Input | 9  |

| Power                             | 10 |

| Power Modes                       | 10 |

| Configuration Options             | 13 |

| Digital I/Os                      | 13 |

| GPIOs                             | 13 |

| EMI                               | 13 |

| System-level ESD                  | 13 |

| Pin Configuration                              | 14 |

|------------------------------------------------|----|

| Pin Description                                | 15 |

| Absolute Maximum Ratings                       |    |

| Operating Conditions                           |    |

| DC Specifications                              |    |

| MIPI D-PHY Electrical Characteristics          |    |

| AC Timing Parameters                           | 19 |

| MIPI Data to Clock Timing Reference            | 19 |

| Reference Clock Specifications                 |    |

| MIPI CSI Signal Low Power AC Characteristics . | 20 |

| AC Specifications                              |    |

| Serial Peripherals Timing                      | 21 |

| Reset Sequence                                 | 26 |

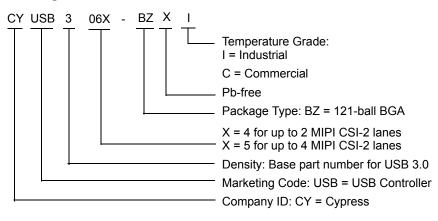

| Ordering Information                           | 27 |

| Ordering Code Definitions                      | 27 |

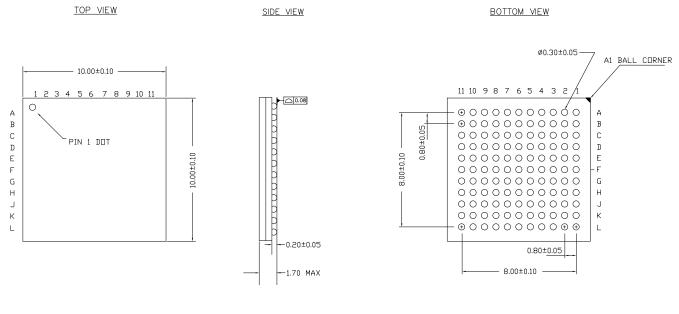

| Package Diagram                                |    |

| Acronyms                                       | 29 |

| Document Conventions                           | 29 |

| Units of Measure                               | 29 |

| Document History Page                          | 30 |

| Sales, Solutions, and Legal Information        | 32 |

| Worldwide Sales and Design Support             | 32 |

| Products                                       | 32 |

| PSoC®Solutions                                 |    |

| Cypress Developer Community                    | 32 |

| Technical Support                              |    |

#### **Functional Overview**

Cypress's EZ-USB CX3 is the next-generation bridge controller that can connect devices with the Mobile Industry Processor Interface – Camera Serial Interface 2 (MIPI CSI-2) interface to any USB 3.0 Host.

CX3 has a 4-lane CSI-2 receiver with up to 1 Gbps on each lane. It supports video data formats such as RAW8/10/12/14, YUV422 (CCIR/ITU 8/10-bit), RGB888/666/565, and user-defined 8-bit.

CX3 has integrated the USB 3.0 and USB 2.0 physical layers (PHYs) along with a 32-bit ARM926EJ-S microprocessor for powerful data processing and for building custom applications.

CX3 contains 512 KB of on-chip SRAM (see Ordering Information on page 27) for code and data. EZ-USB CX3 also provides interfaces to connect to serial peripherals such as UART, SPI, I<sup>2</sup>C, and I<sup>2</sup>S.

CX3 comes with application development tools. The software development kit comes with application examples for accelerating time-to-market.

CX3 complies with the USB 3.0 v1.0 specification and is also backward compatible with USB 2.0. It also complies with the MIPI CSI-2 v1.01, revision 0.04 specification dated 2<sup>nd</sup> April 2009.

#### **Application Examples**

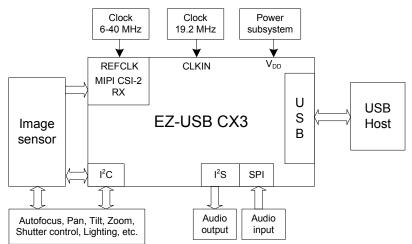

In a typical application (see Figure 1), CX3 acts as the main processor and connects to an image sensor, an audio device, or camera control devices amongst others.

Figure 1. EZ-USB CX3 Example Application

#### **USB** Interface

CX3 complies with the following specifications and supports the following features:

- Supports USB peripheral functionality compliant with USB 3.0 Specification, Revision 1.0, and is also backward compatible with the USB 2.0 Specification.

- As a peripheral, CX3 is capable of SuperSpeed, High-Speed, and Full-Speed.

- Supports up to 16 IN and 16 OUT endpoints

- Supports the USB 3.0 Streams feature

- As a USB peripheral, CX3 supports USB-attached storage (UAS), USB Video Class (UVC), and Media Transfer Protocol (MTP) USB peripheral classes. As a USB peripheral, all other device classes are supported only in pass-through mode when handled entirely by a host processor external to the device.

Figure 2. USB Interface Signals

# ReNumeration

Because of CX3's soft configuration, one chip can take on the identities of multiple distinct USB devices.

When first plugged into USB, CX3 enumerates automatically with the Cypress Vendor ID (0x04B4) and downloads the firmware and USB descriptors over the USB interface. The downloaded firmware executes an electrical disconnect and connect. CX3 enumerates again, this time as a device defined by the downloaded information. This patented two-step process, called ReNumeration, happens instantly when the device is plugged in.

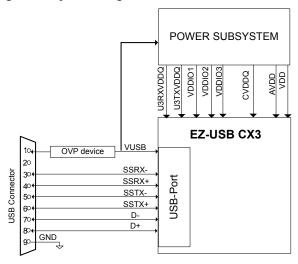

# **VBUS Overvoltage Protection**

The maximum input voltage on CX3's VUSB pin is 6 V. A charger can supply up to 9 V on VUSB. In this case, an external overvoltage protection (OVP) device is required to protect CX3 from damage on VUSB. Figure 3 shows the system application diagram with an OVP device connected on VUSB. Refer to DC Specifications on page 17 for the operating range of VUSB.

**Note:** The VBUS pin of the USB connector should be connected to the VUSB pin of CX3.

Figure 3. System Diagram with OVP Device For VUSB

# MIPI CSI-2 RX Interface

The Mobile Industry Processor Interface (MIPI) association defined the Camera Serial Interface 2 (CSI-2) standard to enable image data to be sent on high-bandwidth serial lines.

CX3 implements a MIPI CSI-2 Receiver with the following features:

- It can receive clock and data in 1, 2, 3, or 4 lanes. (CYUSB3065 part supports up to four lanes; CYUSB3064 part supports up to two lanes)

- 2. Up to 1 Gbps of data on each CSI lane is supported (total maximum bandwidth should not exceed 2.4 Gbps).

- Video formats such as RAW8/10/12/14, YUV422 (CCIR/ITU 8/10-bit), RGB888/666/565, and User-Defined 8-bit are supported

- A CCI interface (compatible with 100-kHz or 400-kHz I<sup>2</sup>C interface with 7-bit addressing) is provided to configure the sensor.

- GPIOs are available for synchronization of external flash or lighting system with image sensors to illuminate the scene that improves the image quality by improving Signal to noise ratio.

- GPIOs can also be used to synchronize the image sensor with external events, so that image can be captured based on external event.

- Serial interfaces (such as I<sup>2</sup>C, I<sup>2</sup>S, SPI, UART) are available to implement camera functions such as Auto focus and Pan, Tilt, Zoom (PTZ)

#### **Additional Outputs**

In addition to the standard MIPI CSI-2 signals, the following three additional outputs are provided:

- 1. XRST: this can be used to reset the image sensor

- XSHUTDOWN: this pin can be used to put the sensor to a standby/shutdown mode

- MCLK: this pin can provide the clock output. It can be used only for testing the image sensor. For production, use an external clock generator as clock input for image sensors.

# **CPU**

CX3 has an on-chip 32-bit, 200-MHz ARM926EJ-S core CPU. The core has direct access to 16 kB of Instruction Tightly Coupled Memory (TCM) and 8 kB of data TCM. The ARM926EJ-S core provides a JTAG interface for firmware debugging.

CX3 offers the following advantages:

- Integrates 512 KB of embedded SRAM for code and data and 8 kB of instruction cache and data cache.

- Implements efficient and flexible DMA connectivity between the various peripherals (such as, USB, CSI-2 Rx, I<sup>2</sup>S, SPI, and UART), requiring firmware only to configure data accesses between peripherals, which are then managed by the DMA fabric.

- Allows easy application development on industry-standard development tools for ARM926EJ-S.

Examples of the CX3 firmware are available with the Cypress EZ-USB CX3 Development Kit. Software APIs that can be ported to an external processor are available with the Cypress EZ-USB CX3 Software Development Kit.

# JTAG Interface

CX3's JTAG interface has a standard five-pin interface to connect to a JTAG debugger in order to debug firmware through the CPU-core's on-chip-debug circuitry.

Industry-standard debugging tools for the ARM926EJ-S core can be used for the CX3 application development.

# **Other Interfaces**

CX3 supports the following serial peripherals:

- **■** UART

- I<sup>2</sup>C

- I<sup>2</sup>S

- SPI

The CYUSB306X Pin List on page 15 shows the details of how these interfaces are mapped.

#### **UART Interface**

The UART interface of CX3 supports full-duplex communication. It includes the signals noted in Table 1.

**Table 1. UART Interface Signals**

| Signal | Description   |

|--------|---------------|

| TX     | Output signal |

| RX     | Input signal  |

| CTS    | Flow control  |

| RTS    | Flow control  |

The UART is capable of generating a range of baud rates, from 300 bps to 4608 Kbps, selectable by the firmware. If flow control is enabled, then CX3's UART only transmits data when the CTS input is asserted. In addition to this, CX3's UART asserts the RTS output signal, when it is ready to receive data.

#### I<sup>2</sup>C Interface

CX3's I<sup>2</sup>C interface is compatible with the I<sup>2</sup>C Bus Specification Revision 3. This I<sup>2</sup>C interface is capable of operating only as I<sup>2</sup>C master; therefore, it may be used to communicate with other I<sup>2</sup>C slave devices. For example, CX3 may boot from an EEPROM connected to the I<sup>2</sup>C interface, as a selectable boot option.

CX3's I<sup>2</sup>C Master Controller also supports multi-master mode functionality.

The power supply for the  $\rm I^2C$  interface is  $\rm V_{DDIO1}$ , which is a separate power domain from the other serial peripherals. This gives the  $\rm I^2C$  interface the flexibility to operate at a different voltage than the other serial interfaces.

The  $\rm I^2C$  controller supports bus frequencies of 400 kHz, and 1 MHz. When  $\rm V_{DDIO1}$  is 1.8 V, 2.5 V, or 3.3 V, the operating frequencies supported are 400 kHz and 1 MHz. The  $\rm I^2C$  controller supports the clock-stretching feature to enable slower devices to exercise flow control.

The  $I^2$ C interface's SCL and SDA signals require external pull-up resistors. The pull-up resistors must be connected to  $V_{DDIO1}$ .

**Note:** I<sup>2</sup>C addresses with the pattern 0x0000111x are used internally and no slave devices with those addresses should be connected to the bus.

# I<sup>2</sup>S Interface

CX3 has an I<sup>2</sup>S port to support external audio codec devices. CX3 functions as I<sup>2</sup>S Master as transmitter only. The I<sup>2</sup>S interface consists of four signals: clock line (I2S\_CLK), serial data line (I2S\_SD), word select line (I2S\_WS), and master system clock (I2S\_MCLK). CX3 can generate the system clock as an output on I2S\_MCLK or accept an external system clock input on I2S MCLK.

The sampling frequencies supported by the I<sup>2</sup>S interface are 32 kHz, 44.1 kHz, and 48 kHz.

#### **SPI Interface**

CX3 supports an SPI Master interface on the Serial Peripherals port. The maximum operation frequency is 33 MHz.

The SPI controller supports four modes of SPI communication (see SPI Timing Specification on page 24 for details on the modes) with the Start-Stop clock. This controller is a single-master controller with a single automated SSN control. It supports transaction sizes ranging from 4 bits to 32 bits.

# **Boot Options**

CX3 can load boot images from various sources, selected by the configuration of the PMODE pins. Following are the CX3 boot options:

- Boot from USB

- Boot from I<sup>2</sup>C

- Boot from SPI (SPI devices supported are M25P16 (16 Mbit), M25P80 (8 Mbit), and M25P40 (4 Mbit)) or their equivalents

Table 2. CX3 Booting Options

| PMODE[2:0] <sup>[1]</sup> | Boot From                                         |

|---------------------------|---------------------------------------------------|

| F11                       | USB boot                                          |

| F1F                       | I <sup>2</sup> C, On failure, USB boot is enabled |

| 1FF                       | I <sup>2</sup> C only                             |

| 0F1                       | SPI, On failure, USB boot is enabled              |

#### Reset

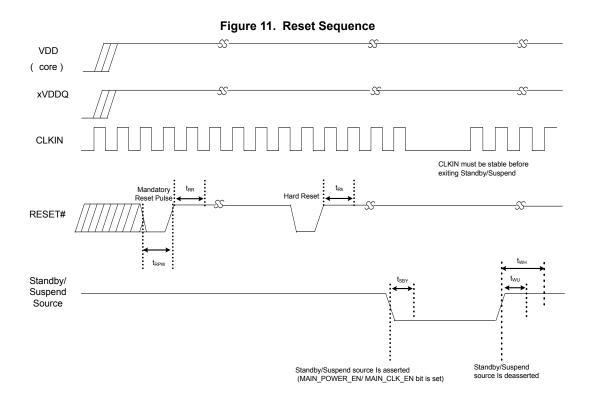

#### **Hard Reset**

A hard reset is initiated by asserting the RESET# pin on CX3. The specific reset sequence and timing requirements are detailed in Figure 11 on page 26 and Table 14 on page 26. All I/Os are tristated during a hard reset.

An additional reset pin called MIPI\_RESET is provided that resets the MIPI CSI-2 core. It should be pulled down with a resistor for normal operation.

#### **Soft Reset**

There are two types of Soft Reset:

- CPU Reset The CPU Program Counter is reset. Firmware does not need to be reloaded following a CPU Reset.

- Whole Device Reset This reset is identical to Hard Reset. The firmware must be reloaded following a Whole Device Reset.

1. F indicates Floating.

# Clocking

CX3 requires two clocks for normal operation:

- 1. A 19.2-MHz clock to be connected at the CLKIN pin

- 2. A 6-MHz to 40-MHz clock to be connected at the REFCLK pin Clock inputs to CX3 must meet the phase noise and jitter requirements specified in Table 3 on page 9.

Table 3. CX3 Input Clock Specifications

The input clock frequency is independent of the clock and data rate of the CX3 core or any of the device interfaces (including the CSI-2 Rx Port). The internal PLL applies the appropriate clock-multiply option depending on the input frequency.

**Note:** REFCLK and CLKIN must have either separate clock inputs or if the same source is used, the clock must be passed through a buffer with two outputs and then connected to the clock pins

| Parameter                   | Description    | Specifi | Units       |        |  |

|-----------------------------|----------------|---------|-------------|--------|--|

| Farameter                   | Description    | Min     | Max         | Office |  |

|                             | 100-Hz offset  | -       | <b>–</b> 75 | dB     |  |

|                             | 1-kHz offset   | _       | -104        | dB     |  |

| Phase noise                 | 10-kHz offset  | _       | -120        | dB     |  |

|                             | 100-kHz offset | -       | -128        | dB     |  |

|                             | 1-MHz offset   | _       | -130        | dB     |  |

| Maximum frequency deviation | -              | _       | 150         | ppm    |  |

| Duty cycle                  | -              | 30      | 70          | %      |  |

| Overshoot                   | _              | _       | 3           | %      |  |

| Undershoot                  | _              | _       | -3          | %      |  |

| Rise time/fall time         | _              | _       | 3           | ns     |  |

# 32-kHz Watchdog Timer Clock Input

CX3 includes a watchdog timer. The watchdog timer can be used to interrupt the ARM926EJ-S core, automatically wake up the CX3 in Standby mode, and reset the ARM926EJ-S core. The watchdog timer runs a 32-kHz clock, which may be optionally supplied from an external source on a dedicated CX3 pin.

The firmware can disable the watchdog timer.

Table 4 provides the requirements for the optional 32-kHz clock input

Table 4. 32-kHz Clock Input Requirements

| Parameter           | Min | Max  | Units |

|---------------------|-----|------|-------|

| Duty cycle          | 40  | 60   | %     |

| Frequency deviation | _   | ±200 | ppm   |

| Rise time/fall time | _   | 200  | ns    |

Document Number: 001-87516 Rev. \*K

#### **Power**

CX3 has the following power supply domains:

- IO\_VDDQ: This is a group of independent supply domains for digital I/Os.

- $\hfill\Box \mbox{ $V_{DDIO1}$: GPIO, $I^2$C, JTAG, XRST, XSHUTDOWN and REFCLK$

- □ V<sub>DDIO2</sub>: UART and I<sup>2</sup>S (except MCLK)

- □ V<sub>DDIO3</sub>: I<sup>2</sup>S\_MCLK and SPI

- □ C<sub>VDDQ</sub>: CLKIN

- □ V<sub>DD MIPI</sub>: MIPI CSI-2 clock and data lanes

- V<sub>DD</sub>: This is the supply voltage for the logic core. The nominal supply-voltage level is 1.2 V. This supplies the core logic circuits. The same supply must also be used for the following:

- □ A<sub>VDD</sub>: This is the 1.2-V supply for the PLL, crystal oscillator, and other core analog circuits.

- □ U3TXVDDQ/U3RXVDDQ: These are the 1.2-V supply voltages for the USB 3.0 interface.

- VUSB: This is the 3.2-V to 6-V battery power supply for the USB I/O and analog circuits. This supply powers the USB transceiver through CX3's internal voltage regulator. VUSB is internally regulated to 3.3 V.

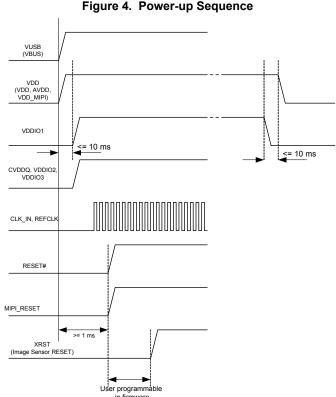

Note: The different power supplies have to be powered on or off in a specific sequence as illustrated in Figure 4.

#### **Power Modes**

CX3 supports the following power modes:

- Normal mode: This is the full-functional operating mode. The internal CPU clock and the internal PLLs are enabled in this mode.

- □ Normal operating power consumption does not exceed the sum of  $I_{CC}$  Core max and  $I_{CC}$  USB max (see DC Specifications on page 17 for current consumption specifications).

- $\hfill\Box$  The I/O power supplies  $V_{DDIO2}$  and  $V_{DDIO3}$  can be turned off when the corresponding interface is not in use.  $V_{DDIO1}$  should never be turned off for normal operation.

- Low-power modes (see Table 5 on page 11):

- □ Suspend mode with USB 3.0 PHY enabled

- □ Standby mode

- □ Core power-down mode

Table 5. Entry and Exit Methods for Low-Power Modes

| Low-Power Mode                | Characteristics                                                                                                                                                                                                                                                                                      | Methods of Entry                                                                                                                        | Methods of Exit                                              |

|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

|                               | ■ Power consumption in this mode does not exceed I <sub>SB1</sub>                                                                                                                                                                                                                                    |                                                                                                                                         |                                                              |

|                               | ■ USB 3.0 PHY is enabled and is in U3 mode (one of the suspend modes defined by the USB 3.0 specification). This one block alone is operational with its internal clock, while all other clocks are shut down                                                                                        |                                                                                                                                         | ■ D+ transitioning to low or high                            |

|                               | ■ All I/Os maintain their previous state                                                                                                                                                                                                                                                             |                                                                                                                                         | ■ D- transitioning to low                                    |

| Suspend Mode with USB 3.0 PHY | ■ Power supply for the wakeup source and core power must be retained. All other power domains can be turned on or off individually                                                                                                                                                                   | ■ Firmware executing on<br>ARM926EJ-S core can put CX3 into<br>the suspend mode. For example, on<br>USB suspend condition, the firmware | or high ■ Resume condition on SSRX±                          |

| Enabled                       | ■ The states of the configuration registers, buffer memory, and all internal RAM are maintained                                                                                                                                                                                                      | may decide to put CX3 into suspend mode                                                                                                 | ■ Detection of VBUS ■ Level detect on UART_CTS (programmable |

|                               | ■ All transactions must be completed before CX3 enters suspend mode (state of outstanding transactions are not preserved)                                                                                                                                                                            |                                                                                                                                         | polarity)  Assertion of RESET#                               |

|                               | ■ The firmware resumes operation from where it was suspended (except when woken up by RESET# assertion) because the program counter does not reset                                                                                                                                                   |                                                                                                                                         |                                                              |

|                               | ■ The power consumption in this mode does not exceed ISB3                                                                                                                                                                                                                                            |                                                                                                                                         |                                                              |

|                               | ■ All configuration register settings and program/data RAM contents are preserved. However, data in the buffers or other parts of the data path, if any, is not guaranteed. Therefore, the external processor should take care that the data needed is read before putting CX3 into the standby mode |                                                                                                                                         | ■ Detection of VBUS                                          |

|                               | ■ The program counter is reset after waking                                                                                                                                                                                                                                                          | ■ The firmware executing on                                                                                                             | ■ Level detect on                                            |

| Standby Mode                  | up from the standby mode  GPIO pins maintain their configuration                                                                                                                                                                                                                                     | ARM926EJ-S core or external processor configures the appropriate                                                                        | UART_CTS<br>(programmable                                    |

|                               | ■ Internal PLL is turned off                                                                                                                                                                                                                                                                         | register                                                                                                                                | polarity)                                                    |

|                               | ■ USB transceiver is turned off                                                                                                                                                                                                                                                                      |                                                                                                                                         | ■ Assertion of RESET#                                        |

|                               | ■ ARM926EJ-S core is powered down. Upon wakeup, the core re-starts and runs the program stored in the program/data RAM                                                                                                                                                                               |                                                                                                                                         |                                                              |

|                               | ■ Power supply for the wakeup source and core power must be retained. All other power domains can be turned on or off individually                                                                                                                                                                   |                                                                                                                                         |                                                              |

Table 5. Entry and Exit Methods for Low-Power Modes (continued)

| Low-Power Mode          | Characteristics                                                                                                                       | Methods of Entry           | Methods of Exit                                                          |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------|----------------------------|--------------------------------------------------------------------------|

|                         | ■ The power consumption in this mode does not exceed ISB <sub>4</sub>                                                                 |                            |                                                                          |

|                         | ■ Core power is turned off                                                                                                            |                            |                                                                          |

| Core Power-down<br>Mode | ■ All buffer memory, configuration registers, and the program RAM do not maintain state. After exiting this mode, reload the firmware | ■ Turn off V <sub>DD</sub> | <ul><li>■ Reapply V<sub>DD</sub></li><li>■ Assertion of RESET#</li></ul> |

|                         | ■ In this mode, all other power domains can be turned on or off individually                                                          |                            |                                                                          |

# **Configuration Options**

Configuration options are available for specific usage models. Contact Cypress Marketing (usb3@cypress.com) for details.

# Digital I/Os

CX3 has internal firmware-controlled pull-up or pull-down resistors on all digital I/O pins. An internal  $50-k\Omega$  resistor pulls the pins high, while an internal  $10-k\Omega$  resistor pulls the pins low to prevent them from floating. The I/O pins may have the following states:

- Tristated (High-Z)

- Weak pull-up (via internal 50 k $\Omega$ )

- Pull-down (via internal 10 kΩ)

- Hold (I/O hold its value) when in low-power modes

- The JTAG TDI, TMC, and TRST# signals have fixed 50-k $\Omega$  internal pull-ups, and the TCK signal has a fixed 10-k $\Omega$  pull-down resistor.

All unused I/Os should be pulled high by using the internal pull-up resistors. All unused outputs should be left floating. All I/Os can be driven at full-strength, three-quarter strength, half-strength, or quarter-strength. These drive strengths are configured separately for each interface.

# **GPIOs**

CX3 provides 12 pins for general purpose I/O (for example, can be used for lighting, sync-in, sync-out and so on). See Pin Configuration on page 14 for pinout details.

All GPIO pins support an external load of up to 16 pF for every pin.

# **EMI**

CX3 can meet EMI requirements outlined by FCC 15B (USA) and EN55022 (Europe) for consumer electronics at system level. CX3 can tolerate reasonable EMI, conducted by the aggressor, outlined by these specifications and continue to function as expected.

# System-level ESD

CX3 has built-in ESD protection on the D+, D-, and GND pins on the USB interface. The ESD protection levels provided on these ports are:

- ±2.2-kV human body model (HBM) based on JESD22-A114 specification

- ±6-kV contact discharge and ±8-kV air gap discharge based on IEC61000-4-2 level 3A using external system-level protection devices

- ± 8-kV contact discharge and ±15-kV air gap discharge based on IEC61000-4-2 level 4C using external system-level protection devices

This protection ensures that the device continues to function after ESD events up to the levels stated in this section.

The SSRX+, SSRX-, SSTX+, and SSTX- pins only have up to ±2.2-kV HBM internal ESD protection.

# **Pin Configuration**

Figure 5. CX3 Ball Map (Top View)

| A1                     | A2                     | А3                   | A4                     | A5                     | A6                    | <b>A</b> 7 | A8                       | A9                       | A10     | A11                    |

|------------------------|------------------------|----------------------|------------------------|------------------------|-----------------------|------------|--------------------------|--------------------------|---------|------------------------|

| U3VSSQ                 | U3RXVDDQ               | SSRXM                | SSRXP                  | SSTXP                  | SSTXM                 | AVDD       | VSS                      | DP                       | DM      | GPIO[24]               |

| B1                     | B2                     | В3                   | B4                     | B5                     | В6                    | В7         | B8                       | В9                       | B10     | B11                    |

| VDDIO3                 | VSS                    | GPIO[23]             | GPIO[21]               | U3TXVDDQ               | CVDDQ                 | AVSS       | VSS                      | VSS                      | VDD     | TRST#                  |

| C1                     | C2                     | C3                   | C4                     | C5                     | C6                    | C7         | C8                       | C9                       | C10     | C11                    |

| SPI_SSN /<br>GPIO[54]  | SPI_MISO /<br>GPIO[55] | VDD                  | GPIO[26]               | RESET#                 | GPIO[18]              | GPIO[19]   | GPIO[22]                 | GPIO[45]                 | TDO     | 12S_MCLK<br>/ GPIO[57] |

| D1                     | D2                     | D3                   | D4                     | D5                     | D6                    | D7         | D8                       | D9                       | D10     | D11                    |

| I2S_CLK /<br>GPIO[50]  | I2S_SD /<br>GPIO[51]   | I2S_WS /<br>GPIO[52] | SPI_SCK /<br>GPIO[53]  | SPI_MOSI /<br>GPIO[56] | CLKIN_32              | CLKIN      | VSS                      | I2C_SCL                  | I2C_SDA | GPIO[17]               |

| E1                     | E2                     | E3                   | E4                     | E5                     | E6                    | E7         | E8                       | E9                       | E10     | E11                    |

| UART_CTS /<br>GPIO[47] | VSS                    | VDDIO2               | UART_RX /<br>GPIO[49]  | UART_TX /<br>GPIO[48]  | GPIO[20]              | TDI        | TMS                      | VDD                      | VUSB    | VSS                    |

| F1                     | F2                     | F3                   | F4                     | F5                     | F6                    | F7         | F8                       | F9                       | F10     | F11                    |

| DNU                    | REFCLK                 | GPIO[44]             | XRST                   | UART_RTS /<br>GPIO[46] | TCK                   | DNU        | DNU                      | DNU                      | DNU     | VDD                    |

| G1                     | G2                     | G3                   | G4                     | G5                     | G6                    | G7         | G8                       | G9                       | G10     | G11                    |

| VSS                    | XSHUTDOW<br>N          | MCLK                 | PMODE[0] /<br>GPIO[30] | GPIO[25]               | HSYNC_test            | DNU        | DNU                      | DNU                      | DNU     | VSS                    |

| H1                     | H2                     | Н3                   | H4                     | H5                     | Н6                    | H7         | H8                       | Н9                       | H10     | H11                    |

| VDD                    | DNU                    | DNU                  | PMODE[1] /<br>GPIO[31] | VSYNC_test             | MIPI RESET            | DNU        | PCLK_test                | DNU                      | DNU     | VDDIO1                 |

| J1                     | J2                     | J3                   | J4                     | J5                     | J6                    | J7         | J8                       | J9                       | J10     | J11                    |

| DNU                    | DNU                    | DNU                  | DNU                    | MIPI_D0P               | MIPI_D1P <sup>1</sup> | MIPI_CP    | MIPI_D2P <sup>1, 2</sup> | MIPI_D2N <sup>1, 2</sup> | DNU     | VDD                    |

| K1                     | K2                     | K3                   | K4                     | K5                     | K6                    | K7         | K8                       | K9                       | K10     | K11                    |

| DNU                    | DNU                    | VSS                  | VSS                    | MIPI_D0N               | MIPI_D1N <sup>1</sup> | MIPI_CN    | MIPI_D3N <sup>1, 2</sup> | DNU                      | DNU     | DNU                    |

| L1                     | L2                     | L3                   | L4                     | L5                     | L6                    | L7         | L8                       | L9                       | L10     | L11                    |

| VSS                    | VSS                    | VSS                  | PMODE[2] /<br>GPIO[32] | VDD_MIPI               | VSS                   | VDD        | MIPI_D3P <sup>1, 2</sup> | VDDIO1                   | DNU     | VSS                    |

# Legend

Unused MIPI input data lanes to be connected to GND.

The signals MIPI\_D2N, MIPI\_D3N, and MIPI\_D3P are not available in the CYUSB3064 part. These pins should be left "open" in the customer board.

# **Pin Description**

Table 6. CYUSB306X Pin List

| СХЗ  |                     |     |  |  |

|------|---------------------|-----|--|--|

| Pin# | Pin name            | I/O |  |  |

| F10  | DNU                 | I/O |  |  |

| F9   | DNU                 | I/O |  |  |

| F7   | DNU                 | I/O |  |  |

| G10  | DNU                 | I/O |  |  |

| G9   | DNU                 | I/O |  |  |

| F8   | DNU                 | I/O |  |  |

| H10  | DNU                 | I/O |  |  |

| H9   | DNU                 | I/O |  |  |

| J10  | DNU                 | I/O |  |  |

| H7   | DNU                 | I/O |  |  |

| K11  | DNU                 | I/O |  |  |

| L10  | DNU                 | I/O |  |  |

| K10  | DNU                 | I/O |  |  |

| K9   | DNU                 | I/O |  |  |

| G7   | DNU                 | I/O |  |  |

| G8   | DNU                 | I/O |  |  |

| K2   | DNU                 | I/O |  |  |

| J4   | DNU                 | I/O |  |  |

| K1   | DNU                 | I/O |  |  |

| J2   | DNU                 | I/O |  |  |

| J3   | DNU                 | I/O |  |  |

| J1   | DNU                 | I/O |  |  |

| H2   | DNU                 | I/O |  |  |

| H3   | DNU                 | I/O |  |  |

| G6   | HSYNC_test          | I/O |  |  |

| H5   | VSYNC_test          | I/O |  |  |

| H8   | PCLK_test           | I/O |  |  |

|      | VDDIO1 Power Domain |     |  |  |

| D11  | GPIO[17]            | I/O |  |  |

| C6   | GPIO[18]            | I/O |  |  |

| C7   | GPIO[19]            | I/O |  |  |

| E6   | GPIO[20]            | I/O |  |  |

| B4   | GPIO[21]            | I/O |  |  |

| C8   | GPIO[22]            | I/O |  |  |

| В3   | GPIO[23]            | I/O |  |  |

| A11  | GPIO[24]            | I/O |  |  |

| G5   | GPIO[25]            | I/O |  |  |

Table 6. CYUSB306X Pin List (continued)

| CX3                          |                                            |     |  |  |  |

|------------------------------|--------------------------------------------|-----|--|--|--|

| Pin# Pin name I/O            |                                            |     |  |  |  |

| C4                           | GPIO[26]                                   | I/O |  |  |  |

| F3                           | GPIO[44]                                   | I/O |  |  |  |

| C9                           | GPIO[45]                                   | I/O |  |  |  |

| G4                           | PMODE[0] / GPIO[30]                        | I/O |  |  |  |

| H4                           | PMODE[1] / GPIO[31]                        | I/O |  |  |  |

| L4                           | PMODE[2] / GPIO[32]                        | I/O |  |  |  |

| F1                           | DNU                                        | I/O |  |  |  |

| H6                           | MIPI RESET                                 | I/O |  |  |  |

| C5                           | RESET#                                     | I   |  |  |  |

| F4                           | XRST                                       | 0   |  |  |  |

| G2                           | XSHUTDOWN                                  | 0   |  |  |  |

| G3                           | MCLK                                       | 0   |  |  |  |

|                              | VDDIO2 Power Domain                        | I   |  |  |  |

| F5                           | UART_RTS / GPIO[46]                        | I/O |  |  |  |

| E1                           | UART_CTS / GPIO[47]                        | I/O |  |  |  |

| E5                           | UART_TX / GPIO[48]                         | I/O |  |  |  |

| E4                           | UART_RX / GPIO[49]                         | I/O |  |  |  |

| D1                           | I2S_CLK / GPIO[50]                         | I/O |  |  |  |

| D2                           | I2S_SD / GPIO[51]                          | I/O |  |  |  |

| D3                           | D3   I2S_WS / GPI0[52]                     |     |  |  |  |

|                              | VDDIO3 Power Domain                        |     |  |  |  |

| D4                           | SPI_SCK / GPIO[53]                         | I/O |  |  |  |

| C1                           | SPI_SSN / GPIO[54]                         | I/O |  |  |  |

| C2                           | SPI_MISO / GPIO[55]                        | I/O |  |  |  |

| D5                           | SPI_MOSI / GPIO[56]                        | I/O |  |  |  |

| C11                          | I2S_MCLK / GPIO[57]                        | I/O |  |  |  |

| U                            | SB Port (U3TXVDDQ/U3RXVDI<br>Power Domain) | DQ  |  |  |  |

| A3                           | SSRXM                                      | I   |  |  |  |

| A4                           | SSRXP                                      | I   |  |  |  |

| A6                           | SSTXM                                      | 0   |  |  |  |

| A5                           | SSTXP                                      | 0   |  |  |  |

| USB Port (VUSB Power Domain) |                                            |     |  |  |  |

| A9                           | DP                                         | I/O |  |  |  |

| A10                          | DM                                         | I/O |  |  |  |

|                              | VDDIO1 Power Domain                        |     |  |  |  |

| F2                           | REFCLK                                     |     |  |  |  |

| VDD_MIPI Power Domain        |                                            |     |  |  |  |

| J7                           | MIPI_CP                                    | I   |  |  |  |

Document Number: 001-87516 Rev. \*K

Table 6. CYUSB306X Pin List (continued)

|      | CX3                      |     |  |  |  |

|------|--------------------------|-----|--|--|--|

| Pin# | Pin name                 | I/O |  |  |  |

| K7   | MIPI_CN                  | I   |  |  |  |

| J5   | MIPI_D0P                 | I   |  |  |  |

| K5   | MIPI_D0N                 | I   |  |  |  |

| J6   | MIPI_D1P <sup>1</sup>    | I   |  |  |  |

| K6   | MIPI_D1N <sup>1</sup>    | I   |  |  |  |

| J9   | MIPI_D2N <sup>1, 2</sup> | I   |  |  |  |

| J8   | MIPI_D2P <sup>1, 2</sup> | I   |  |  |  |

| L8   | MIPI_D3P <sup>1, 2</sup> | I   |  |  |  |

| K8   | MIPI_D3N <sup>1, 2</sup> | I   |  |  |  |

|      | CVDDQ Power Domain       | l   |  |  |  |

| D7   | CLKIN                    | I   |  |  |  |

| D6   | CLKIN_32                 | I   |  |  |  |

|      | VDDIO1 Power Domain      |     |  |  |  |

| D9   | I2C_SCL                  | I/O |  |  |  |

| D10  | I2C_SDA                  | I/O |  |  |  |

| E7   | TDI                      | I   |  |  |  |

| C10  | TDO                      | 0   |  |  |  |

| B11  | TRST#                    | I   |  |  |  |

| E8   | TMS                      | I   |  |  |  |

| F6   | TCK                      | I   |  |  |  |

|      | Power Domains            | 1   |  |  |  |

| E10  | VUSB                     | PWR |  |  |  |

| A1   | U3VSSQ                   | PWR |  |  |  |

| H11  | VDDIO1                   | PWR |  |  |  |

| L9   | VDDIO1                   | PWR |  |  |  |

| E3   | VDDIO2                   | PWR |  |  |  |

| B1   | VDDIO3                   | PWR |  |  |  |

| В6   | CVDDQ                    | PWR |  |  |  |

| B5   | U3TXVDDQ                 | PWR |  |  |  |

| A2   | U3RXVDDQ                 | PWR |  |  |  |

| A7   | AVDD                     | PWR |  |  |  |

| B7   | AVSS                     | PWR |  |  |  |

| L5   | VDD_MIPI                 | PWR |  |  |  |

| B10  | VDD                      | PWR |  |  |  |

| J11  | VDD                      | PWR |  |  |  |

| C3   | VDD                      | PWR |  |  |  |

| E9   | VDD                      | PWR |  |  |  |

| F11  | VDD                      | PWR |  |  |  |

| H1   | VDD                      | PWR |  |  |  |

Table 6. CYUSB306X Pin List (continued)

|      | CX3      |     |

|------|----------|-----|

| Pin# | Pin name | I/O |

| L7   | VDD      | PWR |

| D8   | VSS      | PWR |

| E2   | VSS      | PWR |

| E11  | VSS      | PWR |

| G1   | VSS      | PWR |

| A8   | VSS      | PWR |

| G11  | VSS      | PWR |

| L1   | VSS      | PWR |

| B8   | VSS      | PWR |

| L6   | VSS      | PWR |

| B2   | VSS      | PWR |

| L11  | VSS      | PWR |

| В9   | VSS      | PWR |

| K4   | VSS      | PWR |

| L3   | VSS      | PWR |

| K3   | VSS      | PWR |

| L2   | VSS      | PWR |

- Unused MIPI input data lanes to be connected to GND.

The signals MIPI\_D2N, MIPI\_D2P, MIPI\_D3N, and MIPI\_D3P are not available in the CYUSB3064 part. These pins should be left "open" in the customer board.

# **Absolute Maximum Ratings**

# **Operating Conditions**

| T <sub>A</sub> (ambient temperature under bias)<br>Industrial                                      | –40 °C to +85 °C |

|----------------------------------------------------------------------------------------------------|------------------|

| $V_{DD}$ , $A_{VDDQ}$ , $U3TX_{VDDQ}$ , $U3RX_{VDDQ}$<br>Supply voltage                            | 1.15 V to 1.25 V |

| V <sub>USB</sub> supply voltage                                                                    | 3.2 V to 6 V     |

| V <sub>DDIO1</sub> , V <sub>DDIO2</sub> , V <sub>DDIO3</sub> , C <sub>VDDQ</sub><br>Supply voltage | 1.7 V to 3.6 V   |

# **DC Specifications**

| Parameter            | Description                                  | Min                     | Max                    | Units | Notes                                                                                                                                       |

|----------------------|----------------------------------------------|-------------------------|------------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------|

| $V_{DD}$             | Core voltage supply                          | 1.15                    | 1.25                   | V     | 1.2-V typical                                                                                                                               |

| A <sub>VDD</sub>     | Analog voltage supply                        | 1.15                    | 1.25                   | V     | 1.2-V typical                                                                                                                               |

| V <sub>DD_MIPI</sub> | MIPI bridge D-PHY supply voltage             | 1.15                    | 1.25                   | V     | 1.2-V typical                                                                                                                               |

| V <sub>DDIO1</sub>   | I <sup>2</sup> C, JTAG and GPIO power domain | 1.7                     | 3.6                    | V     | 1.8-, 2.5-, and 3.3-V typical                                                                                                               |

| $V_{\rm DDIO2}$      | UART/I <sup>2</sup> S power supply domain    | 1.7                     | 3.6                    | V     | 1.8-, 2.5-, and 3.3-V typical                                                                                                               |

| $V_{\rm DDIO3}$      | SPI/I <sup>2</sup> S power supply domain     | 1.7                     | 3.6                    | V     | 1.8-, 2.5-, and 3.3-V typical                                                                                                               |

| V <sub>USB</sub>     | USB voltage supply                           | 3.2                     | 6                      | V     | 5-V typical                                                                                                                                 |

| U3TX <sub>VDDQ</sub> | USB 3.0 1.2-V supply                         | 1.15                    | 1.25                   | V     | 1.2-V typical. A 22-µF bypass capacitor is required on this power supply.                                                                   |

| U3RX <sub>VDDQ</sub> | USB 3.0 1.2-V supply                         | 1.15                    | 1.25                   | V     | 1.2-V typical. A 22-µF bypass capacitor is required on this power supply.                                                                   |

| C <sub>VDDQ</sub>    | Clock voltage supply                         | 1.7                     | 3.6                    | V     | 1.8-, 3.3-V typical                                                                                                                         |

| V <sub>IH1</sub>     | Input HIGH voltage 1                         | 0.625 × V <sub>CC</sub> | V <sub>CC</sub> + 0.3  | V     | For 2.0 V $\leq$ V <sub>CC</sub> $\leq$ 3.6 V (except USB and MIPI CSI-2 pins).V <sub>CC</sub> is the corresponding I/O voltage supply.     |

| V <sub>IH2</sub>     | Input HIGH voltage 2                         | V <sub>CC</sub> – 0.4   | V <sub>CC</sub> + 0.3  | V     | For 1.7 V $\leq$ V <sub>CC</sub> $\leq$ 2.0 V (except USB USB and MIPI CSI-2 pins).V <sub>CC</sub> is the corresponding I/O voltage supply. |

| V <sub>IL</sub>      | Input LOW voltage                            | -0.3                    | 0.25 × V <sub>CC</sub> | V     | V <sub>CC</sub> is the corresponding I/O voltage supply.                                                                                    |

| V <sub>OH</sub>      | Output HIGH voltage                          | 0.9 × V <sub>CC</sub>   | _                      | ٧     | $I_{OH}$ (max) = -100 $\mu$ A tested at quarter drive strength. $V_{CC}$ is the corresponding I/O voltage supply.                           |

| V <sub>OL</sub>      | Output LOW voltage                           | -                       | 0.1 × V <sub>CC</sub>  | ٧     | $I_{OL}$ (min) = +100 $\mu$ A tested at quarter drive strength. $V_{CC}$ is the corresponding I/O voltage supply.                           |

Document Number: 001-87516 Rev. \*K

# DC Specifications (continued)

| Parameter            | Description                                                                                       | Min             | Max | Units | Notes                                                                                                                                                               |

|----------------------|---------------------------------------------------------------------------------------------------|-----------------|-----|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| l <sub>IX</sub>      | Input leakage current for all pins except SSTXP/SSXM/SSRXP/SSRXM                                  | -1              | 1   | μА    | All I/O signals held at $V_{DDQ}$ (For I/Os with a pull-up or pull-down resistor connected, the leakage current increases by $V_{DDQ}/R_{PU}$ or $V_{DDQ}/R_{PD}$ ) |

| l <sub>OZ</sub>      | Output High-Z leakage current for all pins except SSTXP/ SSXM/ SSRXP/SSRXM and MIPI CSI-2 signals | -1              | 1   | μA    | All I/O signals held at V <sub>DDQ</sub>                                                                                                                            |

| I <sub>CC</sub> Core | Core and analog voltage operating current                                                         | -               | 192 | mA    | Total current through A <sub>VDD</sub> , V <sub>DD</sub>                                                                                                            |

| I <sub>CC</sub> USB  | USB voltage supply operating current                                                              | -               | 60  | mA    | -                                                                                                                                                                   |

|                      | Total suspend current during                                                                      | Core: 558.35 µA | -   | μA    | Core Current is measured through                                                                                                                                    |

| I <sub>SB1</sub>     | suspend mode with USB 3.0 PHY                                                                     | I/O: 4.58 μA    | -   | μA    | V <sub>DD</sub> , A <sub>VDD</sub> and V <sub>DD_MIPI</sub> .                                                                                                       |

|                      | enabled                                                                                           | USB: 4672 μA    | -   | μA    | I/O Current is measured through                                                                                                                                     |

|                      | T-1-1-1-1                                                                                         | Core: 148.31 µA | -   | μA    | V <sub>DDIO1</sub> to V <sub>DDIO3</sub> .                                                                                                                          |

| I <sub>SB3</sub>     | Total standby current during core power-down mode                                                 | I/O: 3.16 μA    | _   | μA    | USB Current is measured through                                                                                                                                     |

|                      |                                                                                                   | USB: 15.8 μA    | -   | μA    | $V_{\rm USB}$ , U3TX $_{ m VDDQ}$ and U3RX $_{ m VDDQ}$ .                                                                                                           |

| V <sub>RAMP</sub>    | Voltage ramp rate on core and I/O supplies                                                        | 0.2             | 12  | V/ms  | Voltage ramp must be monotonic                                                                                                                                      |

| V <sub>N</sub>       | Noise level permitted on V <sub>DD</sub> and I/O supplies                                         | -               | 100 | mV    | Max p-p noise level permitted on all supplies except A <sub>VDD</sub>                                                                                               |

| V <sub>N_AVDD</sub>  | Noise level permitted on A <sub>VDD</sub> supply                                                  | _               | 20  | mV    | Max p-p noise level permitted on A <sub>VDD</sub>                                                                                                                   |

# **MIPI D-PHY Electrical Characteristics**

| Parameter              | Description                          |                                                | Spec |      |      |  |

|------------------------|--------------------------------------|------------------------------------------------|------|------|------|--|

| Parameter              | Description -                        |                                                | Nom  | Max  | Unit |  |

| MIPI D-PHY F           | RX DC Characteristics                | <u>,                                      </u> | •    | •    | •    |  |

| V <sub>PIN</sub>       | Pin signal voltage range             | -50                                            | _    | 1350 | mV   |  |

| V <sub>IH</sub>        | Logic 1 input voltage                | 880                                            | _    | -    | mV   |  |

| V <sub>IL</sub>        | Logic 0 input voltage                | _                                              | _    | 550  | mV   |  |

| V <sub>CMRX (DC)</sub> | Common-mode voltage HS receiver mode | 70                                             | _    | 330  | mV   |  |

| $V_{\text{IDTH}}$      | Differential input high threshold    |                                                | _    | 70   | mV   |  |

| $V_{IDTL}$             | Differential input low threshold     | <b>–</b> 70                                    | _    | -    | mV   |  |

| V <sub>IHHS</sub>      | Single-ended input high voltage      |                                                | _    | 460  | mV   |  |

| V <sub>ILHS</sub>      | Single-ended input low voltage       | -40                                            | _    | _    | mV   |  |

# **AC Timing Parameters**

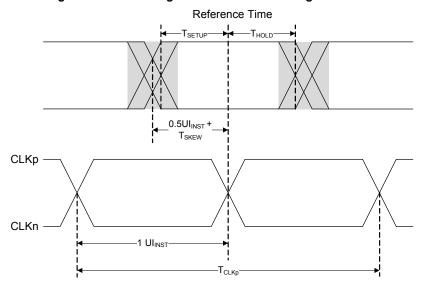

# **MIPI Data to Clock Timing Reference**

Figure 6. MIPI CSI Signal Data to Clock Timing Reference

Table 7. MIPI Data to Clock Timing Reference

| Parameter          | Description                                    | Min   | Max  | Units              |

|--------------------|------------------------------------------------|-------|------|--------------------|

| T <sub>SKEW</sub>  | Data to clock skew measured at the transmitter | -0.15 | 0.15 | UI <sub>INST</sub> |

| T <sub>SETUP</sub> | Data to clock setup time at receiver           | 0.15  | _    | UI <sub>INST</sub> |

| T <sub>HOLD</sub>  | Clock to data hold time at receiver            | 0.15  | _    | UI <sub>INST</sub> |

| UI <sub>INST</sub> | One data bit time (instantaneous)              | 1     | 12.5 | ns                 |

| T <sub>CLKp</sub>  | Period of dual data rate clock                 | 2     | 25   | ns                 |

# **Reference Clock Specifications**

Table 8. Reference Clock Specifications

| Parameter     | Description                         | Min  | Max | Units | Notes |

|---------------|-------------------------------------|------|-----|-------|-------|

| RefClk        | Reference clock frequency           | 6    | 40  | MHz   | _     |

| RefclkDutyCyl | Duty cycle                          | 40%  | 60% | _     | -     |

| RefClkPJ      | Reference clock input period jitter | -100 | 100 | ps    | -     |

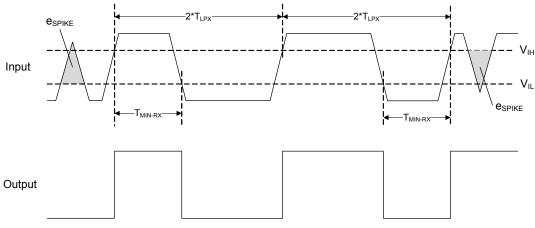

# **MIPI CSI Signal Low Power AC Characteristics**

Figure 7. MIPI CSI bus Input Glitch Rejection

Table 9. MIPI CSI Signal Low Power AC Characteristics

| Parameter           | Description                          | Min | Max | Units | Notes                                                                                                                                                                                          |

|---------------------|--------------------------------------|-----|-----|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| e <sub>SPIKE</sub>  | Input noise rejection                | -   | 300 |       | Time-voltage integration of a spike above $V_{\text{IL}}$ when being in LP-0 or below $V_{\text{IH}}$ when being in LP-1 state.  An impulse less than this will not change the receiver state. |

| T <sub>MIN-RX</sub> | Minimum pulse width response         | 20  | -   | ns    | An input pulse greater than this shall toggle the output.                                                                                                                                      |

| V <sub>INT</sub>    | peak interference amplitude          | -   | 200 | mV    | -                                                                                                                                                                                              |

| F <sub>INT</sub>    | Interference frequency               | 450 | _   | MHz   | -                                                                                                                                                                                              |

| T <sub>LPX</sub>    | Length of any low power state period | 50  | -   | ns    | -                                                                                                                                                                                              |

# **AC Specifications**

Table 10. AC Specifications

| Parameter | Description                                     | Min | Max | Units | Details / Conditions                                                                                        |

|-----------|-------------------------------------------------|-----|-----|-------|-------------------------------------------------------------------------------------------------------------|

| Λ \/      | Common-mode interference beyond 450 MHz         | 1   | 100 | mV    | $\Delta V_{CMRX(HF)}$ is the peak amp. Of a sine wave superimposed on the receiver inputs.                  |

| // //     | Common-mode interference<br>beyond 50 - 450 MHz | -50 | 50  | mV    | Excluding static ground shift of 50 mV. Voltage difference compared to the DC average common-mode potential |

# **Serial Peripherals Timing**

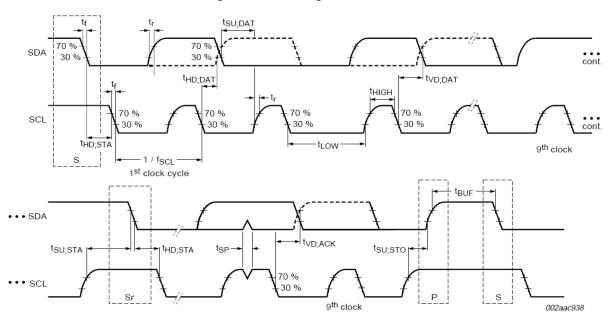

I<sup>2</sup>C Timing

Figure 8. I<sup>2</sup>C Timing Definition

Table 11. I<sup>2</sup>C Timing Parameters<sup>[2]</sup>

| Parameter           | Description                                                   | Min | Max  | Units |

|---------------------|---------------------------------------------------------------|-----|------|-------|

|                     | I <sup>2</sup> C Standard Mode Parameters                     | 1   | •    |       |

| f <sub>SCL</sub>    | SCL clock frequency                                           | 0   | 100  | kHz   |

| t <sub>HD:STA</sub> | Hold time START condition                                     | 4   | _    | μs    |

| t <sub>LOW</sub>    | LOW period of the SCL                                         | 4.7 | _    | μs    |

| t <sub>HIGH</sub>   | HIGH period of the SCL                                        | 4   | _    | μs    |

| t <sub>SU:STA</sub> | Setup time for a repeated START condition                     | 4.7 | _    | μs    |

| t <sub>HD:DAT</sub> | Data hold time                                                | 0   | _    | μs    |

| t <sub>SU:DAT</sub> | Data setup time                                               | 250 | _    | ns    |

| t <sub>r</sub>      | Rise time of both SDA and SCL signals                         | _   | 1000 | ns    |

| t <sub>f</sub>      | Fall time of both SDA and SCL signals                         | _   | 300  | ns    |

| t <sub>SU:STO</sub> | Setup time for STOP condition                                 | 4   | _    | μs    |

| t <sub>BUF</sub>    | Bus free time between a STOP and START condition              | 4.7 | _    | μs    |

| t <sub>VD:DAT</sub> | Data valid time                                               | _   | 3.45 | μs    |

| t <sub>VD:ACK</sub> | Data valid ACK                                                | _   | 3.45 | μs    |

| t <sub>SP</sub>     | Pulse width of spikes that must be suppressed by input filter | n/a | n/a  |       |

#### Note

Document Number: 001-87516 Rev. \*K

<sup>2.</sup> All parameters guaranteed by design and validated through characterization.

Table 11. I<sup>2</sup>C Timing Parameters<sup>[2]</sup> (continued)

| Parameter           | Description                                                   | Min      | Max  | Units |

|---------------------|---------------------------------------------------------------|----------|------|-------|

|                     | I <sup>2</sup> C Fast Mode Parameters                         |          | •    | •     |

| f <sub>SCL</sub>    | SCL clock frequency                                           | 0        | 400  | kHz   |

| t <sub>HD:STA</sub> | Hold time START condition                                     | 0.6      | _    | μs    |

| t <sub>LOW</sub>    | LOW period of the SCL                                         | 1.3      | _    | μs    |

| t <sub>HIGH</sub>   | HIGH period of the SCL                                        | 0.6      | _    | μs    |

| t <sub>SU:STA</sub> | Setup time for a repeated START condition                     | 0.6      | _    | μs    |

| t <sub>HD:DAT</sub> | Data hold time                                                | 0        | _    | μs    |

| t <sub>SU:DAT</sub> | Data setup time                                               | 100      | _    | ns    |

| t <sub>r</sub>      | Rise time of both SDA and SCL signals                         | _        | 300  | ns    |

| t <sub>f</sub>      | Fall time of both SDA and SCL signals                         | _        | 300  | ns    |

| t <sub>SU:STO</sub> | Setup time for STOP condition                                 | 0.6      | _    | μs    |

| t <sub>BUF</sub>    | Bus free time between a STOP and START condition              | 1.3      | _    | μs    |

| t <sub>VD:DAT</sub> | Data valid time                                               | _        | 0.9  | μs    |

| t <sub>VD:ACK</sub> | Data valid ACK                                                | _        | 0.9  | μs    |

| t <sub>SP</sub>     | Pulse width of spikes that must be suppressed by input filter | 0        | 50   | ns    |

|                     | I <sup>2</sup> C Fast Mode Plus Parameters                    | <u>.</u> |      |       |

| f <sub>SCL</sub>    | SCL clock frequency                                           | 0        | 1000 | kHz   |

| t <sub>HD:STA</sub> | Hold time START condition                                     | 0.26     | _    | μs    |

| t <sub>LOW</sub>    | LOW period of the SCL                                         | 0.5      | _    | μs    |

| t <sub>HIGH</sub>   | HIGH period of the SCL                                        | 0.26     | _    | μs    |

| t <sub>SU:STA</sub> | Setup time for a repeated START condition                     | 0.26     | _    | μs    |

| t <sub>HD:DAT</sub> | Data hold time                                                | 0        | _    | μs    |

| t <sub>SU:DAT</sub> | Data setup time                                               | 50       | _    | ns    |

| t <sub>r</sub>      | Rise time of both SDA and SCL signals                         | -        | 120  | ns    |

| t <sub>f</sub>      | Fall time of both SDA and SCL signals                         | -        | 120  | ns    |

| t <sub>SU:STO</sub> | Setup time for STOP condition                                 | 0.26     | _    | μs    |

| t <sub>BUF</sub>    | Bus-free time between a STOP and START condition              | 0.5      | _    | μs    |

| t <sub>VD:DAT</sub> | Data valid time                                               | _        | 0.45 | μs    |

| t <sub>VD:ACK</sub> | Data valid ACK                                                | _        | 0.55 | μs    |

| t <sub>SP</sub>     | Pulse width of spikes that must be suppressed by input filter | 0        | 50   | ns    |

|                     | •                                                             |          |      |       |

# I<sup>2</sup>S Timing Diagram

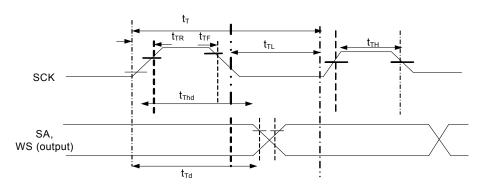

Figure 9. I<sup>2</sup>S Transmit Cycle

Table 12. I<sup>2</sup>S Timing Parameters<sup>[3]</sup>

| Parameter                   | Description                                                                               | Min                  | Max                  | Units |

|-----------------------------|-------------------------------------------------------------------------------------------|----------------------|----------------------|-------|

| t <sub>T</sub>              | I <sup>2</sup> S transmitter clock cycle                                                  | t <sub>TR</sub>      | -                    | ns    |

| t <sub>TL</sub>             | I <sup>2</sup> S transmitter cycle LOW period                                             | 0.35 t <sub>TR</sub> | -                    | ns    |

| t <sub>TH</sub>             | I <sup>2</sup> S transmitter cycle HIGH period                                            | 0.35 t <sub>TR</sub> | -                    | ns    |

| t <sub>TR</sub>             | I <sup>2</sup> S transmitter rise time                                                    | _                    | 0.15 t <sub>TR</sub> | ns    |

| t <sub>TF</sub>             | I <sup>2</sup> S transmitter fall time                                                    | _                    | 0.15 t <sub>TR</sub> | ns    |

| t <sub>Thd</sub>            | I <sup>2</sup> S transmitter data hold time                                               | 0                    | -                    | ns    |

| t <sub>Td</sub>             | I <sup>2</sup> S transmitter delay time                                                   | _                    | 0.8 t <sub>T</sub>   | ns    |

| Note t <sub>T</sub> is sele | ctable through clock gears. Max $t_{TR}$ is designed for 96-kHz codec at 32 bits to be 32 | 6 ns (3.072 l        | MHz).                |       |

Note

3. All parameters guaranteed by design and validated through characterization.

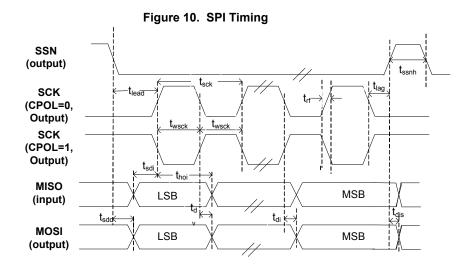

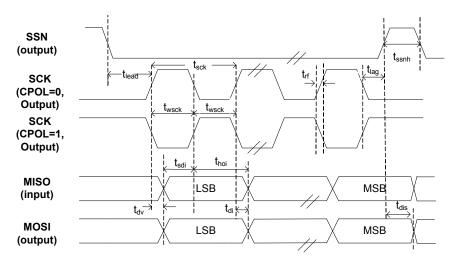

# SPI Timing Specification

# SPI Master Timing for CPHA = 0

**SPI Master Timing for CPHA = 1**

Table 13. SPI Timing Parameters<sup>[4]</sup>

| Parameter         | Description                         | Min                                     | Max                                     | Units |

|-------------------|-------------------------------------|-----------------------------------------|-----------------------------------------|-------|

| f <sub>op</sub>   | Operating frequency                 | 0                                       | 33                                      | MHz   |

| t <sub>sck</sub>  | Cycle time                          | 30                                      | _                                       | ns    |

| t <sub>wsck</sub> | Clock HIGH/LOW time                 | 13.5                                    | _                                       | ns    |

| t <sub>lead</sub> | SSN-SCK lead time                   | 1/2 t <sub>sck</sub> <sup>[5]</sup> – 5 | 1.5 t <sub>sck</sub> <sup>[5]</sup> + 5 | ns    |

| t <sub>lag</sub>  | Enable lag time                     | 0.5                                     | 1.5 t <sub>sck</sub> <sup>[5]</sup> + 5 | ns    |

| t <sub>rf</sub>   | Rise/fall time                      | -                                       | 8                                       | ns    |

| t <sub>sdd</sub>  | Output SSN to valid data delay time | -                                       | 5                                       | ns    |

| t <sub>dv</sub>   | Output data valid time              | -                                       | 5                                       | ns    |

| t <sub>di</sub>   | Output data invalid                 | 0                                       | _                                       | ns    |