Is Now Part of

# **ON Semiconductor**®

To learn more about ON Semiconductor, please visit our website at <u>www.onsemi.com</u>

ON Semiconductor and the ON Semiconductor logo are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor dates sheds, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor dates sheds and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights of others. ON Semiconductor products are not designed, intended, or authorized for use on similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor and its officers, employees, subsidiaries, affliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out or i, directly or indirectly, any lay bed ON Semiconductor and its officers, employees, ween if such claim alleges that ON Semiconductor was negligent regarding the d

October 2012

# FT3001 Reset Timer with Configurable Delay

#### Features

- Delay Times: 3.0, 3.75, 4.5, 6.0 Seconds

- ≤ 1 µA I<sub>CC</sub> Current Consumption in Standby

- Primary and Secondary Input Reset Pins

- Push-Pull and Open-Drain Output Pins

- 1.65 V to 5.0 V Operation at T<sub>A</sub> = 0°C to +85°C

- 1.7 V to 5.0 V Operation at T<sub>A</sub> = 0°C to +85°C

- 1.8 V to 5.0 V Operation at T<sub>A</sub> = -40°C to +85°C

- Available in 8-Lead MLP and 10-Lead UMLP Packages

- ESD Protection Exceeds:

- 4 kV HBM (per JESD22-A114 & Mil Std 883e 3015.7)

- 2 kV CDM (per ESD STM 5.3)

## Description

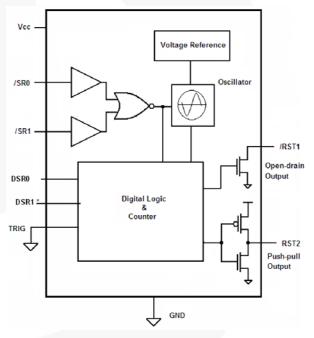

The FT3001 is a timer for resetting a mobile device where long reset times are needed. The long delay helps avoid unintended resets caused by accidental key presses. Four timer values can be selected by hardwiring the DSR0 and DSR1 pins.

The FT3001 has two inputs for single- or dual-button resetting capability. The device has two outputs: a push-pull output with 0.5 mA drive and an open-drain output with 0.5 mA pull-down drive.

The FT3001 draws minimal supply current when inactive and functions over a power supply range of 1.65 V to 5.0 V.

Figure 1. Block Diagram

### **Ordering Information**

| Part Number | Operating Package Temperature Range |                                                                           | Packing Method              |  |

|-------------|-------------------------------------|---------------------------------------------------------------------------|-----------------------------|--|

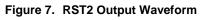

| FT3001UMX   | -40°C to +85°C                      | 10-Lead, Ultrathin MLP, 1.4 x 1.8 x 0.55mm<br>Package, 0.40 mm Pitch      | 5000 Units<br>Tape and Reel |  |

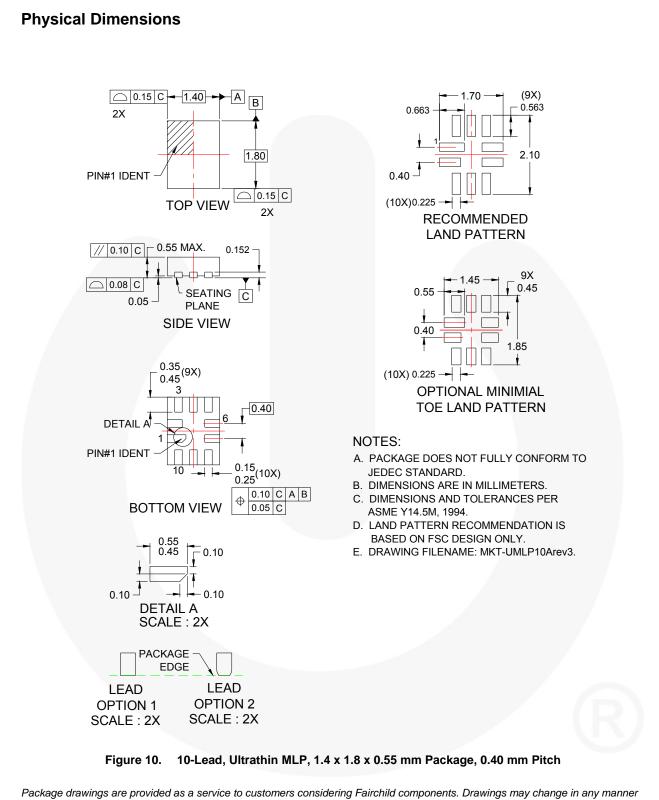

| FT3001MPX   | -40°C to +85°C                      | 8-Lead, Molded Leadless Package (MLP),<br>Dual JEDEC, MO-229 2.0 x 2.0 mm | 3000 Units<br>Tape and Reel |  |

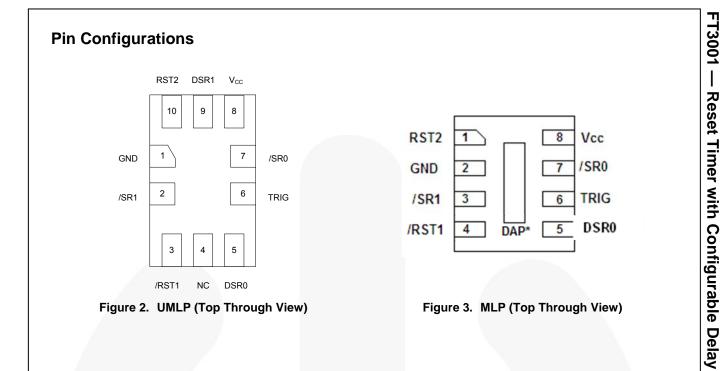

# **Pin Definitions**

| UMLP<br>Pin# | MLP<br>Pin# | Name            | Description                                                                                                          |  |  |

|--------------|-------------|-----------------|----------------------------------------------------------------------------------------------------------------------|--|--|

| 1            | 2           | GND             | Ground                                                                                                               |  |  |

| 2            | 3           | /SR1            | Secondary Reset Input, Active LOW                                                                                    |  |  |

| 3            | 4           | /RST1           | Open-Drain Output, Active LOW                                                                                        |  |  |

| 4            |             | NC              | No Connect                                                                                                           |  |  |

| 5            | 5           | DSR0            | Delay Selection Input (Must be tied directly to GND or $V_{CC}$ ; do not use pull-up or pull-down resistors.)        |  |  |

| 6            | 6           | TRIG            | Test Pin; tied to ground in normal use                                                                               |  |  |

| 7            | 7           | /SR0            | Primary Reset Input, Active LOW                                                                                      |  |  |

| 8            | 8           | V <sub>cc</sub> | Power Supply                                                                                                         |  |  |

| 9            |             | DSR1            | Delay Selection Input (Must be tied directly to GND or $V_{\text{CC}}$ ; do not use pull-up or pull-down resistors.) |  |  |

| 10           | 1           | RST2            | Push-Pull Output, Active HIGH                                                                                        |  |  |

FT3001 — Reset Timer with Configurable Delay

## **Absolute Maximum Ratings**

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

| Symbol                           | Parameter                                    | Condition                          | Min. | Max.                 | Unit |

|----------------------------------|----------------------------------------------|------------------------------------|------|----------------------|------|

| V <sub>CC</sub>                  | Supply Voltage                               |                                    | -0.5 | 7.0                  | V    |

| V <sub>IN</sub>                  | DC Input Voltage                             | /SR0, /SR1, TRIG, DSR0             | -0.5 | 7.0                  | V    |

| V                                | Output Voltage <sup>(1)</sup>                | /RST1, RST2 HIGH or LOW            | -0.5 | V <sub>CC</sub> +0.5 | V    |

| V <sub>OUT</sub>                 | Oulput voltage                               | /RST1, RST2, V <sub>CC</sub> =0 V  | -0.5 | 7.0                  | v    |

| I <sub>IK</sub>                  | DC Input Diode Current                       | V <sub>IN</sub> < 0 V              |      | -50                  | mA   |

|                                  | DC Output Diada Current                      | V <sub>OUT</sub> < 0 V             |      | -50                  | mA   |

| Ι <sub>οκ</sub>                  | DC Output Diode Current                      | V <sub>OUT</sub> > V <sub>CC</sub> |      | +50                  |      |

| I <sub>OH</sub> /I <sub>OL</sub> | DC Output Source/Sink Current                |                                    | -50  | +50                  | mA   |

| I <sub>CC</sub>                  | DC V <sub>CC</sub> or Ground Current per Sup | ply Pin                            |      | ±100                 | mA   |

| T <sub>STG</sub>                 | Storage Temperature Range                    |                                    | -65  | +150                 | °C   |

| V <sub>CC</sub>                  | Junction Temperature Under Bias              |                                    |      | +150                 | °C   |

| V <sub>IN</sub>                  | Junction Lead Temperature, Solder            |                                    | +260 | °C                   |      |

| PD                               | Power Dissipation                            |                                    |      | 5                    | mW   |

|                                  |                                              | Human Body Model, JESD22-A114      | 4 4  |                      |      |

| ESD                              | Electrostatic Discharge Capability           | Charged Device Model, JESD22-C101  |      | 2                    | kV   |

Note:

1. I<sub>O</sub> absolute maximum rating must be observed.

## **Recommended Operating Conditions**

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance to the datasheet specifications. Fairchild does not recommend exceeding them or designing to Absolute Maximum Ratings.

| Symbol               | Parameter                             | Conditions                                         | Min. | Max.            | Unit |

|----------------------|---------------------------------------|----------------------------------------------------|------|-----------------|------|

|                      |                                       | $T_A = 0^{\circ}C$ to +85°C                        | 1.65 | 5.00            |      |

| V <sub>CC</sub>      | Supply Voltage                        | $T_A = -25^{\circ}C$ to $+85^{\circ}C$             | 1.7  | 5.0             | V    |

|                      |                                       | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$      | 1.8  | 5.0             |      |

| t <sub>VCC_REC</sub> | Vcc Recovery Time After Power<br>Down | Vcc = 0 V after power down, then rising to $0.5 V$ | 5    |                 | ms   |

| V <sub>IN</sub>      | Input Voltage <sup>(2)</sup>          | /SR0, /SR1                                         | 0    | 5.0             | V    |

| M                    | Output Maltage                        | /RST1, RST2 High or Low                            | 0    | V <sub>cc</sub> | V    |

| V <sub>OUT</sub>     | Output Voltage                        | /RST1, RST2, V <sub>CC</sub> = 0 V                 | 0    | 5.0             | v    |

|                      |                                       | RST2, 1.8 V $\leq$ V <sub>CC</sub> $\leq$ 3.0 V    | -100 |                 |      |

| I <sub>он</sub>      | DC Output Source Current              | RST2, 3.0 V $\leq$ V <sub>CC</sub> $\leq$ 5.0 V    | -500 |                 | μA   |

| I <sub>OL</sub>      | DC Output Sink Current                | /RST1, RST2, V <sub>CC</sub> = 1.8V to 5.0 V       | +500 |                 | C    |

| T <sub>A</sub>       | Free Air Operating Temperature        |                                                    | -40  | +85             | °C   |

|                      | Thermal Resistance                    | MLP-8                                              |      | 245             | °C/W |

| $\Theta_{JA}$        | Thermal Resistance                    | UMLP-10                                            |      | 200             | 0/00 |

Notes:

2. All unused inputs must be held at  $V_{CC}$  or GND.

# **DC Electrical Characteristics**

Unless otherwise specified, conditions of T<sub>A</sub>=-40 to 80C with V<sub>CC</sub>=1.8 - 5.0V <u>OR</u> T<sub>A</sub>=-25 to 85C with V<sub>CC</sub>=1.7 - 5V <u>OR</u> T<sub>A</sub>=0 to 85C with V<sub>CC</sub>=1.65 - 5V produce the performance characteristics below.

| Symbol          | Parameter                                    | Condition                                      |                       | Max.                | Unit |  |

|-----------------|----------------------------------------------|------------------------------------------------|-----------------------|---------------------|------|--|

| V <sub>IH</sub> | Input High Voltage <sup>(3)</sup>            | /SR0, /SR1                                     | $0.8 \times V_{CC}$   |                     | V    |  |

| V <sub>IL</sub> | Input Low Voltage                            | /SR0, /SR1                                     |                       | $0.2 \times V_{CC}$ | V    |  |

| V <sub>IH</sub> | Input High Voltage                           | DSR0, DSR1                                     | 0.8 x V <sub>CC</sub> | y n                 | V    |  |

| V <sub>IL</sub> | Input Low Voltage                            | DSR0, DSR1                                     |                       | $0.2 \times V_{CC}$ | V    |  |

|                 |                                              | RST2, I <sub>OH</sub> =-100 µA                 | 0.8 x V <sub>CC</sub> |                     |      |  |

| V <sub>OH</sub> | High Level Output Voltage                    | RST2, $I_{OH}$ =-500 µA, $V_{CC}$ =3.0 to 5.0V | 0.8 x V <sub>CC</sub> |                     | V    |  |

| V               |                                              | RST2, Ι <sub>ΟL</sub> =500 μΑ                  |                       | 0.3                 | V    |  |

| V <sub>OL</sub> | Low Level Output Voltage                     | /RST1, I <sub>OL</sub> =500 µA                 |                       | 0.3                 | V    |  |

| I <sub>IN</sub> | Input Leakage Current                        | V <sub>IN</sub> =0.0 V or 5.0 V                |                       | ±1                  | μA   |  |

| I <sub>CC</sub> | Quiescent Supply Current (Timer<br>Inactive) | /SR0 or /SR1=V <sub>CC</sub>                   |                       | 1                   | μA   |  |

| I <sub>cc</sub> | Dynamic Supply Current (Timer Active)        | /SR0 and /SR1=0 V                              |                       | 100                 | μA   |  |

#### Note:

3. /SR0 and /SR1 HIGH levels should be referenced to the same  $V_{CC}$  rail supplying the FT3001.

# **AC Electrical Characteristics**

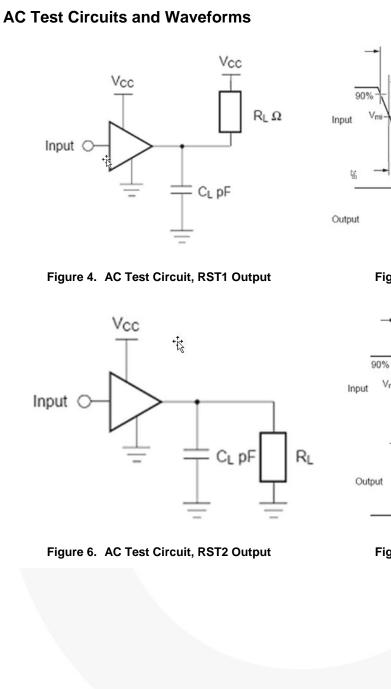

Unless otherwise specified, conditions of  $T_A$ =-40 to 80°C with  $V_{cc}$ =1.8 - 5.0 V <u>or</u>  $T_A$ =-25 to 85°C with  $V_{CC}$ =1.7 - 5 V <u>or</u>  $T_A$ =0 to 85°C with  $V_{cc}$ =1.65 - 5 V produce the performance characteristics below.

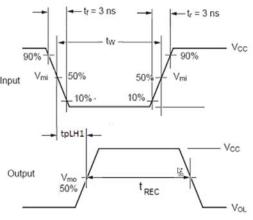

| Symbol              | Parameter                                      | Condition                                                                         | Min. | Тур. | Max. | Unit |

|---------------------|------------------------------------------------|-----------------------------------------------------------------------------------|------|------|------|------|

|                     | Timer Delay, /SRn to /RST1<br>(DSR0=0, DSR1=0) | $C_L=5 \text{ pF}, R_L=5 \text{ k}\Omega,$<br>Figure 9, Figure 4, Figure 5        | 2.40 | 3.00 | 3.60 |      |

| t <sub>PHL1</sub> , | Timer Delay, /SRn to /RST1<br>(DSR0=0, DSR1=1) | C <sub>L</sub> =5 pF, R <sub>L</sub> =5 k $\Omega$ , Figure 9, Figure 4, Figure 5 | 3.00 | 3.75 | 4.50 | s    |

| t <sub>PLH1</sub>   | Timer Delay, /SRn to RST2<br>(DSR0=1, DSR1=0)  | C <sub>L</sub> =5 pF, R <sub>L</sub> =10 k $\Omega$ , Figure 6, Figure 7          | 3.60 | 4.50 | 5.40 | 3    |

|                     | Timer Delay, /SRn to RST2<br>(DSR0=1, DSR1=1), | C <sub>L</sub> =5 pF, R <sub>L</sub> =10 k $\Omega$ , Figure 6, Figure 7          | 4.80 | 6.00 | 7.20 |      |

| t <sub>REC</sub>    | Reset Timeout Delay, /RST1 and RST2            | Figure 4, Figure 5, Figure 6, Figure 7                                            |      | 400  |      | ms   |

# **Capacitance Specifications**

T<sub>A</sub> = +25°C.

| Symbol           | Parameter          | Condition              | Typical | Unit |

|------------------|--------------------|------------------------|---------|------|

| C <sub>IN</sub>  | Input Capacitance  | V <sub>CC</sub> =GND   | 4.0     | pF   |

| C <sub>OUT</sub> | Output capacitance | V <sub>CC</sub> =5.0 V | 5.0     | pF   |

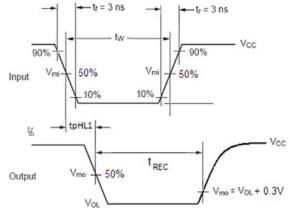

Figure 5. RST1 Output Waveform

## **Functional Description**

The reset timer uses an internal oscillator and a twostage 21-bit counter to determine when the output pins switch. The time, *n*, is set by the hard-wired logic level of the DSR0 and DSR1 pins. See Table 1 & 2.

#### Table 1. FT3001UMX Truth Table

| DSR0 | DSR1 | Reset Time (±20%)<br>in Seconds |

|------|------|---------------------------------|

| 0    | 0    | 3.00                            |

| 0    | 1    | 3.75                            |

| 1    | 0    | 4.50                            |

| 1    | 1    | 6.00                            |

#### Table 2. FT3001MPX Truth Table

| DSR0 | Reset Time (±20%)<br>in Seconds |

|------|---------------------------------|

| 0    | 3.0                             |

| 1    | 4.5                             |

The two CMOS input pins, /SR0 and /SR1, control the reset function. A low input signal on both /SR0 and /SR1 starts the oscillator. Both /SR0 and /SR1 pins must be held LOW for time n before the /RST1 and RST2 outputs are activated. The TRIG pin should be tied LOW during normal operation. The TRIG pin is used for SCAN testing.

#### Table 3. Short Duration

**Application Information**

**IMPORTANT**: The DSR0 and DSR1 pins must be tied directly to  $V_{CC}$  or GND to provide a HIGH or LOW voltage level. The voltage level on the DSR pin determines the length of the configurable delay. The voltage level on the DSR pins must not change during normal operation. Do not use pull-up or pull-down resistors on DSR pins.

#### Short Duration (Button Press Time < n)

In this case, both input /SR0 and /SR1 are LOW for a duration ( $t_W$ ) that is shorter than time *n*. When an input goes LOW, the internal timer starts counting. If the input goes HIGH before time *n*, the timer stops counting and resets and no changes occur on the outputs.

#### Long Duration $(t_w > n)$

In this case, both input /SR0 and /SR1 are LOW for a duration ( $t_W$ ) that is longer than time *n*. When an input goes LOW, the internal timer starts counting.

After time n, the outputs switch and the timer stops counting. After time  $t_{REC}$ , the outputs return to their original states.

| Table 5.                                                                                                                          | Short D | uration        |                      |                                                                                                                                                                                                                       |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------|---------|----------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| /SR0                                                                                                                              | /SR1    | /RST1          | RST2                 | Description                                                                                                                                                                                                           |  |  |

| V                                                                                                                                 | L       | Н              | L                    | The timer starts counting when both inputs go LOW. The timer stops counting and resets when either input goes high. No changes occur on the butputs. Both /SR0 and /SR1 need to be LOW to activate (start) the timer. |  |  |

| $/SR0 \longrightarrow T_W < N$<br>Or<br>/SR1<br>/SR1<br>/SR1<br>$T_W > N$<br>/SR1<br>/SR1<br>/SR1<br>/SR1<br>/SR1<br>/SR1<br>/SR1 |         |                |                      |                                                                                                                                                                                                                       |  |  |

| /RS                                                                                                                               |         | start<br>Timer | end<br>Tim           | Timer Timer                                                                                                                                                                                                           |  |  |

| RS                                                                                                                                | T2 = L  |                |                      | RST2                                                                                                                                                                                                                  |  |  |

|                                                                                                                                   | Figu    | re 8. Shor     | t Duratio            | Figure 9. Long Duration                                                                                                                                                                                               |  |  |

| Table 4.                                                                                                                          | Long D  | uration        |                      |                                                                                                                                                                                                                       |  |  |

| /SR0                                                                                                                              | /SR1    | /RST1          | RST2                 | Description                                                                                                                                                                                                           |  |  |

| $\nabla$                                                                                                                          | L       | $\sim$         | $\mathbf{\nabla}$    | The timer starts counting when both inputs go LOW. After time <i>n</i> , the                                                                                                                                          |  |  |

| L                                                                                                                                 |         |                | $\overline{\Lambda}$ | outputs switch. After time $t_{REC}$ , the outputs return to their original states.<br>Both /SR0 and /SR1 need to be LOW to activate (start) the timer.                                                               |  |  |

Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or obtain the most recent revision. Package specifications do not expand the terms of Fairchild's worldwide terms and conditions, specifically the warranty therein, which covers Fairchild products.

Always visit Fairchild Semiconductor's online packaging area for the most recent package drawings: <u>http://www.fairchildsemi.com/packaging/</u>.

Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or obtain the most recent revision. Package specifications do not expand the terms of Fairchild's worldwide terms and conditions, specifically the warranty therein, which covers Fairchild products.

Always visit Fairchild Semiconductor's online packaging area for the most recent package drawings: <u>http://www.fairchildsemi.com/packaging/</u>.

FT3001 — Reset Timer with Configurable Delay

#### FAIRCHILD SEMICONDUCTOR TRADEMARKS The following includes registered and unregistered trademarks and service marks, owned by Fairchild Semiconductor and/or its global subsidiaries, and is not intended to be an exhaustive list of all such trademarks. F-PFS™ PowerTrench® The Power Franchise® 2CoolT AccuPower™ FRFET® PowerXS™ wer Global Power Resource<sup>SM</sup> Programmable Active Droop™ AX-CAP™\* franchise QFET BitSiC™ GreenBridge™ TinyBoost™ OSTM Build it Now™ Green FPS™ TinyBuck™ CorePLUS™ Green FPS™ e-Series™ Quiet Series™ TinyCalc™ RapidConfigure™ **CorePOWER™** Gmax™ TinyLogic )™ CROSSVOLT **GTO™** TINYOPTOT IntelliMAX<sup>TM</sup> CTL™ Saving our world, 1mW/W/kW at a time™ TinyPower™ Current Transfer Logic™ **ISOPLANAR™** SignalWise™ TinyPWM™ Making Small Speakers Sound Louder DEUXPEED® SmartMax™ TinyWire™ Dual Cool™ and Better<sup>T</sup> SMART START Tran SIC™ EcoSPARK<sup>®</sup> MegaBuck™ Solutions for Your Success™ TriFault Detect™ MICROCOUPLER™ EfficientMax™ SPM TRUECURRENT®\* ESBC™ MicroFET™ **STEALTH™** uSerDes™ R MicroPak™ SuperFET® $\mu_{\scriptscriptstyle {\rm Ser} \scriptscriptstyle {\rm Des}}$ MicroPak2™ SuperSOT™-3 Fairchild® MillerDrive™ SuperSOT™-6 UHC Fairchild Semiconductor® Motion Max<sup>™</sup> SuperSOT™-8 Ultra FRFET™ FACT Quiet Series™ mWSaver™ SupreMOS<sup>®</sup> UniFET™ FACT OptoHiT™ FAST® SyncFET™ VCX™ **OPTOLOGIC®** Sync-Lock™ FastvCore™ VisualMax™ **OPTOPLANAR®** FETBench™ VoltagePlus™ FlashWriter®\* XS™ l ø **FPS™** \* Trademarks of System General Corporation, used under license by Fairchild Semiconductor. DISCLAIMER FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION, OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS. THESE SPECIFICATIONS DO NOT EXPAND THE TERMS OF FAIRCHILD'S WORLDWIDE TERMS AND CONDITIONS, SPECIFICALLY THE WARRANTY THEREIN, WHICH COVERS THESE PRODUCTS. LIFE SUPPORT POLICY FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein: 1. Life support devices or systems are devices or systems which, (a) are 2. A critical component in any component of a life support, device, or intended for surgical implant into the body or (b) support or sustain system whose failure to perform can be reasonably expected to life, and (c) whose failure to perform when properly used in cause the failure of the life support device or system, or to affect its accordance with instructions for use provided in the labeling, can be safety or effectiveness. reasonably expected to result in a significant injury of the user. ANTI-COUNTERFEITING POLICY Fairchild Semiconductor Corporation's Anti-Counterfeiting Policy. Fairchild's Anti-Counterfeiting Policy is also stated on our external website, www.fairchildsemi.com, under Sales Support Counterfeiting of semiconductor parts is a growing problem in the industry. All manufacturers of semiconductor products are experiencing counterfeiting of their parts. Customers who inadvertently purchase counterfeit parts experience many problems such as loss of brand reputation, substandard performance, failed applications, and increased cost of production and manufacturing delays. Fairchild is taking strong measures to protect ourselves and our customers from the proliferation of counterfeit parts. Fairchild strongly encourages customers to purchase Fairchild parts either directly from Fairchild or from Authorized Fairchild Distributors who are listed by country on our web page cited above. Products customers buy either from Fairchild directly or from Authorized Fairchild Distributors are genuine parts, have full traceability, meet Fairchild's quality standards for handling and storage and provide access to Fairchild's full range of up-to-date technical and product information. Fairchild and our Authorized Distributors will stand behind all warranties and will appropriately address any warranty issues that may arise. Fairchild will not provide any warranty coverage or other assistance for parts bought from Unauthorized Sources. Fairchild is committed to combat this global

problem and encourage our customers to do their part in stopping this practice by buying direct or from authorized distributors.

#### PRODUCT STATUS DEFINITIONS

| Definition of Terms      |                       |                                                                                                                                                                                                        |

|--------------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Datasheet Identification | Product Status        | Definition                                                                                                                                                                                             |

| Advance Information      | Formative / In Design | Datasheet contains the design specifications for product development. Specifications may change<br>in any manner without notice.                                                                       |

| Preliminary              | First Production      | Datasheet contains preliminary data; supplementary data will be published at a later date. Fairchild<br>Semiconductor reserves the right to make changes at any time without notice to improve design. |

| No Identification Needed | Full Production       | Datasheet contains final specifications. Fairchild Semiconductor reserves the right to make<br>changes at any time without notice to improve the design.                                               |

| Obsolete                 | Not In Production     | Datasheet contains specifications on a product that is discontinued by Fairchild Semiconductor.<br>The datasheet is for reference information only.                                                    |

Rev. 162

T3001 —

**Reset Timer with Configurable Delay**

# **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Fairchild Semiconductor: <u>FT3001UMX</u> FT3001MPX