# Single-Channel, 128-/64-/32-Position, $I^2C$ , ±8% Resistor Tolerance, Nonvolatile Digital Potentiometer

### **Data Sheet**

# AD5110/AD5112/AD5114

### FEATURES

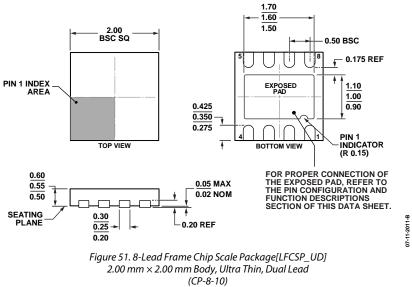

Nominal resistor tolerance error: ±8% maximum Wiper current: ±6 mA Rheostat mode temperature coefficient: 35 ppm/°C Low power consumption: 2.5 μA max @ 2.7 V and 125°C Wide bandwidth: 4 MHz (5 kΩ option) Power-on EEPROM refresh time < 50 μs 50-year typical data retention at 125°C 1 million write cycles 2.3 V to 5.5 V analog supply operation 1.8 V to 5.5 V logic supply operation Wide operating temperature: -40°C to +125°C Thin, 2 mm × 2 mm × 0.55 mm 8-lead LFCSP package

### **APPLICATIONS**

Mechanical potentiometer replacement Portable electronics level adjustment Audio volume control Low resolution DAC LCD panel brightness and contrast control Programmable voltage to current conversion Programmable filters, delays, time constants Feedback resistor programmable power supply Sensor calibration

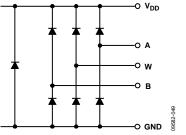

### FUNCTIONAL BLOCK DIAGRAM

Table 1. ±8% Resistance Tolerance Family

| Model  | Resistance (kΩ) | Position | Interface        |

|--------|-----------------|----------|------------------|

| AD5110 | 10, 80          | 128      | I <sup>2</sup> C |

| AD5111 | 10, 80          | 128      | Up/down          |

| AD5112 | 5, 10, 80       | 64       | I <sup>2</sup> C |

| AD5113 | 5, 10, 80       | 64       | Up/down          |

| AD5116 | 5, 10, 80       | 64       | Push-button      |

| AD5114 | 10, 80          | 32       | I <sup>2</sup> C |

| AD5115 | 10, 80          | 32       | Up/down          |

### **GENERAL DESCRIPTION**

The AD5110/AD5112/AD5114 provide a nonvolatile solution for 128-/64-/32-position adjustment applications, offering guaranteed low resistor tolerance errors of  $\pm 8\%$  and up to  $\pm 6$  mA current density in the A, B, and W pins. The low resistor tolerance, low nominal temperature coefficient and high bandwidth simplify open-loop applications, as well as tolerance matching applications.

The new low wiper resistance feature minimizes the wiper resistance in the extremes of the resistor array to only 45  $\Omega$ , typical.

The wiper settings are controllable through an I<sup>2</sup>C-compatible digital interface that is also used to readback the wiper register and EEPROM content. Resistor tolerance is stored within EEPROM, providing an end-to-end tolerance accuracy of 0.1%.

The AD5110/AD5112/AD5114 are available in a 2 mm  $\times$  2 mm LFCSP package. The parts are guaranteed to operate over the extended industrial temperature range of  $-40^{\circ}$ C to  $+125^{\circ}$ C.

#### **Document Feedback**

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

# TABLE OF CONTENTS

| Features                                      |

|-----------------------------------------------|

| Applications1                                 |

| Functional Block Diagram1                     |

| General Description                           |

| Revision History                              |

| Specifications                                |

| Electrical Characteristics—AD5110             |

| Electrical Characteristics—AD5112             |

| Electrical Characteristics—AD51147            |

| Interface Timing Specifications9              |

| Shift Register and Timing Diagram10           |

| Absolute Maximum Ratings11                    |

| Thermal Resistance11                          |

| ESD Caution11                                 |

| Pin Configuration and Function Descriptions12 |

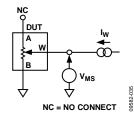

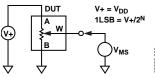

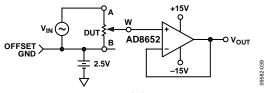

| Typical Performance Characteristics           |

| Test Circuits                                 |

### **REVISION HISTORY**

#### 11/12—Rev. A to Rev. B

| Changed Low Power Consumption from 2.5 mA to 2.5 µA | 1 |

|-----------------------------------------------------|---|

| Changed $I_{DD}$ Unit from mA to $\mu$ A, Table 2   | 4 |

| Changed $I_{DD}$ Unit from mA to $\mu$ A, Table 3   | 6 |

| Changed $I_{DD}$ Unit from mA to $\mu$ A, Table 4   | 8 |

| Changes to Figure 45                                |   |

|                                                     |   |

#### 4/12—Rev. 0 to Rev. A

| Changes to Features Section                 | 1  |

|---------------------------------------------|----|

| Changes to Positive Supply Current, Table 2 | 4  |

| Changes to Positive Supply Current, Table 3 | 6  |

| Changes to Positive Supply Current, Table 4 | 8  |

| Updated Outline Dimensions                  | 27 |

10/11—Revision 0: Initial Version

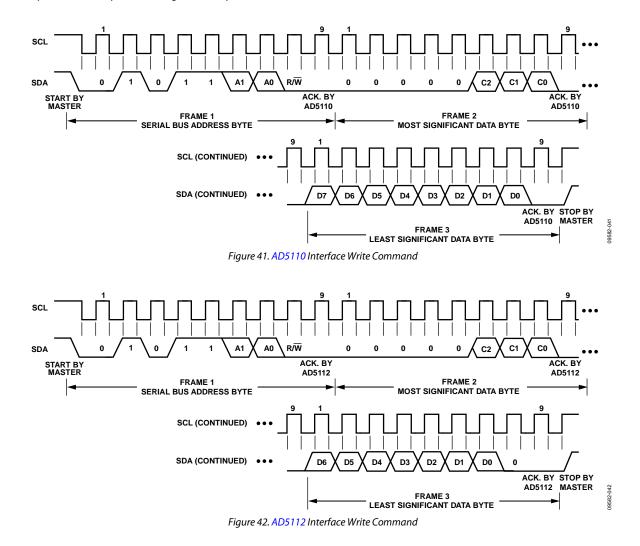

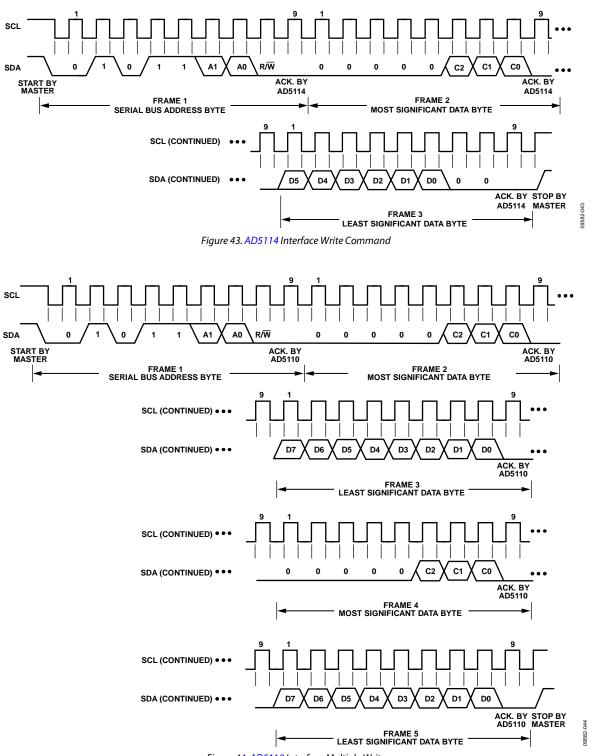

| Theory of Operation                    | 19 |

|----------------------------------------|----|

| RDAC Register and EEPROM               | 19 |

| I <sup>2</sup> C Serial Data Interface | 19 |

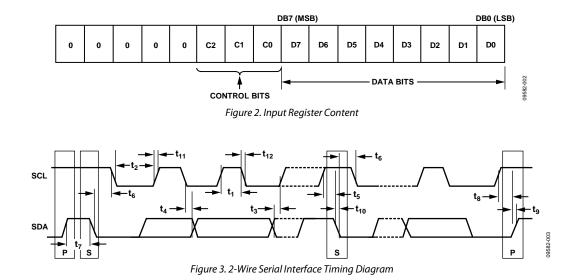

| Input Shift Register                   | 20 |

| Write Operation                        | 21 |

| EEPROM Write Acknowlegde Polling       | 23 |

| Read Operation                         | 23 |

| Reset                                  | 23 |

| Shutdown Mode                          | 23 |

| RDAC Architecture                      | 24 |

| Programming the Variable Resistor      | 24 |

| Programming the Potentiometer Divider  | 25 |

| Terminal Voltage Operating Range       | 26 |

| Power-Up Sequence                      | 26 |

| Layout and Power Supply Biasing        | 26 |

| Outline Dimensions                     | 27 |

| Ordering Guide                         | 27 |

|                                        |    |

# **SPECIFICATIONS**

### ELECTRICAL CHARACTERISTICS—AD5110

10 k $\Omega$  and 80 k $\Omega$  versions:  $V_{DD}$  = 2.3 V to 5.5 V,  $V_{LOGIC}$  = 1.8 V to  $V_{DD}$ ,  $V_A$  =  $V_{DD}$ ,  $V_B$  = 0 V, -40°C <  $T_A$  < +125°C, unless otherwise noted.

| Table 2. Parameter                                   | Symbol                                        | Test Conditions/Comments                                                                                                                           | Min                    | Typ <sup>1</sup> | Max                           | Unit   |

|------------------------------------------------------|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------------------|-------------------------------|--------|

| DC CHARACTERISTICS—RHEOSTAT MODE                     | Symbol                                        |                                                                                                                                                    |                        | 176              | Mux                           | Unit   |

| Resolution                                           | N                                             |                                                                                                                                                    | 7                      |                  |                               | Bits   |

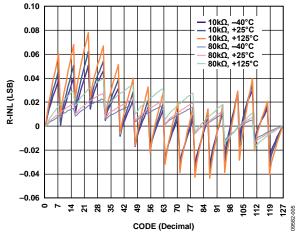

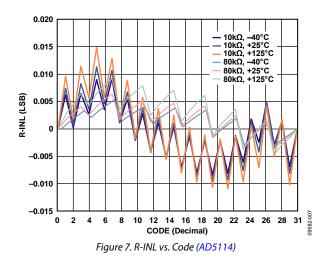

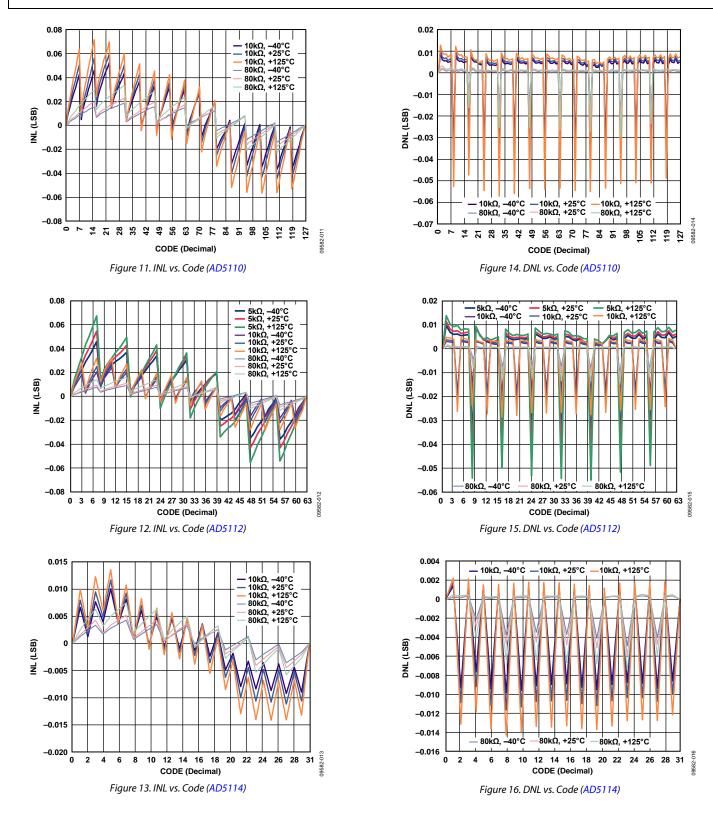

| Resistor Integral Nonlinearity <sup>2</sup>          | R-INL                                         | $R_{AB} = 10 \text{ k}\Omega, V_{DD} = 2.3 \text{ V to } 2.7 \text{ V}$                                                                            | -2.5                   | ±0.5             | +2.5                          | LSB    |

| nesistor integra Nonincurty                          |                                               | $R_{AB} = 10 \text{ k}\Omega, V_{DD} = 2.3 \text{ V to } 2.7 \text{ V}$<br>$R_{AB} = 10 \text{ k}\Omega, V_{DD} = 2.7 \text{ V to } 5.5 \text{ V}$ | -1                     | ±0.25            | +1                            | LSB    |

|                                                      |                                               | $R_{AB} = 80 \text{ k}\Omega$                                                                                                                      | -0.5                   | ±0.25            | +0.5                          | LSB    |

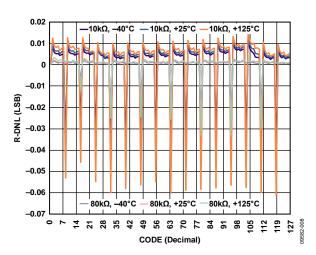

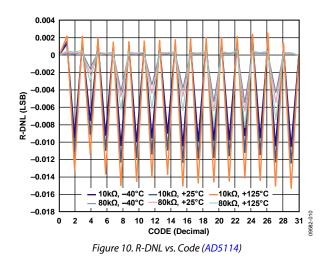

| Resistor Differential Nonlinearity <sup>2</sup>      | R-DNL                                         |                                                                                                                                                    | -1                     | ±0.1             | +1                            | LSB    |

| Nominal Resistor Tolerance                           | $\Delta R_{AB}/R_{AB}$                        |                                                                                                                                                    | -8                     | _0.20            | +8                            | %      |

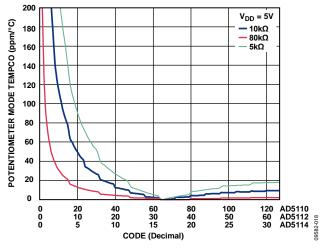

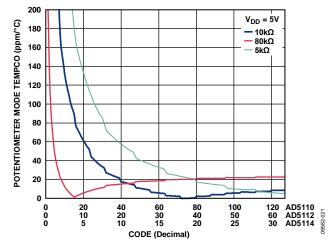

| Resistance Temperature Coefficient <sup>3</sup>      | $(\Delta R_{AB}/R_{AB})/\Delta T \times 10^6$ | Code = full scale                                                                                                                                  | U                      | 35               | 10                            | ppm/°C |

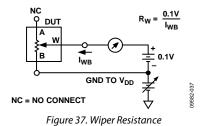

| Wiper Resistance                                     | R <sub>w</sub>                                | Code = zero scale                                                                                                                                  |                        | 70               | 140                           | Ω      |

| mpernesistance                                       | R <sub>BS</sub>                               | Code = bottom scale                                                                                                                                |                        | 45               | 80                            | Ω      |

|                                                      | R <sub>TS</sub>                               | Code = top scale                                                                                                                                   |                        | 70               | 140                           | Ω      |

| DC CHARACTERISTICS—POTENTIOMETER<br>DIVIDER MODE     |                                               |                                                                                                                                                    |                        |                  |                               |        |

| Integral Nonlinearity <sup>4</sup>                   | INL                                           |                                                                                                                                                    | -0.5                   | ±0.15            | +0.5                          | LSB    |

| Differential Nonlinearity <sup>4</sup>               | DNL                                           |                                                                                                                                                    | -0.5                   | ±0.15            | +0.5                          | LSB    |

| Full-Scale Error                                     | V <sub>WFSE</sub>                             | $R_{AB} = 10 \text{ k}\Omega$                                                                                                                      | -2.5                   |                  |                               | LSB    |

|                                                      | in se                                         | $R_{AB} = 80 \text{ k}\Omega$                                                                                                                      | -1.5                   |                  |                               | LSB    |

| Zero-Scale Error                                     | V <sub>WZSE</sub>                             | $R_{AB} = 10 \text{ k}\Omega$                                                                                                                      |                        |                  | 1.5                           | LSB    |

|                                                      | 11252                                         | $R_{AB} = 80 \text{ k}\Omega$                                                                                                                      |                        |                  | 0.5                           | LSB    |

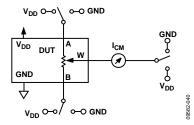

| Voltage Divider Temperature Coefficient <sup>3</sup> | $(\Delta V_w/V_w)/\Delta T \times 10^6$       | Code = half scale                                                                                                                                  |                        | ±10              |                               | ppm/°C |

| RESISTOR TERMINALS                                   |                                               |                                                                                                                                                    |                        |                  |                               |        |

| Maximum Continuous $I_A$ , $I_B$ , and $I_W$         |                                               | $R_{AB} = 10 \ k\Omega$                                                                                                                            | -6                     |                  | +6                            | mA     |

| Current <sup>3</sup>                                 |                                               | $R_{AB} = 80 \text{ k}\Omega$                                                                                                                      | -1.5                   |                  | +1.5                          | mA     |

| Terminal Voltage Range⁵                              |                                               | A0                                                                                                                                                 | GND                    |                  | $V_{DD}$                      | v      |

| Capacitance A, Capacitance B <sup>3</sup>            | C <sub>A</sub> , C <sub>B</sub>               | f = 1 MHz, measured to GND,<br>code = half scale,<br>$V_w = V_A = 2.5$ V or $V_w = V_B = 2.5$ V                                                    |                        | 20               |                               | pF     |

| Capacitance W <sup>3</sup>                           | C <sub>w</sub>                                | f = 1 MHz, measured to GND,<br>code = half scale, $V_A = V_B = 2.5$ V                                                                              |                        | 35               |                               | pF     |

| Common-Mode Leakage Current <sup>3</sup>             |                                               | $V_A = V_W = V_B$                                                                                                                                  | -500                   | ±15              | +500                          | nA     |

| DIGITAL INPUTS                                       |                                               |                                                                                                                                                    |                        |                  |                               |        |

| Input Logic <sup>3</sup>                             |                                               |                                                                                                                                                    |                        |                  |                               |        |

| High                                                 | V <sub>INH</sub>                              | $V_{LOGIC} = 1.8 V \text{ to } 2.3 V$                                                                                                              | $0.8 \times V_{LOGIC}$ |                  |                               | v      |

|                                                      |                                               | $V_{LOGIC} = 2.3 V \text{ to } 5.5 V$                                                                                                              | $0.7 \times V_{LOGIC}$ |                  |                               | V      |

| Low                                                  | V <sub>INL</sub>                              | $V_{LOGIC} = 1.8 V \text{ to } 2.3 V$                                                                                                              |                        |                  | $0.2 \times V_{\text{LOGIC}}$ | V      |

|                                                      |                                               | $V_{LOGIC} = 2.3 V \text{ to } 5.5 V$                                                                                                              |                        |                  | $0.3 \times V_{LOGIC}$        | V      |

| Input Hysteresis <sup>3</sup>                        | V <sub>HYST</sub>                             |                                                                                                                                                    | $0.1 \times V_{LOGIC}$ |                  |                               | V      |

| Input Current <sup>3</sup>                           | I <sub>N</sub>                                |                                                                                                                                                    |                        |                  | ±1                            | μA     |

| Input Capacitance <sup>3</sup>                       | C <sub>IN</sub>                               |                                                                                                                                                    |                        | 5                |                               | pF     |

| DIGITAL OUTPUT (SDA)                                 | 1                                             |                                                                                                                                                    |                        |                  |                               |        |

| Output Low Voltage <sup>3</sup>                      | V <sub>OL</sub>                               | I <sub>SINK</sub> = 3 mA                                                                                                                           |                        |                  | 0.2                           | V      |

|                                                      |                                               | $I_{SINK} = 6 \text{ mA}$                                                                                                                          |                        |                  | 0.4                           | v      |

| Three-State Leakage Current                          |                                               | 5                                                                                                                                                  | -1                     |                  | +1                            | μA     |

| Three-State Output Capacitance <sup>3</sup>          |                                               |                                                                                                                                                    |                        | 2                |                               | pF     |

| Parameter                                | Symbol                    | <b>Test Conditions/Comments</b>                                                     | Min | Typ <sup>1</sup> | Max      | Unit    |

|------------------------------------------|---------------------------|-------------------------------------------------------------------------------------|-----|------------------|----------|---------|

| POWER SUPPLIES                           |                           |                                                                                     |     |                  |          |         |

| Single-Supply Power Range                |                           |                                                                                     | 2.3 |                  | 5.5      | V       |

| Logic Supply Range                       |                           |                                                                                     | 1.8 |                  | $V_{DD}$ | V       |

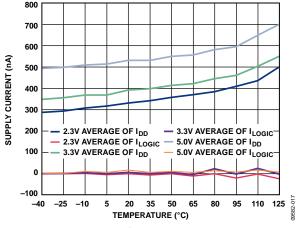

| Positive Supply Current                  | I <sub>DD</sub>           | $V_{DD} = 5 V$                                                                      |     | 0.75             | 3.5      | μA      |

|                                          |                           | $V_{DD} = 2.7 V$                                                                    |     |                  | 2.5      | μA      |

|                                          |                           | $V_{DD} = 2.3 V$                                                                    |     |                  | 2.4      | μA      |

| EEMEM Store Current <sup>3, 6</sup>      | I <sub>DD_NVM_STORE</sub> |                                                                                     |     | 2                |          | mA      |

| EEMEM Read Current <sup>3, 7</sup>       | I <sub>DD_NVM_READ</sub>  |                                                                                     |     | 320              |          | μA      |

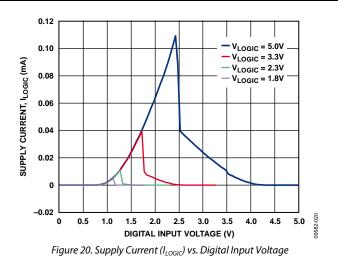

| Logic Supply Current                     | I <sub>LOGIC</sub>        | $V_{IH} = V_{LOGIC}$ or $V_{IL} = GND$                                              |     | 30               |          | nA      |

| Power Dissipation <sup>8</sup>           | P <sub>DISS</sub>         | $V_{IH} = V_{LOGIC}$ or $V_{IL} = GND$                                              |     | 5                |          | μW      |

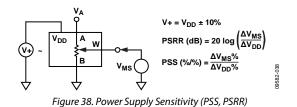

| Power Supply Rejection <sup>3</sup>      | PSR                       | $\Delta V_{DD} / \Delta V_{SS} = 5 \text{ V} \pm 10\%$                              |     |                  |          |         |

|                                          |                           | $R_{AB} = 10 \ k\Omega$                                                             |     | -50              |          | dB      |

|                                          |                           | $R_{AB} = 80 \ k\Omega$                                                             |     | -64              |          | dB      |

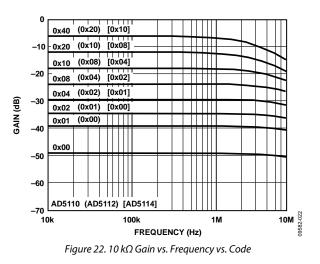

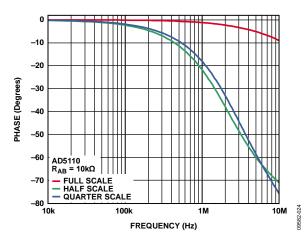

| DYNAMIC CHARACTERISTICS <sup>3, 9</sup>  |                           |                                                                                     |     |                  |          |         |

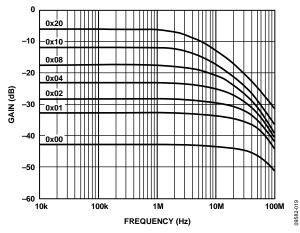

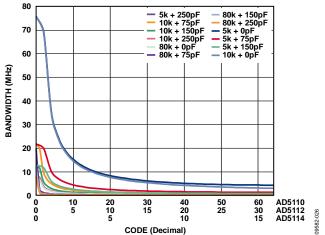

| Bandwidth                                | BW                        | Code = half scale, -3 dB                                                            |     |                  |          |         |

|                                          |                           | $R_{AB} = 10 \ k\Omega$                                                             |     | 2                |          | MHz     |

|                                          |                           | $R_{AB} = 80 \ k\Omega$                                                             |     | 200              |          | kHz     |

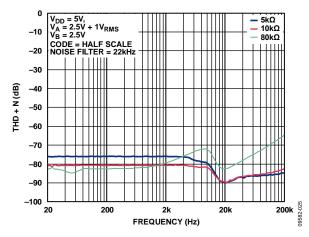

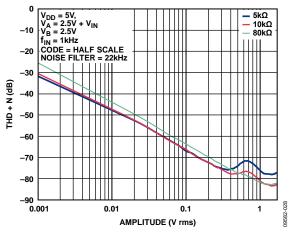

| Total Harmonic Distortion                | THD                       | $V_A = V_{DD}/2 + 1 V \text{ rms}, V_B = V_{DD}/2,$<br>f = 1 kHz, code = half scale |     |                  |          |         |

|                                          |                           | $R_{AB} = 10 \ k\Omega$                                                             |     | -80              |          | dB      |

|                                          |                           | $R_{AB} = 80 \ k\Omega$                                                             |     | -85              |          | dB      |

| V <sub>w</sub> Settling Time             | t <sub>s</sub>            | $V_A = 5 V, V_B = 0 V,$<br>±0.5 LSB error band                                      |     |                  |          |         |

|                                          |                           | $R_{AB} = 10 \ k\Omega$                                                             |     | 3                |          | μs      |

|                                          |                           | $R_{AB} = 80 \ k\Omega$                                                             |     | 12               |          | μs      |

| Resistor Noise Density                   | e <sub>N_WB</sub>         | Code = half scale, $T_A = 25^{\circ}C$ ,<br>f = 100 kHz                             |     |                  |          |         |

|                                          |                           | $R_{AB} = 10 \text{ k}\Omega$                                                       |     | 9                |          | nV/√Hz  |

|                                          |                           | $R_{AB} = 80 \text{ k}\Omega$                                                       |     | 20               |          | nV/√Hz  |

| FLASH/EE MEMORY RELIABILITY <sup>3</sup> |                           |                                                                                     |     |                  |          |         |

| Endurance <sup>10</sup>                  |                           | $T_A = 25^{\circ}C$                                                                 |     | 1                |          | MCycles |

|                                          |                           |                                                                                     | 100 |                  |          | kCycles |

| Data Retention <sup>11</sup>             |                           |                                                                                     |     | 50               |          | Years   |

<sup>1</sup> Typical values represent average readings at 25°C,  $V_{DD} = 5 V$ ,  $V_{SS} = 0 V$ , and  $V_{LOGIC} = 5 V$ .

<sup>2</sup> Resistor position nonlinearity error (R-INL) is the deviation from an ideal value measured between the maximum resistance and the minimum resistance wiper

positions. R-DNL measures the relative step change from ideal between successive tap positions. The maximum wiper current is limited to  $0.75 \times V_{DO}/R_{AB}$ .

<sup>3</sup> Guaranteed by design and characterization, not subject to production test.

<sup>4</sup> INL and DNL are measured at V<sub>WB</sub> with the RDAC configured as a potentiometer divider similar to a voltage output DAC. V<sub>A</sub> = V<sub>DD</sub> and V<sub>B</sub> = 0 V. DNL specification limits of ±1 LSB maximum are guaranteed monotonic operating conditions.

<sup>5</sup> Resistor Terminal A, Resistor Terminal B, and Resistor Terminal W have no limitations on polarity with respect to each other.

$^6$  Different from operating current; supply current for NVM program lasts approximately 30 ms.  $^7$  Different from operating current; supply current for NVM read lasts approximately 20  $\mu s.$

<sup>8</sup> P<sub>DISS</sub> is calculated from  $(I_{DD} \times V_{DD}) + (I_{LOGIC} \times V_{LOGIC})$ . <sup>9</sup> All dynamic characteristics use  $V_{DD} = 5.5$  V, and  $V_{LOGIC} = 5$  V. <sup>10</sup> Endurance is qualified at 100,000 cycles per JEDEC Standard 22, Method A117 and measured at 150°C.

<sup>11</sup> Retention lifetime equivalent at junction temperature (T<sub>j</sub>) = 125°C per JEDEC Standard 22, Method A117. Retention lifetime based on an activation energy of 1 eV derates with junction temperature in the Flash/EE memory.

### ELECTRICAL CHARACTERISTICS—AD5112

5 kΩ, 10 kΩ, and 80 kΩ versions:  $V_{DD}$  = 2.3 V to 5.5 V,  $V_{LOGIC}$  = 1.8 V to  $V_{DD}$ ,  $V_A$  =  $V_{DD}$ ,  $V_B$  = 0 V, -40°C <  $T_A$  < +125°C, unless otherwise noted.

| Table | 3. |

|-------|----|

|       |    |

| Parameter                                            | Symbol                                        | <b>Test Conditions/Comments</b>                                           | Min                    | Typ¹  | Мах                           | Unit   |

|------------------------------------------------------|-----------------------------------------------|---------------------------------------------------------------------------|------------------------|-------|-------------------------------|--------|

| DC CHARACTERISTICS—RHEOSTAT MODE                     |                                               |                                                                           |                        |       |                               |        |

| Resolution                                           | Ν                                             |                                                                           | 6                      |       |                               | Bits   |

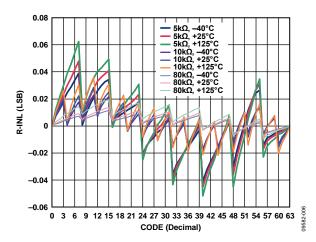

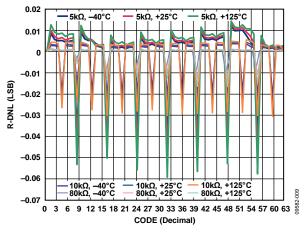

| Resistor Integral Nonlinearity <sup>2</sup>          | R-INL                                         | $R_{AB} = 5 \text{ k}\Omega$ , $V_{DD} = 2.3 \text{ V}$ to 2.7 V          | -2.5                   | ±0.5  | +2.5                          | LSB    |

|                                                      |                                               | $R_{AB} = 5 \text{ k}\Omega$ , $V_{DD} = 2.7 \text{ V to } 5.5 \text{ V}$ | -1                     | ±0.25 | +1                            | LSB    |

|                                                      |                                               | $R_{AB} = 10 \ k\Omega$                                                   | -1                     | ±0.25 | +1                            | LSB    |

|                                                      |                                               | $R_{AB} = 80 \ k\Omega$                                                   | -0.25                  | ±0.1  | +0.25                         | LSB    |

| Resistor Differential Nonlinearity <sup>2</sup>      | R-DNL                                         |                                                                           | +1                     | ±0.25 | +1                            | LSB    |

| Nominal Resistor Tolerance                           | $\Delta R_{AB}/R_{AB}$                        |                                                                           | -8                     |       | +8                            | %      |

| Resistance Temperature Coefficient <sup>3</sup>      | $(\Delta R_{AB}/R_{AB})/\Delta T \times 10^6$ | Code = full scale                                                         |                        | 35    |                               | ppm/°C |

| Wiper Resistance                                     | R <sub>w</sub>                                | Code = zero scale                                                         |                        | 70    | 140                           | Ω      |

|                                                      | R <sub>BS</sub>                               | Code = bottom scale                                                       |                        | 45    | 80                            | Ω      |

|                                                      | R <sub>TS</sub>                               | Code = top scale                                                          |                        | 70    | 140                           | Ω      |

| DC CHARACTERISTICS—POTENTIOMETER<br>DIVIDER MODE     |                                               |                                                                           |                        |       |                               |        |

| Integral Nonlinearity <sup>4</sup>                   | INL                                           |                                                                           | -0.5                   | ±0.15 | +0.5                          | LSB    |

| Differential Nonlinearity <sup>4</sup>               | DNL                                           |                                                                           | -0.5                   | ±0.15 | +0.5                          | LSB    |

| Full-Scale Error                                     | V <sub>WFSE</sub>                             | $R_{AB} = 5 k\Omega$                                                      | -2.5                   |       |                               | LSB    |

|                                                      | in se                                         | $R_{AB} = 10 \text{ k}\Omega$                                             | -1.5                   |       |                               | LSB    |

|                                                      |                                               | $R_{AB} = 80 \text{ k}\Omega$                                             | -1                     |       |                               | LSB    |

| Zero-Scale Error                                     | V <sub>WZSE</sub>                             | $R_{AB} = 5 k\Omega$                                                      |                        |       | 1.5                           | LSB    |

|                                                      | WESE                                          | $R_{AB} = 10 \text{ k}\Omega$                                             |                        |       | 1                             | LSB    |

|                                                      |                                               | $R_{AB} = 80 \text{ k}\Omega$                                             |                        |       | 0.25                          | LSB    |

| Voltage Divider Temperature Coefficient <sup>3</sup> | $(\Delta V_w/V_w)/\Delta T \times 10^6$       | Code = half scale                                                         |                        | ±10   |                               | ppm/°C |

| RESISTOR TERMINALS                                   |                                               |                                                                           |                        |       |                               |        |

| Maximum Continuous $I_A$ , $I_B$ , and $I_W$         |                                               | $R_{AB} = 5$ kΩ, 10 kΩ                                                    | -6                     |       | +6                            | mA     |

| Current <sup>3</sup>                                 |                                               | $R_{AB} = 80 \text{ k}\Omega$                                             | -1.5                   |       | +1.5                          | mA     |

| Terminal Voltage Range⁵                              |                                               | AD                                                                        | GND                    |       | V <sub>DD</sub>               | v      |

| Capacitance A, Capacitance B <sup>3</sup>            | C <sub>A</sub> , C <sub>B</sub>               | f = 1 MHz, measured to GND,                                               |                        | 20    | bb                            | рF     |

|                                                      |                                               | code = half scale, $V_W = V_A =$<br>2.5 V or $V_W = V_B =$ 2.5 V          |                        |       |                               |        |

| Capacitance W <sup>3</sup>                           | C <sub>w</sub>                                | f = 1 MHz, measured to GND,<br>code = half scale,                         |                        | 35    |                               | pF     |

|                                                      |                                               | $V_{A} = V_{B} = 2.5 V$                                                   |                        |       |                               |        |

| Common-Mode Leakage Current <sup>3</sup>             |                                               | $V_A = V_W = V_B$                                                         | -500                   | ±15   | +500                          | nA     |

| DIGITAL INPUTS                                       |                                               |                                                                           |                        |       |                               |        |

| Input Logic <sup>3</sup>                             |                                               |                                                                           |                        |       |                               |        |

| High                                                 | V <sub>INH</sub>                              | $V_{LOGIC} = 1.8 V \text{ to } 2.3 V$                                     | $0.8 \times V_{LOGIC}$ |       |                               | V      |

|                                                      |                                               | $V_{LOGIC} = 2.3 V \text{ to } 5.5 V$                                     | $0.7 \times V_{LOGIC}$ |       |                               | V      |

| Low                                                  | V <sub>INL</sub>                              | $V_{LOGIC} = 1.8 \text{ V} \text{ to } 2.3 \text{ V}$                     |                        |       | $0.2 \times V_{\text{logic}}$ | V      |

|                                                      |                                               | $V_{LOGIC} = 2.3 \text{ V} \text{ to } 5.5 \text{ V}$                     |                        |       | $0.3 	imes V_{\text{LOGIC}}$  | V      |

| Input Hysteresis <sup>3</sup>                        | V <sub>HYST</sub>                             |                                                                           | $0.1 \times V_{LOGIC}$ |       |                               | V      |

| Input Current <sup>3</sup>                           | I <sub>N</sub>                                |                                                                           |                        |       | ±1                            | μA     |

| Input Capacitance <sup>3</sup>                       | C <sub>IN</sub>                               |                                                                           |                        | 5     |                               | pF     |

| DIGITAL OUTPUT (SDA)                                 |                                               |                                                                           |                        |       |                               |        |

| Output Low Voltage <sup>3</sup>                      | V <sub>oL</sub>                               | $I_{SINK} = 3 \text{ mA}$                                                 |                        |       | 0.2                           | V      |

| · -                                                  |                                               | $I_{SINK} = 6 \text{ mA}$                                                 |                        |       | 0.4                           | V      |

| Three-State Leakage Current                          |                                               |                                                                           | -1                     |       | +1                            | μA     |

| Three-State Output Capacitance <sup>3</sup>          |                                               |                                                                           |                        | 2     |                               | pF     |

| Parameter                                | Symbol                    | Test Conditions/Comments                                                         | Min | <b>Typ</b> <sup>1</sup> | Max      | Unit    |

|------------------------------------------|---------------------------|----------------------------------------------------------------------------------|-----|-------------------------|----------|---------|

| POWER SUPPLIES                           |                           |                                                                                  |     |                         |          |         |

| Single-Supply Power Range                |                           |                                                                                  | 2.3 |                         | 5.5      | V       |

| Logic Supply Range                       |                           |                                                                                  | 1.8 |                         | $V_{DD}$ | V       |

| Positive Supply Current                  | I <sub>DD</sub>           | $V_{DD} = 5 V$                                                                   |     | 0.75                    | 3.5      | μΑ      |

|                                          |                           | $V_{DD} = 2.7 V$                                                                 |     |                         | 2.5      | μΑ      |

|                                          |                           | $V_{DD} = 2.3 V$                                                                 |     |                         | 2.4      | μΑ      |

| EEMEM Store Current <sup>3, 6</sup>      | I <sub>DD_NVM_STORE</sub> |                                                                                  |     | 2                       |          | mA      |

| EEMEM Read Current <sup>3, 7</sup>       | I <sub>DD_NVM_READ</sub>  |                                                                                  |     | 320                     |          | μΑ      |

| Logic Supply Current                     | I <sub>LOGIC</sub>        | $V_{IH} = V_{LOGIC}$ or $V_{IL} = GND$                                           |     | 30                      |          | nA      |

| Power Dissipation <sup>8</sup>           | P <sub>DISS</sub>         | $V_{IH} = V_{LOGIC}$ or $V_{IL} = GND$                                           |     | 5                       |          | μW      |

| Power Supply Rejection <sup>3</sup>      | PSR                       | $\Delta V_{DD} / \Delta V_{SS} = 5 V \pm 10\%$                                   |     |                         |          |         |

|                                          |                           | $R_{AB} = 5 k\Omega$                                                             |     | -43                     |          | dB      |

|                                          |                           | $R_{AB} = 10 k\Omega$                                                            |     | -50                     |          | dB      |

|                                          |                           | $R_{AB} = 80 \text{ k}\Omega$                                                    |     | -64                     |          | dB      |

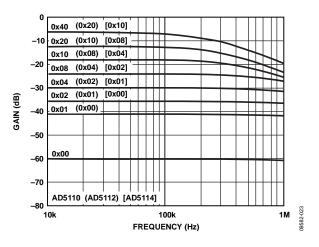

| DYNAMIC CHARACTERISTICS <sup>3, 9</sup>  |                           |                                                                                  |     |                         |          |         |

| Bandwidth                                | BW                        | Code = half scale – 3 dB                                                         |     |                         |          |         |

|                                          |                           | $R_{AB} = 5 k\Omega$                                                             |     | 4                       |          | MHz     |

|                                          |                           | $R_{AB} = 10 k\Omega$                                                            |     | 2                       |          | MHz     |

|                                          |                           | $R_{AB} = 80 \ k\Omega$                                                          |     | 200                     |          | kHz     |

| Total Harmonic Distortion                | THD                       | $V_A = V_{DD}/2 + 1 V rms,$<br>$V_B = V_{DD}/2, f = 1 kHz,$<br>code = half scale |     |                         |          |         |

|                                          |                           | $R_{AB} = 5 k\Omega$                                                             |     | -75                     |          | dB      |

|                                          |                           | $R_{AB} = 10 k\Omega$                                                            |     | -80                     |          | dB      |

|                                          |                           | $R_{AB} = 80 \text{ k}\Omega$                                                    |     | -85                     |          | dB      |

| $V_w$ Settling Time                      | t <sub>s</sub>            | $V_A = 5 V, V_B = 0 V,$<br>±0.5 LSB error band                                   |     |                         |          | μs      |

|                                          |                           | $R_{AB} = 5 k\Omega$                                                             |     | 2.5                     |          | μs      |

|                                          |                           | $R_{AB} = 10 \text{ k}\Omega$                                                    |     | 3                       |          | μs      |

|                                          |                           | $R_{AB} = 80 \text{ k}\Omega$                                                    |     | 10                      |          | μs      |

| Resistor Noise Density                   | e <sub>N_WB</sub>         | Code = half scale, $T_A = 25^{\circ}C$ ,<br>f = 100 kHz                          |     |                         |          |         |

|                                          |                           | $R_{AB} = 5 k\Omega$                                                             |     | 7                       |          | nV/√Hz  |

|                                          |                           | $R_{AB} = 10 \text{ k}\Omega$                                                    |     | 9                       |          | nV/√Hz  |

|                                          |                           | $R_{AB} = 80 \text{ k}\Omega$                                                    |     | 20                      |          | nV/√Hz  |

| FLASH/EE MEMORY RELIABILITY <sup>3</sup> |                           |                                                                                  |     |                         |          |         |

| Endurance <sup>10</sup>                  |                           | $T_A = 25^{\circ}C$                                                              |     | 1                       |          | MCycles |

|                                          |                           |                                                                                  | 100 |                         |          | kCycles |

| Data Retention <sup>11</sup>             |                           |                                                                                  |     | 50                      |          | Years   |

<sup>1</sup> Typical values represent average readings at 25°C,  $V_{DD}$  = 5 V,  $V_{SS}$  = 0 V, and  $V_{LOGIC}$  = 5 V. <sup>2</sup> Resistor position nonlinearity error (R-INL) is the deviation from an ideal value measured between the maximum resistance and the minimum resistance wiper positions. R-DNL measures the relative step change from ideal between successive tap positions. The maximum wiper current is limited to  $0.75 \times V_{DD}/R_{AB}$ . <sup>3</sup> Guaranteed by design and characterization, not subject to production test.

$^{4}$  INL and DNL are measured at V<sub>WB</sub> with the RDAC configured as a potentiometer divider similar to a voltage output DAC. V<sub>A</sub> = V<sub>DD</sub> and V<sub>B</sub> = 0 V. DNL specification limits of ±1 LSB maximum are guaranteed monotonic operating conditions.

<sup>5</sup> Resistor Terminal A, Resistor Terminal B, and Resistor Terminal W have no limitations on polarity with respect to each other.

<sup>6</sup> Different from operating current; supply current for NVM program lasts approximately 30 ms. <sup>7</sup> Different from operating current; supply current for NVM read lasts approximately 20  $\mu$ s. <sup>8</sup> P<sub>DISS</sub> is calculated from ( $I_{DD} \times V_{DD}$ ) + ( $I_{LOGIC} \times V_{LOGIC}$ ). <sup>9</sup> All dynamic characteristics use  $V_{DD}$  = 5.5 V, and  $V_{LOGIC}$  = 5 V. <sup>10</sup> Endurance is qualified at 100,000 cycles per JEDEC Standard 22, Method A117 and measured at 150°C.

<sup>11</sup> Retention lifetime equivalent at junction temperature (T<sub>i</sub>) = 125°C per JEDEC Standard 22, Method A117. Retention lifetime based on an activation energy of 1 eV derates with junction temperature in the Flash/EE memory.

### ELECTRICAL CHARACTERISTICS—AD5114

10 k $\Omega$  and 80 k $\Omega$  versions:  $V_{DD}$  = 2.3 V to 5.5 V,  $V_{LOGIC}$  = 1.8 V to  $V_{DD}$ ,  $V_A$  =  $V_{DD}$ ,  $V_B$  = 0 V, -40°C <  $T_A$  < +125°C, unless otherwise noted.

| Table 4.                                             | 1                                               | T                                                                                               |                               |                         |                               | T      |

|------------------------------------------------------|-------------------------------------------------|-------------------------------------------------------------------------------------------------|-------------------------------|-------------------------|-------------------------------|--------|

| Parameter                                            | Symbol                                          | Test Conditions/Comments                                                                        | Min                           | <b>Typ</b> <sup>1</sup> | Max                           | Unit   |

| DC CHARACTERISTICS—RHEOSTAT MODE                     |                                                 |                                                                                                 |                               |                         |                               |        |

| Resolution                                           | Ν                                               |                                                                                                 | 5                             |                         |                               | Bits   |

| Resistor Integral Nonlinearity <sup>2</sup>          | R-INL                                           |                                                                                                 | -0.5                          |                         | +0.5                          | LSB    |

| Resistor Differential Nonlinearity <sup>2</sup>      | R-DNL                                           |                                                                                                 | -0.25                         |                         | +0.25                         | LSB    |

| Nominal Resistor Tolerance                           | $\Delta R_{AB}/R_{AB}$                          |                                                                                                 | -8                            |                         | +8                            | %      |

| Resistance Temperature Coefficient <sup>3</sup>      | $(\Delta R_{AB}/R_{AB})/\Delta T \times 10^{6}$ | Code = full scale                                                                               |                               | 35                      |                               | ppm/°C |

| Wiper Resistance                                     | R <sub>w</sub>                                  | Code = zero scale                                                                               |                               | 70                      | 140                           | Ω      |

|                                                      | R <sub>BS</sub>                                 | Code = bottom scale                                                                             |                               | 45                      | 80                            | Ω      |

|                                                      | R <sub>TS</sub>                                 | Code = top scale                                                                                |                               | 70                      | 140                           | Ω      |

| DC CHARACTERISTICS—POTENTIOMETER<br>DIVIDER MODE     |                                                 |                                                                                                 |                               |                         |                               |        |

| Integral Nonlinearity <sup>4</sup>                   | INL                                             |                                                                                                 | -0.25                         |                         | +0.25                         | LSB    |

| Differential Nonlinearity <sup>4</sup>               | DNL                                             |                                                                                                 | -0.25                         |                         | +0.25                         | LSB    |

| Full-Scale Error                                     | V <sub>WFSE</sub>                               | $R_{AB} = 10 \ k\Omega$                                                                         | -1                            |                         |                               | LSB    |

|                                                      |                                                 | $R_{AB} = 80 \ k\Omega$                                                                         | -0.5                          |                         |                               | LSB    |

| Zero-Scale Error                                     | V <sub>WZSE</sub>                               | $R_{AB} = 10 \ k\Omega$                                                                         |                               |                         | 1                             | LSB    |

|                                                      |                                                 | $R_{AB} = 80 \ k\Omega$                                                                         |                               |                         | 0.25                          | LSB    |

| Voltage Divider Temperature Coefficient <sup>3</sup> | $(\Delta V_w/V_w)/\Delta T \times 10^6$         | Code = half scale                                                                               |                               | ±10                     |                               | ppm/°C |

| RESISTOR TERMINALS                                   |                                                 |                                                                                                 |                               |                         |                               |        |

| Maximum Continuous $I_A$ , $I_B$ , and $I_W$         |                                                 | $R_{AB} = 10 \ k\Omega$                                                                         | -6                            |                         | +6                            | mA     |

| Current <sup>3</sup>                                 |                                                 | $R_{AB} = 80 \ k\Omega$                                                                         | -1.5                          |                         | +1.5                          | mA     |

| Terminal Voltage Range⁵                              |                                                 |                                                                                                 | GND                           |                         | V <sub>DD</sub>               | V      |

| Capacitance A, Capacitance B <sup>3</sup>            | C <sub>A</sub> , C <sub>B</sub>                 | f = 1 MHz, measured to GND,<br>code = half scale, $V_W = V_A =$<br>2.5 V or $V_W = V_B = 2.5$ V |                               | 20                      |                               | pF     |

| Capacitance W <sup>3</sup>                           | C <sub>w</sub>                                  | f = 1 MHz, measured to<br>GND, code = half scale, $V_A = V_B = 2.5$ V                           |                               | 35                      |                               | pF     |

| Common-Mode Leakage Current <sup>3</sup>             |                                                 | $V_A = V_W = V_B$                                                                               | -500                          | ±15                     | +500                          | nA     |

| DIGITAL INPUTS                                       |                                                 |                                                                                                 |                               |                         |                               |        |

| Input Logic <sup>3</sup>                             |                                                 |                                                                                                 |                               |                         |                               |        |

| High                                                 | V <sub>INH</sub>                                | $V_{LOGIC} = 1.8 V \text{ to } 2.3 V$                                                           | $0.8 \times V_{LOGIC}$        |                         |                               | V      |

|                                                      |                                                 | $V_{LOGIC} = 2.3 \text{ V to } 5.5 \text{ V}$                                                   | $0.7 \times V_{LOGIC}$        |                         |                               | V      |

| Low                                                  | V <sub>INL</sub>                                | $V_{LOGIC} = 1.8 \text{ V to } 2.3 \text{ V}$                                                   |                               |                         | $0.2 \times V_{\text{LOGIC}}$ | V      |

|                                                      |                                                 | $V_{LOGIC} = 2.3 \text{ V to } 5.5 \text{ V}$                                                   |                               |                         | $0.3 \times V_{LOGIC}$        | V      |

| Input Hysteresis <sup>3</sup>                        | V <sub>HYST</sub>                               |                                                                                                 | $0.1 \times V_{\text{LOGIC}}$ |                         |                               | V      |

| Input Current <sup>3</sup>                           | I <sub>N</sub>                                  |                                                                                                 |                               |                         | ±1                            | μA     |

| Input Capacitance <sup>3</sup>                       | C <sub>IN</sub>                                 |                                                                                                 |                               | 5                       |                               | pF     |

| DIGITAL OUTPUT (SDA)                                 |                                                 |                                                                                                 |                               |                         |                               |        |

| Output Low Voltage <sup>3</sup>                      | V <sub>OL</sub>                                 | $I_{SINK} = 3 \text{ mA}$                                                                       |                               |                         | 0.2                           | V      |

|                                                      |                                                 | $I_{SINK} = 6 \text{ mA}$                                                                       |                               |                         | 0.4                           | v      |

| Three-State Leakage Current                          |                                                 |                                                                                                 | -1                            |                         | +1                            | μA     |

| Three-State Output Capacitance <sup>3</sup>          |                                                 |                                                                                                 |                               | 2                       |                               | pF     |

| Parameter                                | Symbol                    | <b>Test Conditions/Comments</b>                                | Min | Typ <sup>1</sup> | Max      | Unit             |

|------------------------------------------|---------------------------|----------------------------------------------------------------|-----|------------------|----------|------------------|

| POWER SUPPLIES                           |                           |                                                                |     |                  |          |                  |

| Single-Supply Power Range                |                           |                                                                | 2.3 |                  | 5.5      | V                |

| Logic Supply Range                       |                           |                                                                | 1.8 |                  | $V_{DD}$ | V                |

| Positive Supply Current                  | I <sub>DD</sub>           | $V_{DD} = 5 V$                                                 |     | 0.75             | 3.5      | μA               |

|                                          |                           | $V_{DD} = 2.7 V$                                               |     |                  | 2.5      | μA               |

|                                          |                           | $V_{DD} = 2.3 V$                                               |     |                  | 2.4      | μA               |

| EEMEM Store Current <sup>3, 6</sup>      | I <sub>DD_NVM_STORE</sub> |                                                                |     | 2                |          | mA               |

| EEMEM Read Current <sup>3, 7</sup>       | I <sub>DD_NVM_READ</sub>  |                                                                |     | 320              |          | μA               |

| Logic Supply Current                     | I <sub>LOGIC</sub>        | $V_{IH} = V_{LOGIC}$ or $V_{IL} = GND$                         |     | 30               |          | nA               |

| Power Dissipation <sup>8</sup>           | P <sub>DISS</sub>         | $V_{IH} = V_{LOGIC}$ or $V_{IL} = GND$                         |     | 5                |          | μW               |

| Power Supply Rejection <sup>3</sup>      | PSR                       | $\Delta V_{DD} / \Delta V_{SS} = 5 V \pm 10\%$                 |     |                  |          |                  |

|                                          |                           | $R_{AB} = 10 \ k\Omega$                                        |     | -50              |          | dB               |

|                                          |                           | $R_{AB} = 80 \text{ k}\Omega$                                  |     | -64              |          | dB               |

| DYNAMIC CHARACTERISTICS <sup>3, 9</sup>  |                           |                                                                |     |                  |          |                  |

| Bandwidth                                | BW                        | Code = half scale, -3 dB                                       |     |                  |          |                  |

|                                          |                           | $R_{AB} = 10 \ k\Omega$                                        |     | 2                |          | MHz              |

|                                          |                           | $R_{AB} = 80 \text{ k}\Omega$                                  |     | 200              |          | kHz              |

| Total Harmonic Distortion                | THD                       | $V_{A} = V_{DD}/2 + 1 V rms,$                                  |     |                  |          |                  |

|                                          |                           | $V_{\rm B} = V_{\rm DD}/2$ , f = 1 kHz,                        |     |                  |          |                  |

|                                          |                           | code = half scale                                              |     |                  |          |                  |

|                                          |                           | $R_{AB} = 10 k\Omega$                                          |     | -80              |          | dB               |

|                                          |                           | $R_{AB} = 80 \ k\Omega$                                        |     | -85              |          | dB               |

| V <sub>w</sub> Settling Time             | t <sub>s</sub>            | $V_{A} = 5 V, V_{B} = 0 V, \pm 0.5 LSB$                        |     |                  |          |                  |

|                                          |                           | error band                                                     |     | 2.7              |          |                  |

|                                          |                           | $R_{AB} = 10 k\Omega$                                          |     | 2.7              |          | μs               |

|                                          |                           | $R_{AB} = 80 \text{ k}\Omega$                                  |     | 9.5              |          | μs               |

| Resistor Noise Density                   | e <sub>N_WB</sub>         | Code = half scale, $T_A = 25^{\circ}C$ ,<br>f = 100 kHz        |     |                  |          |                  |

|                                          |                           | $R_{AB} = 10 \text{ k}\Omega$                                  |     | 9                |          | nV/√Hz           |

|                                          |                           | $R_{AB} = 10 \text{ K}\Omega$<br>$R_{AB} = 80 \text{ k}\Omega$ |     | 9<br>20          |          | nV/√Hz           |

| FLASH/EE MEMORY RELIABILITY <sup>3</sup> |                           | N <sub>AB</sub> - 60 K2                                        |     | 20               |          |                  |

|                                          |                           |                                                                |     | 1                |          | Mousta           |

| Endurance <sup>10</sup>                  |                           | $T_A = 25^{\circ}C$                                            | 100 | 1                |          | MCycles          |

| Data Retention <sup>11</sup>             |                           |                                                                | 100 | 50               |          | kCycles<br>Voars |

| Data netention                           |                           |                                                                |     | 50               |          | Years            |

<sup>1</sup> Typical values represent average readings at 25°C,  $V_{DD}$  = 5 V,  $V_{SS}$  = 0 V, and  $V_{LOGIC}$  = 5 V. <sup>2</sup> Resistor position nonlinearity error (R-INL) is the deviation from an ideal value measured between the maximum resistance and the minimum resistance wiper positions. R-DNL measures the relative step change from ideal between successive tap positions. The maximum wiper current is limited to  $0.75 \times V_{DD}/R_{AB}$ .

<sup>3</sup> Guaranteed by design and characterization, not subject to production test. <sup>4</sup> INL and DNL are measured at  $V_{WB}$  with the RDAC configured as a potentiometer divider similar to a voltage output DAC.  $V_A = V_{DD}$  and  $V_B = 0$  V. DNL specification limits of ±1 LSB maximum are guaranteed monotonic operating conditions.

<sup>5</sup> Resistor Terminal A, Resistor Terminal B, and Resistor Terminal W have no limitations on polarity with respect to each other.

<sup>6</sup> Different from operating current; supply current for NVM program lasts approximately 30 ms.

<sup>7</sup> Different from operating current; supply current for NVM program has approximately 50 ms. <sup>8</sup> P<sub>Diss</sub> is calculated from  $(I_{box} \times V_{po}) + (I_{LOGIC} \times V_{LOGIC})$ . <sup>9</sup> All dynamic characteristics use  $V_{DD} = 5.5$  V, and  $V_{LOGIC} = 5$  V. <sup>10</sup> Endurance is qualified at 100,000 cycles per JEDEC Standard 22, Method A117 and measured at 150°C.

<sup>11</sup> Retention lifetime equivalent at junction temperature (T<sub>i</sub>) = 125°C per JEDEC Standard 22, Method A117. Retention lifetime based on an activation energy of 1 eV derates with junction temperature in the Flash/EE memory.

### INTERFACE TIMING SPECIFICATIONS

$\rm V_{LOGIC}$  = 1.8 V to 5.5 V; all specifications  $\rm T_{MIN}$  to  $\rm T_{MAX}$  , unless otherwise noted.

#### Table 5.

|                                          | Test Conditions/ |                         |     |      |      |                                                                       |

|------------------------------------------|------------------|-------------------------|-----|------|------|-----------------------------------------------------------------------|

| Parameter <sup>1</sup>                   | Comments         | Min                     | Тур | Max  | Unit | Description                                                           |

| f <sub>SCL</sub> <sup>2</sup>            | Standard mode    |                         |     | 100  | kHz  | Serial clock frequency                                                |

|                                          | Fast mode        |                         |     | 400  | kHz  |                                                                       |

| t <sub>1</sub>                           | Standard mode    | 4.0                     |     |      | μs   | t <sub>HIGH</sub> , SCL high time                                     |

|                                          | Fast mode        | 0.6                     |     |      | μs   |                                                                       |

| t <sub>2</sub>                           | Standard mode    | 4.7                     |     |      | μs   | t <sub>LOW</sub> , SCL low time                                       |

|                                          | Fast mode        | 1.3                     |     |      | μs   |                                                                       |

| t <sub>3</sub>                           | Standard mode    | 250                     |     |      | ns   | t <sub>su;DAT</sub> , data setup time                                 |

|                                          | Fast mode        | 100                     |     |      | ns   |                                                                       |

| t <sub>4</sub>                           | Standard mode    | 0                       |     | 3.45 | μs   | t <sub>HD;DAT</sub> , data hold time                                  |

|                                          | Fast mode        | 0                       |     | 0.9  | μs   |                                                                       |

| t <sub>5</sub>                           | Standard mode    | 4.7                     |     |      | μs   | $t_{SU;STA'}$ setup time for a repeated start condition               |

|                                          | Fast mode        | 0.6                     |     |      | μs   |                                                                       |

| t <sub>6</sub>                           | Standard mode    | 4                       |     |      | μs   | t <sub>HD;STA</sub> , hold time (repeated) start condition            |

|                                          | Fast mode        | 0.6                     |     |      | μs   |                                                                       |

| t <sub>7</sub>                           | Standard mode    | 4.7                     |     |      | μs   | t <sub>BUF</sub> , bus free time between a stop and a start condition |

|                                          | Fast mode        | 1.3                     |     |      | μs   |                                                                       |

| t <sub>8</sub>                           | Standard mode    | 4                       |     |      | μs   | t <sub>su;sto</sub> , setup time for stop condition                   |

|                                          | Fast mode        | 0.6                     |     |      | μs   |                                                                       |

| t <sub>9</sub>                           | Standard mode    |                         |     | 1000 | ns   | t <sub>RDA</sub> , rise time of SDA signal                            |

|                                          | Fast mode        | $20 + 0.1 C_{L}$        |     | 300  | ns   |                                                                       |

| t <sub>10</sub>                          | Standard mode    |                         |     | 300  | ns   | t <sub>FDA</sub> , fall time of SDA signal                            |

|                                          | Fast mode        | $20 + 0.1 C_{L}$        |     | 300  | ns   |                                                                       |

| t <sub>11</sub>                          | Standard mode    |                         |     | 1000 | ns   | t <sub>RCL</sub> , rise time of SCL signal                            |

|                                          | Fast mode        | $20 + 0.1 C_{L}$        |     | 300  | ns   |                                                                       |

| t <sub>11A</sub>                         | Standard mode    |                         |     | 1000 | ns   | t <sub>RCL1</sub> , rise time of SCL signal after a repeated start    |

|                                          | Fast mode        | $20 + 0.1 C_{L}$        |     | 300  | ns   | condition and after an acknowledge bit.                               |

| t <sub>12</sub>                          | Standard mode    |                         |     | 300  | ns   | t <sub>FCL</sub> , fall time of SCL signal                            |

|                                          | Fast mode        | 20 + 0.1 C <sub>L</sub> |     | 300  | ns   |                                                                       |

| t <sub>sP</sub> <sup>3</sup>             | Fast mode        | 0                       |     | 50   | ns   | Pulse width of suppressed spike                                       |

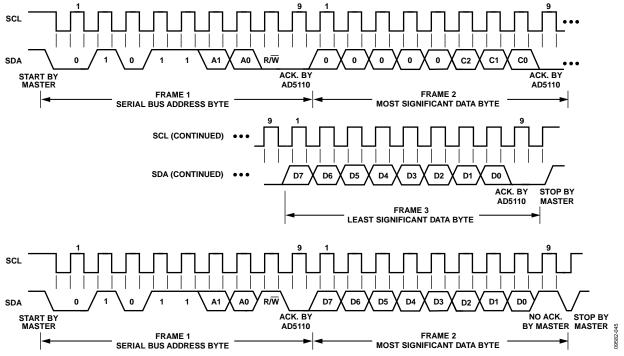

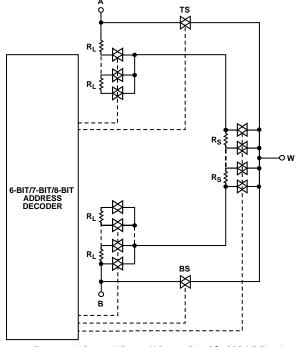

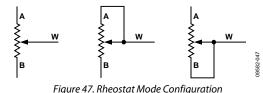

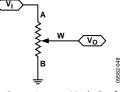

| t <sub>EEPROM_PROGRAM</sub> <sup>4</sup> |                  |                         | 15  | 50   | ms   | Memory program time                                                   |