# 16-Bit, 100 kSPS/200 kSPS BiCMOS A/D Converter

# AD977/AD977A

### FEATURES

Fast 16-Bit ADC 100 kSPS Throughput Rate—AD977 200 kSPS Throughput Rate—AD977A Single 5 V Supply Operation Power Dissipation 100 mW Max Power-Down Mode 50 μW Input Ranges: Unipolar; 0 V–10 V, 0 V–5 V and 0 V–4 V Bipolar; ±10 V, ±5 V and ±3.3 V Choice of External or Internal 2.5 V Reference High Speed Serial Interface On-Chip Clock 20-Lead Skinny DIP or SOIC Package 28-Lead Skinny SSOP Package

#### **GENERAL DESCRIPTION**

The AD977/AD977A is a high speed, low power 16-bit A/D converter that operates from a single 5 V supply. The AD977A has a throughput rate of 200 kSPS whereas the AD977 has a throughput rate of 100 kSPS. Each part contains a successive approximation, switched capacitor ADC, an internal 2.5 V reference, and a high speed serial interface. The ADC is factory calibrated to minimize all linearity errors. The AD977/AD977A is specified for full scale bipolar input ranges of  $\pm 10$  V,  $\pm 5$  V and  $\pm 3.3$  V, and unipolar ranges of 0 V to 10 V, 0 V to 5 V and 0 V to 4 V.

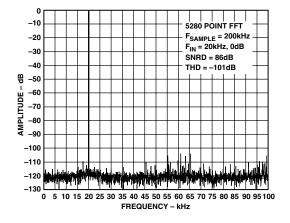

The AD977/AD977A is comprehensively tested for ac parameters such as SNR and THD, as well as the more traditional dc parameters of offset, gain and linearity.

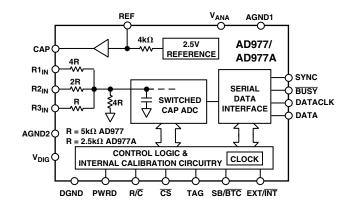

### FUNCTIONAL BLOCK DIAGRAM

#### **PRODUCT HIGHLIGHTS**

- 1. Fast Throughput The AD977/AD977A is a high speed, 16-bit ADC based on a factory calibrated switched capacitor architecture.

- Single-Supply Operation The AD977/AD977A operates from a single 5 V supply and dissipates only 100 mW max.

- 3. Comprehensive DC and AC Specifications In addition to the traditional specifications of offset, gain and linearity, the AD977/AD977A is fully tested for SNR and THD.

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

# AD977/AD977A **AD977—SPECIFICATIONS** (-40°C to +85°C, $F_s = 100$ kHz, $V_{DIG} = V_{ANA} = 5$ V, unless otherwise noted)

| Parameter                                                                                                                                                                                  | Min      | A Grade<br>Typ | Max              | ]<br>Min                | B Grade<br>Typ | Max                    | Min      | C Grade<br>Typ              | e<br>Max | Unit                                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------------|------------------|-------------------------|----------------|------------------------|----------|-----------------------------|----------|-------------------------------------------------------|

| RESOLUTION                                                                                                                                                                                 | 16       |                |                  | 16                      |                |                        | 16       |                             |          | Bits                                                  |

| ANALOG INPUT<br>Voltage Range<br>Impedance                                                                                                                                                 |          |                | ±1               | 0 V, 0 V to<br>  See Ta | able II        | . (See Table II)       |          |                             |          |                                                       |

| Sampling Capacitance                                                                                                                                                                       |          | 40             |                  |                         | 40             |                        |          | 40                          |          | pF                                                    |

| THROUGHPUT SPEED<br>Complete Cycle<br>Throughput Rate                                                                                                                                      | 100      |                | 10               | 100                     |                | 10                     | 100      |                             | 10       | μs<br>kHz                                             |

| DC ACCURACY<br>Integral Linearity Error<br>Differential Linearity Error<br>No Missing Codes<br>Transition Noise <sup>2</sup><br>Full-Scale Error <sup>3, 4</sup><br>Full-Scale Error Drift | -2<br>15 | 1.0<br>±7      | ±3<br>+3<br>±0.5 | -1<br>16                | 1.0<br>±7      | ±2.0<br>+1.75<br>±0.25 |          | ±3<br>±2<br>15<br>1.0<br>±7 | ±0.5     | LSB <sup>1</sup><br>LSB<br>Bits<br>LSB<br>%<br>ppm/°C |

| Full-Scale Error<br>Ext. REF = 2.5 V<br>Full-Scale Error Drift                                                                                                                             |          |                | ±0.5             |                         |                | ±0.25                  |          |                             | ±0.5     | %                                                     |

| Ext. REF = 2.5 V<br>Bipolar Zero Error <sup>3</sup>                                                                                                                                        |          | ±2             | 110              |                         | ±2             | 110                    |          | ±2                          | .15      | ppm/°C                                                |

| Bipolar Ranges<br>Bipolar Zero Error Drift<br>Bipolar Ranges                                                                                                                               |          | ±2             | ±10              |                         | ±2             | ±10                    |          | ±2                          | ±15      | mV<br>ppm/°C                                          |

| Unipolar Zero Error <sup>3</sup><br>Unipolar Ranges                                                                                                                                        |          |                | ±10              |                         |                | ±10                    |          |                             | ±10      | mV                                                    |

| Unipolar Zero Error Drift<br>Unipolar Ranges<br>Recovery to Rated Accuracy                                                                                                                 |          | ±2             |                  |                         | ±2             |                        |          | ±2                          |          | ppm/°C                                                |

| After Power-Down <sup>5</sup><br>2.2 μF to CAP<br>Power Supply Sensitivity                                                                                                                 |          | 1              |                  |                         | 1              |                        |          | 1                           |          | ms                                                    |

| $V_{ANA} = V_{DIG} = V_D = 5 V \pm 5\%$                                                                                                                                                    |          |                | ±8               |                         |                | ±8                     |          |                             | ±8       | LSB                                                   |

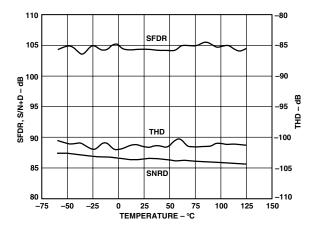

| AC ACCURACY<br>Spurious Free Dynamic Range <sup>6</sup><br>Total Harmonic Distortion <sup>6</sup><br>Signal-to-(Noise+Distortion) <sup>6</sup><br>-60 dB Input                             | 90<br>83 | 27             | -90              | 96<br>85                | 28             | -96                    | 90<br>83 | 27                          | -90      | dB <sup>7</sup><br>dB<br>dB<br>dB                     |

| Signal-to-Noise <sup>6</sup><br>Full Power Bandwidth <sup>8</sup><br>–3 dB Input Bandwidth                                                                                                 | 83       | 700<br>1.5     |                  | 85                      | 700<br>1.5     |                        | 83       | 700<br>1.5                  |          | dB<br>kHz<br>MHz                                      |

| SAMPLING DYNAMICS<br>Aperture Delay<br>Transient Response, Full-Scale Step                                                                                                                 |          | 40             | 2                |                         | 40             | 2                      |          | 40                          | 2        | ns<br>μs                                              |

| Overvoltage Recovery <sup>9</sup>                                                                                                                                                          |          | 150            |                  |                         | 150            |                        |          | 150                         |          | ns                                                    |

| REFERENCE<br>Internal Reference Voltage<br>Internal Reference Source Current<br>External Reference Voltage Range                                                                           | 2.48     | 2.5<br>1       | 2.52             | 2.48                    | 2.5<br>1       | 2.52                   | 2.48     | 2.5<br>1                    | 2.52     | ν<br>μΑ                                               |

| for Specified Linearity<br>External Reference Current Drain                                                                                                                                | 2.3      | 2.5            | 2.7              | 2.3                     | 2.5            | 2.7                    | 2.3      | 2.5                         | 2.7      | V                                                     |

| Ext. REF = 2.5 V                                                                                                                                                                           |          |                | 100              |                         |                | 100                    |          |                             | 100      | μA                                                    |

NOTES

<sup>1</sup>LSB means Least Significant Bit. With a  $\pm 10$  V input, one LSB is 305  $\mu$ V.

<sup>2</sup>Typical rms noise at worst case transitions and temperatures.

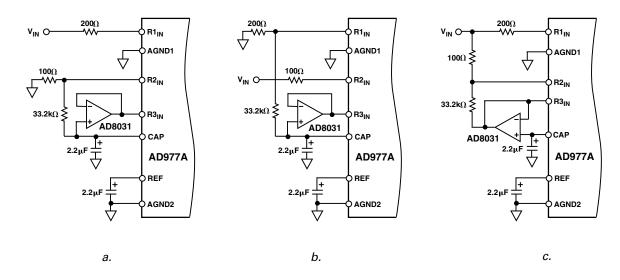

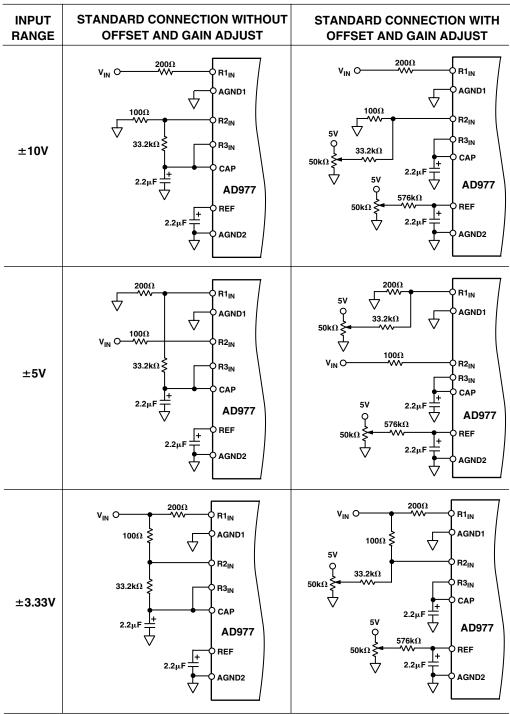

<sup>3</sup>Measured with fixed resistors as shown in Figures 11, 12 and 13. Adjustable to zero. Tested at room temperature.

<sup>4</sup>Full-Scale Error is expressed as the % difference between the actual full-scale code transition voltage and the ideal full scale transition voltage, and includes the effect of offset error. For bipolar input ranges, the Full-Scale Error is the worst case of either the -Full Scale or +Full Scale code transition voltage errors. For unipolar input ranges, Full-Scale Error is with respect to the +Full-Scale code transition voltage.

<sup>5</sup>External 2.5 V reference connected to REF.

$^{7}$ All specifications in dB are referred to a full scale ±10 V input.  $^{8}$ Full-Power Bandwidth is defined as full-scale input frequency at which Signal-to-(Noise+Distortion) degrades to 60 dB, or 10 bits of accuracy.

$^9\text{Recovers to specified performance after a <math display="inline">2\times F_S$  input overvoltage.

Specifications subject to change without notice.

# **AD977A—SPECIFICATIONS** (-40°C to +85°C, $F_s = 200$ kHz, $V_{DIG} = V_{ANA} = 5$ V, unless otherwise noted)

| Parameter                                       | Min  | A Grade<br>Typ | e<br>Max  | Min         | B Grade<br>Typ | Max            | Min  | C Grade<br>Typ | e<br>Max  | Unit             |

|-------------------------------------------------|------|----------------|-----------|-------------|----------------|----------------|------|----------------|-----------|------------------|

| RESOLUTION                                      | 16   |                |           | 16          |                |                | 16   |                |           | Bits             |

| ANALOG INPUT                                    |      |                |           |             |                |                |      |                |           |                  |

| Voltage Range                                   |      |                | ±1        | 0 V, 0 V to | 5 V,           | (See Table II) |      |                |           |                  |

| Impedance                                       |      |                |           | See Ta      | able II        |                |      |                |           |                  |

| Sampling Capacitance                            |      | 40             |           |             | 40             |                |      | 40             |           | pF               |

| THROUGHPUT SPEED                                |      |                |           |             |                |                |      |                |           |                  |

| Complete Cycle                                  |      |                | 5         |             |                | 5              |      |                | 5         | μs               |

| Throughput Rate                                 | 200  |                |           | 200         |                |                | 200  |                |           | kHz              |

| DC ACCURACY                                     |      |                |           |             |                |                |      |                |           |                  |

| Integral Linearity Error                        |      |                | ±3        |             |                | $\pm 2.0$      |      | ±3             |           | LSB <sup>1</sup> |

| Differential Linearity Error                    | -2   |                | +3        | -1          |                | +1.75          |      | $\pm 2$        |           | LSB              |

| No Missing Codes                                | 15   |                |           | 16          |                |                |      | 15             |           | Bits             |

| Transition Noise <sup>2</sup>                   |      | 1.0            |           |             | 1.0            |                |      | 1.0            |           | LSB              |

| Full-Scale Error <sup>3, 4</sup>                |      |                | $\pm 0.5$ |             |                | ±0.25          |      |                | $\pm 0.5$ | %                |

| Full-Scale Error Drift                          |      | $\pm 7$        |           |             | $\pm 7$        |                |      | ±7             |           | ppm/°C           |

| Full-Scale Error                                |      |                |           |             |                |                |      |                |           |                  |

| Ext. REF = $2.5 \text{ V}$                      |      |                | $\pm 0.5$ |             |                | $\pm 0.25$     |      |                | $\pm 0.5$ | %                |

| Full-Scale Error Drift                          |      |                |           |             |                |                |      |                |           |                  |

| Ext. REF = $2.5 \text{ V}$                      |      | $\pm 2$        |           |             | $\pm 2$        |                |      | $\pm 2$        |           | ppm/°C           |

| Bipolar Zero Error <sup>3</sup>                 |      |                |           |             |                |                |      |                |           |                  |

| Bipolar Ranges                                  |      |                | $\pm 10$  |             |                | $\pm 10$       |      |                | ±15       | mV               |

| Bipolar Zero Error Drift                        |      |                |           |             |                |                |      |                |           |                  |

| Bipolar Ranges                                  |      | $\pm 2$        |           |             | $\pm 2$        |                |      | $\pm 2$        |           | ppm/°C           |

| Unipolar Zero Error <sup>3</sup>                |      |                |           |             |                |                |      |                |           |                  |

| Unipolar Ranges                                 |      |                | $\pm 10$  |             |                | $\pm 10$       |      |                | $\pm 10$  | mV               |

| Unipolar Zero Error Drift                       |      |                |           |             |                |                |      |                |           |                  |

| Unipolar Ranges                                 |      | $\pm 2$        |           |             | $\pm 2$        |                |      | $\pm 2$        |           | ppm/°C           |

| Recovery to Rated Accuracy                      |      |                |           |             |                |                |      |                |           |                  |

| After Power-Down <sup>5</sup>                   |      |                |           |             |                |                |      |                |           |                  |

| $2.2 \mu\text{F}$ to CAP                        |      | 1              |           |             | 1              |                |      | 1              |           | ms               |

| Power Supply Sensitivity                        |      |                |           |             |                |                |      |                |           | LOD              |

| $V_{ANA} = V_{DIG} = V_D = 5 \text{ V} \pm 5\%$ |      |                | ±8        |             |                | ±8             |      |                | ±8        | LSB              |

| AC ACCURACY                                     |      |                |           |             |                |                |      |                |           | 7                |

| Spurious Free Dynamic Range <sup>6</sup>        | 90   |                |           | 96          |                |                | 90   |                |           | dB <sup>7</sup>  |

| Total Harmonic Distortion <sup>6</sup>          |      |                | -90       |             |                | -96            |      |                | -90       | dB               |

| Signal-to-(Noise+Distortion) <sup>6</sup>       | 83   |                |           | 85          | • •            |                | 83   |                |           | dB               |

| -60 dB Input                                    |      | 27             |           |             | 28             |                |      | 27             |           | dB               |

| Signal-to-Noise <sup>6</sup>                    | 83   |                |           | 85          |                |                | 83   |                |           | dB               |

| Full Power Bandwidth <sup>8</sup>               |      | 1              |           |             | 1              |                |      | 1              |           | MHz              |

| -3 dB Input Bandwidth                           |      | 2.7            |           |             | 2.7            |                |      | 2.7            |           | MHz              |

| SAMPLING DYNAMICS                               |      |                |           |             |                |                |      |                |           |                  |

| Aperture Delay                                  |      | 40             |           |             | 40             |                |      | 40             |           | ns               |

| Transient Response, Full-Scale Step             |      |                | 1         |             |                | 1              |      |                | 1         | μs               |

| Overvoltage Recovery <sup>9</sup>               |      | 150            |           |             | 150            |                |      | 150            |           | ns               |

| REFERENCE                                       |      |                |           |             |                |                |      |                |           |                  |

| Internal Reference Voltage                      | 2.48 | 2.5            | 2.52      | 2.48        | 2.5            | 2.52           | 2.48 | 2.5            | 2.52      | V                |

| Internal Reference Source Current               |      | 1              |           |             | 1              |                |      | 1              |           | μA               |

| External Reference Voltage Range                |      |                |           |             |                |                |      |                |           |                  |

| for Specified Linearity                         | 2.3  | 2.5            | 2.7       | 2.3         | 2.5            | 2.7            | 2.3  | 2.5            | 2.7       | V                |

| External Reference Current Drain                |      |                |           |             |                |                |      |                |           |                  |

| Ext. $REF = 2.5 V$                              |      |                | 1.2       |             |                | 1.2            |      |                | 1.2       | mA               |

NOTES

$^1\text{LSB}$  means Least Significant Bit. With a  $\pm 10$  V input, one LSB is 305  $\mu\text{V}.$

<sup>2</sup>Typical rms noise at worst case transitions and temperatures.

<sup>3</sup>Measured with fixed resistors as shown in Figures 11, 12 and 13. Adjustable to zero. Tested at room temperature.

<sup>4</sup>Full-Scale Error is expressed as the % difference between the actual full-scale code transition voltage and the ideal full scale transition voltage, and includes the effect of offset error. For bipolar input ranges, the Full-Scale Error is the worst case of either the –Full Scale or +Full Scale code transition voltage errors. For unipolar input ranges, Full-Scale Error is with respect to the +Full-Scale code transition voltage.

<sup>5</sup>External 2.5 V reference connected to REF.

${}^{6}f_{IN} = 20 \text{ kHz}, 0.5 \text{ dB}$  down unless otherwise noted.

<sup>7</sup>All specifications in dB are referred to a full scale  $\pm 10$  V input.

<sup>8</sup>Full-Power Bandwidth is defined as full-scale input frequency at which Signal-to-(Noise+Distortion) degrades to 60 dB, or 10 bits of accuracy.

$^9\text{Recovers to specified performance after a <math display="inline">2\times F_S$  input overvoltage.

Specifications subject to change without notice.

# AD977/AD977A—SPECIFICATIONS (Both Specs)

|                       |                             |              | A, B, C Grades               |                        |      |

|-----------------------|-----------------------------|--------------|------------------------------|------------------------|------|

| Parameter             | Conditions                  | Min          | Тур                          | Max                    | Unit |

| DIGITAL INPUTS        |                             |              |                              |                        |      |

| Logic Levels          |                             |              |                              |                        |      |

| V <sub>IL</sub>       |                             | -0.3         |                              | +0.8                   | V    |

| $V_{IH}$              |                             | 2.0          |                              | $V_{DIG} + 0.3$        | V    |

| $I_{IL}$              |                             |              |                              | $\pm 10$               | μA   |

| I <sub>IH</sub>       |                             |              |                              | ±10                    | μA   |

| DIGITAL OUTPUTS       |                             |              |                              |                        |      |

| Data Format           |                             |              | Serial 16-Bits               |                        |      |

| Data Coding           |                             | В            | inary Two's Complement       | or Straight Binary     |      |

| Pipeline Delay        |                             | Conversion I | Results Only Available after | r Completed Conversion |      |

| V <sub>OL</sub>       | $I_{SINK} = 1.6 \text{ mA}$ |              |                              | 0.4                    | V    |

| V <sub>OH</sub>       | $I_{SOURCE} = 500 \mu A$    | 4            |                              |                        | V    |

| POWER SUPPLIES        |                             |              |                              |                        |      |

| Specified Performance |                             |              |                              |                        |      |

| V <sub>DIG</sub>      |                             | 4.75         | 5                            | 5.25                   | V    |

| $V_{ANA}$             |                             | 4.75         | 5                            | 5.25                   | V    |

| I <sub>DIG</sub>      |                             |              | 4                            |                        | mA   |

| I <sub>ANA</sub>      |                             |              | 11                           |                        | mA   |

| Power Dissipation     |                             |              |                              |                        |      |

| PWRD LOW              |                             |              |                              | 100                    | mW   |

| PWRD HIGH             |                             |              | 50                           |                        | μW   |

| TEMPERATURE RANGE     |                             |              |                              |                        |      |

| Specified Performance | $T_{MIN}$ to $T_{MAX}$      | -40          |                              | +85                    | °C   |

Specifications subject to change without notice.

### TIMING SPECIFICATIONS (AD977A: $F_s = 200$ kHz, AD977: $F_s = 100$ kHz, $V_{DIG} = V_{ANA} = 5$ V, $-40^{\circ}$ C to $+85^{\circ}$ C)

|                                                                           |                 | A   | <b>D9</b> 77A |                     |     | AD977 |                     |      |

|---------------------------------------------------------------------------|-----------------|-----|---------------|---------------------|-----|-------|---------------------|------|

|                                                                           | Symbol          | Min | Тур           | Max                 | Min | Тур   | Max                 | Unit |

| Convert Pulsewidth                                                        | t <sub>1</sub>  | 50  |               |                     | 50  |       |                     | ns   |

| $R/\overline{C}$ , $\overline{CS}$ to $\overline{BUSY}$ Delay             | t <sub>2</sub>  |     |               | 83                  |     |       | 83                  | ns   |

| BUSY LOW Time                                                             | t <sub>3</sub>  |     |               | 4.0                 |     |       | 8.0                 | μs   |

| BUSY Delay after End of Conversion                                        | $t_4$           |     | 50            |                     |     | 50    |                     | ns   |

| Aperture Delay                                                            | t <sub>5</sub>  |     | 40            |                     |     | 40    |                     | ns   |

| Conversion Time                                                           | t <sub>6</sub>  |     | 3.8           | 4.0                 |     | 7.6   | 8.0                 | μs   |

| Acquisition Time                                                          | t <sub>7</sub>  | 1.0 |               |                     | 2.0 |       |                     | μs   |

| Throughput Time                                                           | $t_6 + t_7$     |     |               | 5                   |     |       | 10                  | μs   |

| $R/\overline{C}$ Low to DATACLK Delay                                     | t <sub>8</sub>  |     | 220           |                     |     | 350   |                     | ns   |

| DATACLK Period                                                            | t <sub>9</sub>  |     | 220           |                     |     | 450   |                     | ns   |

| DATA Valid Setup Time                                                     | t <sub>10</sub> | 50  |               |                     | 100 |       |                     | ns   |

| DATA Valid Hold Time                                                      | t <sub>11</sub> | 20  |               |                     | 20  |       |                     | ns   |

| EXT. DATACLK Period                                                       | t <sub>12</sub> | 66  |               |                     | 100 |       |                     | ns   |

| EXT. DATACLK HIGH                                                         | t <sub>13</sub> | 20  |               |                     | 20  |       |                     | ns   |

| EXT. DATACLK LOW                                                          | t <sub>14</sub> | 30  |               |                     | 30  |       |                     | ns   |

| $R/\overline{C}$ , $\overline{CS}$ to EXT. DATACLK Setup Time             | t <sub>15</sub> | 20  |               | t <sub>12</sub> + 5 | 20  |       | t <sub>12</sub> + 5 | ns   |

| $R/\overline{C}$ to $\overline{CS}$ Setup Time                            | t <sub>16</sub> | 10  |               |                     | 10  |       |                     | ns   |

| EXT. DATACLK to SYNC Delay                                                | t <sub>17</sub> | 15  |               | 66                  | 15  |       | 66                  | ns   |

| EXT. DATACLK to DATA Valid Delay                                          | t <sub>18</sub> | 25  |               | 66                  | 25  |       | 66                  | ns   |

| CS to EXT. DATACLK Rising Edge Delay                                      | t <sub>19</sub> | 10  |               |                     | 10  |       |                     | ns   |

| <u>Previo</u> us DATA Valid after $\overline{CS}$ , R/ $\overline{C}$ Low | t <sub>20</sub> | 3.5 |               |                     | 7.5 |       |                     | μs   |

| BUSY to EXT. DATACLK Setup Time                                           | t <sub>21</sub> | 5   |               |                     | 5   |       |                     | ns   |

| Final EXT. DATACLK to BUSY Rising Edge                                    | t <sub>22</sub> |     |               | 1.7                 |     |       | 3.5                 | μs   |

| TAG Valid Setup Time                                                      | t <sub>23</sub> | 0   |               |                     | 0   |       |                     | ns   |

| TAG Valid Hold Time                                                       | t <sub>24</sub> | 20  |               |                     | 20  |       |                     | ns   |

Specifications subject to change without notice.

### ABSOLUTE MAXIMUM RATINGS<sup>1</sup>

| Analog Inputs                                                                                                                      |

|------------------------------------------------------------------------------------------------------------------------------------|

| $R1_{IN}$ , $R2_{IN}$ , $R3_{IN}$ ±25 V                                                                                            |

| CAP+ $V_{ANA}$ + 0.3 V to AGND2 – 0.3 V                                                                                            |

| REF Indefinite Short to AGND2,                                                                                                     |

| $\dots$ Momentary Short to $V_{ANA}$                                                                                               |

| Ground Voltage Differences                                                                                                         |

| DGND, AGND1, AGND2 ±0.3 V                                                                                                          |

| Supply Voltages                                                                                                                    |

| V <sub>ANA</sub>                                                                                                                   |

| $V_{\text{DIG}}$ to $V_{\text{ANA}}$ $\pm 7 \text{ V}$                                                                             |

| V <sub>DIG</sub>                                                                                                                   |

| Digital Inputs $\dots \dots \dots$ |

| Internal Power Dissipation <sup>2</sup>                                                                                            |

| PDIP (N), SOIC (R), SSOP (RS)                                                                                                      |

| Junction Temperature                                                                                                               |

| Storage Temperature Range N, R –65°C to +150°C                                                                                     |

| Lead Temperature Range                                                                                                             |

| (Soldering 10 sec)                                                                                                                 |

| NOTES                                                                                                                              |

<sup>1</sup>Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

<sup>2</sup>Specification is for device in free air:

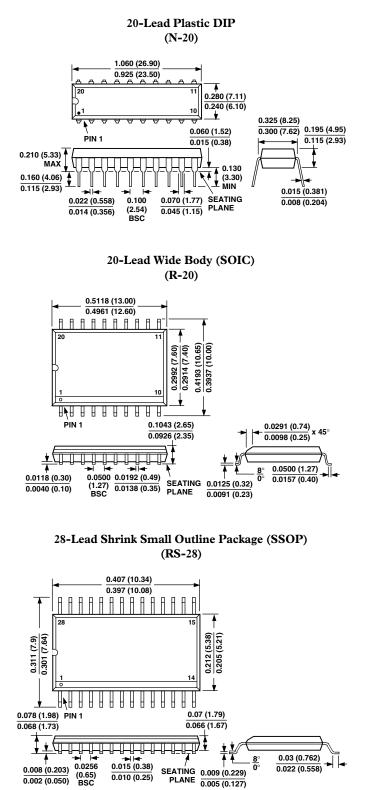

20-Lead PDIP:  $\theta_{IA} = 100^{\circ}$ C/W,  $\theta_{IC} = 31^{\circ}$ C/W,

20-Lead SOIC:  $\theta_{JA} = 75^{\circ}C/W$ ,  $\theta_{JC} = 24^{\circ}C/W$ ,

28-Lead SSOP:  $\theta_{IA} = 109^{\circ}C/W$ ,  $\theta_{IC} = 39^{\circ}C/W$ .

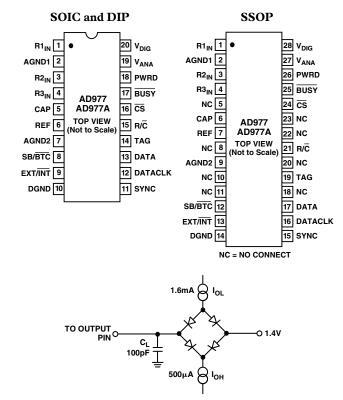

**PIN CONFIGURATIONS**

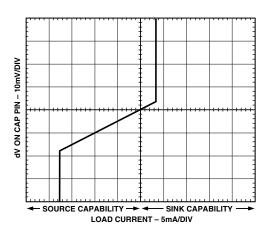

Figure 1. Load Circuit for Digital Interface Timing

### **ORDERING GUIDE**

| Model     | Temperature<br>Range | Throughput<br>Rate | Max INL       | Min S/(N+D) | Package<br>Options* |

|-----------|----------------------|--------------------|---------------|-------------|---------------------|

| AD977AN   | -40°C to +85°C       | 100 kSPS           | ±3.0 LSB      | 83 dB       | N-20                |

| AD977BN   | -40°C to +85°C       | 100 kSPS           | $\pm 2.0$ LSB | 85 dB       | N-20                |

| AD977CN   | -40°C to +85°C       | 100 kSPS           |               | 83 dB       | N-20                |

| AD977AAN  | -40°C to +85°C       | 200 kSPS           | ±3.0 LSB      | 83 dB       | N-20                |

| AD977ABN  | -40°C to +85°C       | 200 kSPS           | $\pm 2.0$ LSB | 85 dB       | N-20                |

| AD977ACN  | -40°C to +85°C       | 200 kSPS           |               | 83 dB       | N-20                |

| AD977AR   | -40°C to +85°C       | 100 kSPS           | ±3.0 LSB      | 83 dB       | R-20                |

| AD977BR   | -40°C to +85°C       | 100 kSPS           | $\pm 2.0$ LSB | 85 dB       | R-20                |

| AD977CR   | -40°C to +85°C       | 100 kSPS           |               | 83 dB       | R-20                |

| AD977AAR  | -40°C to +85°C       | 200 kSPS           | ±3.0 LSB      | 83 dB       | R-20                |

| AD977ABR  | -40°C to +85°C       | 200 kSPS           | $\pm 2.0$ LSB | 85 dB       | R-20                |

| AD977ACR  | -40°C to +85°C       | 200 kSPS           |               | 83 dB       | R-20                |

| AD977ARS  | -40°C to +85°C       | 100 kSPS           | ±3.0 LSB      | 83 dB       | RS-28               |

| AD977BRS  | -40°C to +85°C       | 100 kSPS           | $\pm 2.0$ LSB | 85 dB       | RS-28               |

| AD977CRS  | -40°C to +85°C       | 100 kSPS           |               | 83 dB       | RS-28               |

| AD977AARS | -40°C to +85°C       | 200 kSPS           | ±3.0 LSB      | 83 dB       | RS-28               |

| AD977ABRS | -40°C to +85°C       | 200 kSPS           | ±2.0 LSB      | 85 dB       | RS-28               |

| AD977ACRS | -40°C to +85°C       | 200 kSPS           |               | 83 dB       | RS-28               |

\*N = 20-lead 300 mil plastic DIP; R = 20-lead SOIC; RS = 28-lead SSOP.

#### CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the AD977/AD977A feature proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high-energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

### PIN FUNCTION DESCRIPTIONS

| Pin No.<br>DIP/SOIC | Pin No.<br>SSOP | Mnemonic                                               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------------------|-----------------|--------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 3, 4             | 1, 3, 4         | R1 <sub>IN</sub> , R2 <sub>IN</sub> , R3 <sub>IN</sub> | Analog Input. Refer to Table I, Table II for input range configuration.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2                   | 2               | AGND1                                                  | Analog Ground. Used as the ground reference point for the REF pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 5                   | 6               | САР                                                    | Reference buffer output. Connect a 2.2 $\mu$ F tantalum capacitor between CAP and Analog Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 6                   | 7               | REF                                                    | Reference Input/Output. The internal 2.5 V reference is available at this pin. Alternatively an external reference can be used to override the internal reference. In either case, connect a 2.2 $\mu$ F tantalum capacitor between REF and Analog Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 7                   | 9               | AGND2                                                  | Analog Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 8                   | 12              | SB/BTC                                                 | This digital input is used to select the data format of a conversion result. With SB/BTC tied LOW, conversion data will be output in Binary Two's Complement format. With SB/BTC connected to a logic HIGH, data is output in Straight Binary format.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 9                   | 13              | EXT/INT                                                | Digital select input for choosing the internal or an external data clock. With EXT/INT tied LOW, after initiating a conversion, 16 DATACLK pulses transmit the previous conversion result as shown in Figure 3. With EXT/INT set to a logic HIGH, output data is synchronized to an external clock signal connected to the DATACLK input. Data is output as indicated in Figure 4 through Figure 9.                                                                                                                                                                                                                                                                                                                                      |

| 10                  | 14              | DGND                                                   | Digital Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 11                  | 15              | SYNC                                                   | Digital output frame synchronization for use with an external data clock $(EXT/\overline{INT} = Logic HIGH)$ . When a read sequence is initiated, a pulse one DATACLK period wide is output synchronous to the external data clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 12                  | 16              | DATACLK                                                | Serial data clock input or output, dependent upon the logic state of the EXT/INT pin. When using the internal data clock (EXT/INT = Logic LOW), a conversion start sequence will initiate transmission of 16 DATACLK periods. Output data is synchronous to this clock and is valid on both its rising and falling edges (Figure 3). When using an external data clock (EXT/INT = Logic HIGH), the $\overline{CS}$ and $R/\overline{C}$ signals control how conversion data is accessed.                                                                                                                                                                                                                                                 |

| 13                  | 17              | DATA                                                   | The serial data output is synchronized to DATACLK. Conversion results are stored in an on-chip register. The AD977 provides the conversion result, MSB first, from its internal shift register. The DATA format is determined by the logic level of SB/BTC. When using the internal data clock (EXT/INT = Logic LOW), DATA is valid on both the rising and falling edges of DATACLK. Between conversions DATA will remain at the level of the TAG input when the conversion was started. Using an external data clock (EXT/INT = Logic HIGH) allows previous conversion data to be accessed during a conversion (Figures 5, 7 and 9) or the conversion result can be accessed after the completion of a conversion (Figures 4, 6 and 8). |

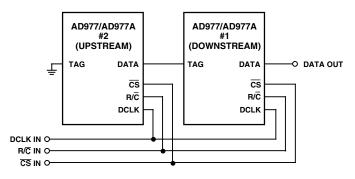

| 14                  | 19              | TAG                                                    | This digital input can be used with an external data clock, (EXT/INT = Logic HIGH) to daisy chain the conversion results from two or more AD977s onto a single DATA line. The digital data level on TAG is output on DATA with a delay of 16 or 17 external DATACLK periods after the initiation of the read sequence. Dependent on whether a SYNC is not present or present.                                                                                                                                                                                                                                                                                                                                                            |

| 15                  | 21              | R/C                                                    | Read/Convert Input. Is used to control the conversion and read modes of the AD977. With $\overline{\text{CS}}$ LOW; a falling edge on $R/\overline{C}$ holds the analog input signal internally and starts a conversion, a rising edge enables the transmission of the conversion result.                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 16                  | 24              | CS                                                     | Chip Select Input. With $R/\overline{C}$ LOW, a falling edge on $\overline{CS}$ will initiate a conversion.<br>With $R/\overline{C}$ HIGH, a falling edge on $\overline{CS}$ will enable the serial data output sequence.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 17                  | 25              | BUSY                                                   | Busy Output. Goes LOW when a conversion is started, and remains LOW until the conversion is completed and the data is latched into the on-chip shift register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 18                  | 26              | PWRD                                                   | Power-Down Input. When set to a logic HIGH power consumption is reduced and conversions are inhibited. The conversion result from the previous conversion is stored in the onboard shift register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 19                  | 27              | V <sub>ANA</sub>                                       | Analog Power Supply. Nominally 5 V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 20                  | 28              | V <sub>DIG</sub>                                       | Digital Power Supply. Nominally 5 V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

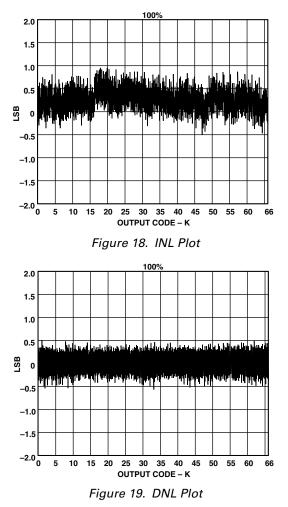

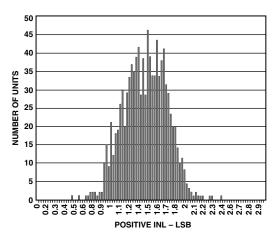

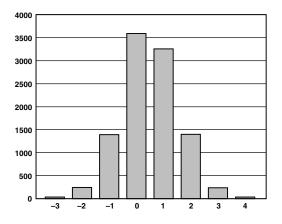

### DEFINITION OF SPECIFICATIONS INTEGRAL NONLINEARITY ERROR (INL)

Linearity error refers to the deviation of each individual code from a line drawn from "negative full scale" through "positive full scale." The point used as "negative full scale" occurs 1/2 LSB before the first code transition. "Positive full scale" is defined as a level 1 1/2 LSB beyond the last code transition. The deviation is measured from the middle of each particular code to the true straight line.

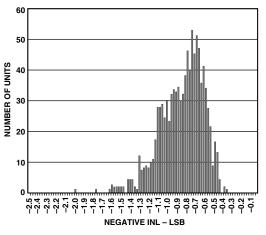

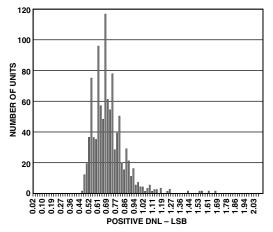

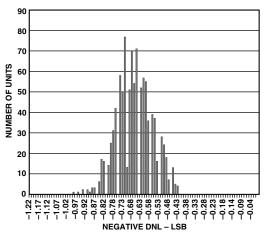

### DIFFERENTIAL NONLINEARITY ERROR (DNL)

In an ideal ADC, code transitions are 1 LSB apart. Differential nonlinearity is the maximum deviation from this ideal value. It is often specified in terms of resolution for which no missing codes are guaranteed.

### FULL-SCALE ERROR

The last + transition (from  $011 \dots 10$  to  $011 \dots 11$  for two's complement format) should occur for an analog voltage 1 1/2 LSB below the nominal full scale (9.9995422 V for a ±10 V range). The full-scale error is the deviation of the actual level of the last transition from the ideal level.

### **BIPOLAR ZERO ERROR**

Bipolar zero error is the difference between the ideal midscale input voltage (0 V) and the actual voltage producing the midscale output code.

### **UNIPOLAR ZERO ERROR**

In unipolar mode, the first transition should occur at a level 1/2 LSB above analog ground. Unipolar zero error is the deviation of the actual transition from that point.

### SPURIOUS FREE DYNAMIC RANGE

The difference, in decibels (dB), between the rms amplitude of the input signal and the peak spurious signal.

### TOTAL HARMONIC DISTORTION (THD)

THD is the ratio of the rms sum of the first six harmonic components to the rms value of a full-scale input signal and is expressed in decibels.

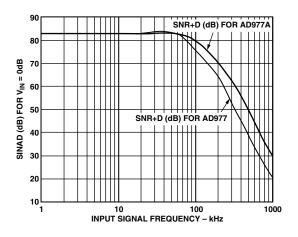

### SIGNAL TO (NOISE AND DISTORTION) (S/[N+D]) RATIO

S/(N+D) is the ratio of the rms value of the measured input signal to the rms sum of all other spectral components below the Nyquist frequency, including harmonics but excluding dc. The value for S/(N+D) is expressed in decibels.

### FULL POWER BANDWIDTH

The full power bandwidth is defined as the full-scale input frequency at which the S/(N+D) degrades to 60 dB, 10 bits of accuracy.

### APERTURE DELAY

Aperture delay is a measure of the acquisition performance, and is measured from the falling edge of the  $R/\overline{C}$  input to when the input signal is held for a conversion.

### TRANSIENT RESPONSE

The time required for the AD977/AD977A to achieve its rated accuracy after a full-scale step function is applied to its input.

### **OVERVOLTAGE RECOVERY**

The time required for the ADC to recover to full accuracy after an analog input signal 150% of full-scale is reduced to 50% of the full-scale value.

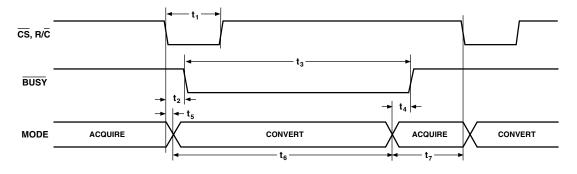

### **CONVERSION CONTROL**

The AD977/AD977A is controlled by two signals:  $R/\overline{C}$  and  $\overline{CS}$ . When  $R/\overline{C}$  is brought low, with  $\overline{CS}$  low, for a minimum of 50 ns, the input signal will be held on the internal capacitor array and a conversion "n" will begin. Once the conversion process does begin, the **BUSY** signal will go low until the conversion is complete. Internally, the signals  $R/\overline{C}$  and  $\overline{CS}$  are OR'd together and there is no requirement on which signal is taken low first when initiating a conversion. The only requirement is that there be at least 10 ns of delay between the two signals being taken low. After the conversion is complete the  $\overline{\text{BUSY}}$  signal will return high and the AD977/AD977A will again resume tracking the input signal. Under certain conditions the  $\overline{CS}$  pin can be tied Low and  $R/\overline{C}$  will be used to determine whether you are initiating a conversion or reading data. On the first conversion, after the AD977/AD977A is powered up, the DATA output will be indeterminate.

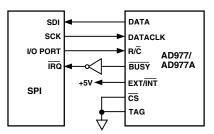

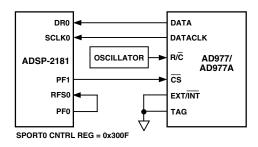

Conversion results can be clocked serially out of the AD977/ AD977A using either an internal clock, generated by the AD977/AD977A, or by using an external clock. The AD977/ AD977A is configured for the internal data clock mode by pulling the EXT/INT pin low. It is configured for the external clock mode by pulling the EXT/INT pin high.

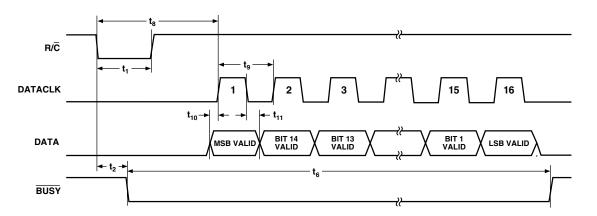

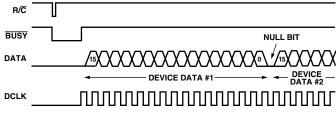

### INTERNAL DATA CLOCK MODE

The AD977/AD977A is configured to generate and provide the data clock when the EXT/ $\overline{\text{INT}}$  pin is held low. Typically  $\overline{\text{CS}}$  will be tied low and  $\overline{\text{R/C}}$  will be used to initiate a conversion "n." During the conversion the AD977/AD977A will output 16 bits of data, MSB first, from conversion "n-1" on the DATA pin. This data will be synchronized with 16 clock pulses provided on the DATACLK pin. The output data will be valid on both the rising and falling edge of the data clock as shown in Figure 3. After the LSB has been presented, the DATA pin will assume whatever state the TAG input was at during the start of conversion, and the DATACLK pin will stay low until another conversion is initiated.

### EXTERNAL DATA CLOCK MODE

The AD977/AD977A is configured to accept an externally supplied data clock when the EXT/INT pin is held high. This mode of operation provides several methods by which conversion results can be read from the AD977/AD977A. The output data from conversion "n-1" can be read during conversion "n," or the output data from conversion "n" can be read after the conversion is complete. The external clock can be either a continuous or discontinuous clock. A discontinuous clock can be either

Figure 2. Basic Conversion Timing

Figure 3. Serial Data Timing for Reading Previous Conversion Results with Internal Clock ( $\overline{CS}$ , EXT/ $\overline{INT}$  and TAG Set to Logic Low)

normally low or normally high when inactive. In the case of the discontinuous clock, the AD977/AD977A can be configured to either generate or not generate a SYNC output (with a continuous clock a SYNC output will always be produced).

Each of the methods will be described in the following sections and are illustrated in Figures 4 through 9. It should be noted that all timing diagrams assume that the receiving device is latching data on the rising edge of the external clock. If the falling edge of DATACLK is used then, in the case of a discontinuous clock, one less clock pulse is required than shown in Figures 4 through 7 to latch in a 16-bit word. Note that data is valid on the falling edge of a clock pulse (for  $t_{13}$  greater than  $t_{18}$ ) and the rising edge of the next clock pulse.

The AD977 provides error correction circuitry that can correct for an improper bit decision made during the first half of the conversion cycle. Normally the occurrence of an incorrect bit decision during a conversion cycle is irreversible. This error occurs as a result of noise during the time of the decision or due to insufficient settling time. As the AD977/AD977A is performing a conversion it is important that transitions not occur on digital input/output pins or degradation of the conversion result could occur. This is particularly important during the second half of the conversion process. For this reason it is recommended that when an external clock is being provided it be a discontinuous clock that is not toggling during the time that <u>BUSY</u> is low or, more importantly, that it does not transition during the latter half of <u>BUSY</u> low.

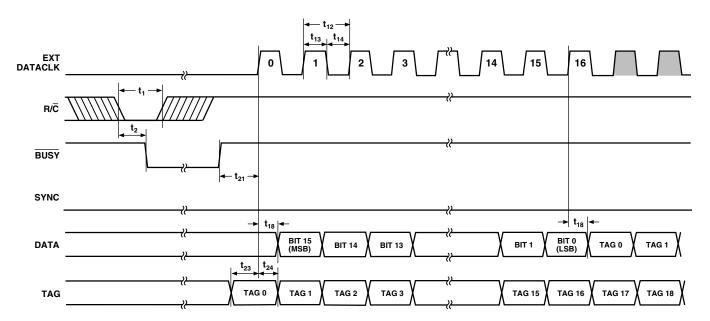

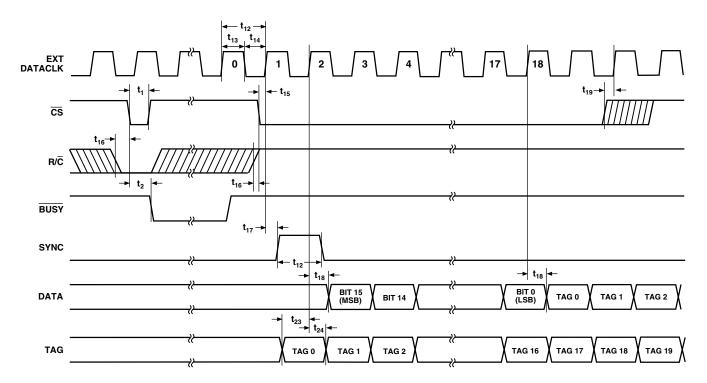

### EXTERNAL DISCONTINUOUS CLOCK DATA READ AFTER CONVERSION NO SYNC OUTPUT GENERATED

Figure 4 illustrates the method by which data from conversion "n" can be read after the conversion is complete using a discontinuous external clock without the generation of a SYNC output. After a conversion is complete, indicated by  $\overline{BUSY}$ returning high, the result of that conversion can be read while  $\overline{CS}$  is Low and  $\overline{R/C}$  is high. In this mode  $\overline{CS}$  can be tied low. The MSB will be valid on the first falling edge and the second rising edge of DATACLK. The LSB will be valid on the 16th falling edge and the 17th rising edge of DATACLK. A minimum of 16 clock pulses are required for DATACLK if the receiving device will be latching data on the falling edge of DATACLK. A minimum of 17 clock pulses are required for DATACLK if the receiving device will be latching data on the rising edge of DATACLK. Approximately 40 ns after the 17th rising edge of DATACLK (if provided) the DATA output pin will reflect the state of the TAG input pin during the first rising edge of DATACLK.

The advantage of this method of reading data is that it is not being clocked out during a conversion and therefore conversion performance is not degraded.

When reading data after the conversion is complete, with the highest frequency permitted for DATACLK (15.15 MHz), and with the AD977A, the maximum possible throughput is approximately 195 kHz and not the rated 200 kHz.

For details on use of the TAG input with this mode see the Use of the Tag Feature section.

Figure 4. Conversion and Read Timing Using an External Discontinuous Data Clock (EXT/INT Set to Logic High, CS Set to Logic Low)

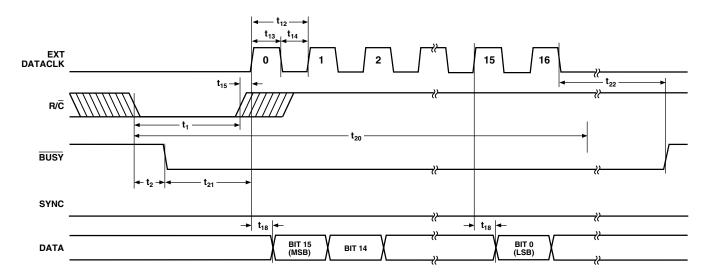

#### EXTERNAL DISCONTINUOUS CLOCK DATA READ DURING CONVERSION NO SYNC OUTPUT GENERATED

Figure 5 illustrates the method by which data from conversion "n-1" can be read during conversion "n" while using a discontinuous external clock, without the generation of a SYNC output. After a conversion is initiated, indicated by  $\overline{BUSY}$  going low, the result of the previous conversion can be read while  $\overline{CS}$ is low and  $R/\overline{C}$  is high. In this mode  $\overline{CS}$  can be tied low. The MSB will be valid on the 1st falling edge and the 2nd rising edge of DATACLK. The LSB will be valid on the 16th falling edge and the 17th rising edge of DATACLK. A minimum of 16 clock pulses are required for DATACLK if the receiving device will be latching data on the falling edge of DATACLK. A minimum of 17 clock pulses are required for DATACLK if the receiving device will be latching data on the rising edge of DATACLK. Approximately 40 ns after the 17th rising edge of DATACLK (if provided) the DATA output pin will reflect the state of the TAG input pin during the first rising edge of DATACLK.

For both the AD977 and the AD977A the data should be clocked out during the first half of  $\overline{\text{BUSY}}$  so not to degrade conversion performance. For the AD977 this requires use of a 4.8 MHz DATACLK or greater with data being read out as soon as the conversion process begins. For the AD977A it requires use of a 10 MHz DATACLK or greater.

It is not recommended that data be shifted through the TAG input in this mode as it will certainly result in clocking of data during the second half of the conversion.

### EXTERNAL DISCONTINUOUS CLOCK DATA READ AFTER CONVERSION WITH SYNC OUTPUT GENERATED

Figure 6 illustrates the method by which data from conversion "n" can be read after the conversion is complete using a discontinuous external clock, with the generation of a SYNC output. What permits the generation of a SYNC output is a transition of DATACLK while either  $\overline{CS}$  is high or while both  $\overline{CS}$  and  $R/\overline{C}$ are low. After a conversion is complete, indicated by  $\overline{\text{BUSY}}$ returning high, the result of that conversion can be read while  $\overline{CS}$  is Low and  $\overline{R/C}$  is high. In this mode  $\overline{CS}$  can be tied low. In Figure 6 clock pulse #0 is used to enable the generation of a SYNC pulse. The SYNC pulse is actually clocked out approximately 40 ns after the rising edge of clock pulse #1. The SYNC pulse will be valid on the falling edge of clock pulse #1 and the rising edge of clock pulse #2. The MSB will be valid on the falling edge of clock pulse #2 and the rising edge of clock pulse #3. The LSB will be valid on the falling edge of clock pulse #17 and the rising edge of clock pulse #18. Approximately 40 ns after the rising edge of clock pulse #18 the DATA output pin will reflect the state of the TAG input pin during the rising edge of clock pulse #2. The advantage of this method of reading data is that it is not being clocked out during a conversion and therefore conversion performance is not degraded.

When reading data after the conversion is complete, with the highest frequency permitted for DATACLK (15.15 MHz), and with the AD977A, the maximum possible throughput is approximately 195 kHz and not the rated 200 kHz.

For details on use of the TAG input with this mode see the Use of the TAG Input section.

Figure 5. Conversion and Read Timing for Reading Previous Conversion Results During A Conversion Using External Discontinuous Data Clock (EXT/INT Set to Logic High, CS Set to Logic Low)

Figure 6. Conversion and Read Timing Using An External Discontinuous Data Clock (EXT/INT Set to Logic High, CS Set to Logic Low)

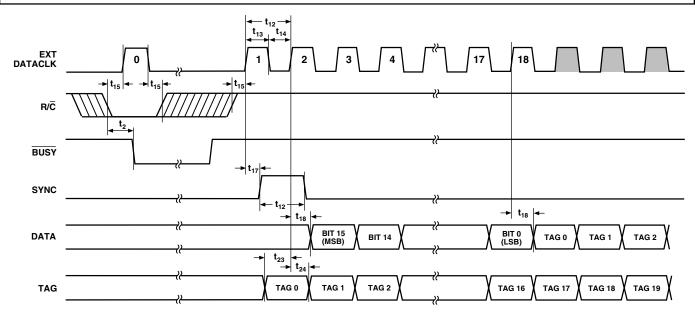

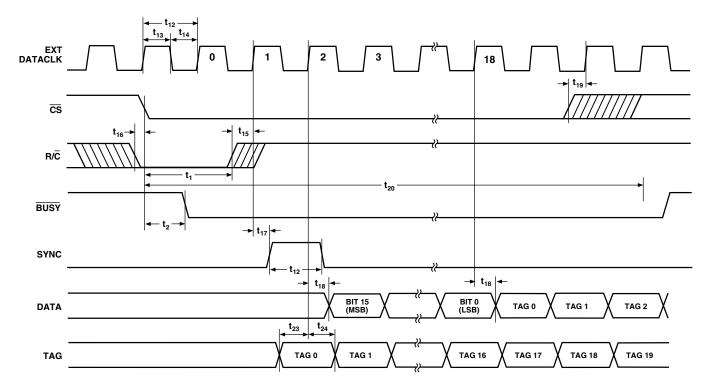

### EXTERNAL DISCONTINUOUS CLOCK DATA READ DURING CONVERSION WITH SYNC OUTPUT GENERATED

Figure 7 illustrates the method by which data from conversion "n-1" can be read during conversion "n" while using a discontinuous external clock, with the generation of a SYNC output. What permits the generation of a SYNC output is a transition of DATACLK while either  $\overline{CS}$  is High or while both  $\overline{CS}$  and  $R/\overline{C}$  are low. In Figure 7 a conversion is initiated by taking  $R/\overline{C}$  low with  $\overline{CS}$  tied low. While this condition exists a transition of DATACLK, clock pulse #0, will enable the generation of a SYNC pulse. Less then 83 ns after  $R/\overline{C}$  is taken low the  $\overline{BUSY}$  output will go low to indicate that the conversion process has

began. Figure 7 shows  $R/\overline{C}$  then going high and after a delay of greater than 15 ns (t<sub>15</sub>) clock pulse #1 can be taken high to request the SYNC output. The SYNC output will appear approximately 40 ns after this rising edge and will be valid on the falling edge of clock pulse #1 and the rising edge of clock pulse #2. The MSB will be valid approximately 40 ns after the rising edge of clock pulse #2 and can be latched off either the falling edge of clock pulse #2 or the rising edge of clock pulse #3. The LSB will be valid on the falling edge of clock pulse #18. Approximately 40 ns after the rising edge of clock pulse #18, the DATA output pin will reflect the state of the TAG input pin during the rising edge of clock pulse #2.

Figure 7. Conversion and Read Timing for Reading Previous Conversion Results During a Conversion Using External Discontinuous Data Clock (EXT/INT Set to Logic High, CS Set to Logic Low)

For both the AD977 and the AD977A the data should be clocked out during the first half of  $\overline{\text{BUSY}}$  so not to degrade conversion performance. For the AD977 this requires use of a 4.8 MHz DATACLK or greater, with data being read out as soon as the conversion process begins. For the AD977A it requires use of a 10 MHz DATACLK or greater.

It is not recommended that data be shifted through the TAG input in this mode as it will certainly result in clocking of data during the second half of the conversion.

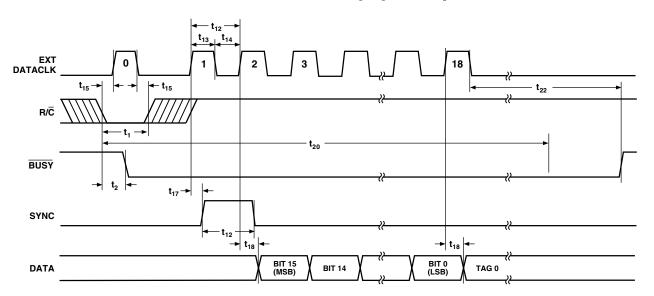

## EXTERNAL CONTINUOUS CLOCK DATA READ AFTER CONVERSION WITH SYNC OUTPUT GENERATED

Figure 8 illustrates the method by which data from conversion "n" can be read after the conversion is complete using a continuous external clock, with the generation of a SYNC output. What permits the generation of a SYNC output is a transition of DATACLK while either  $\overline{CS}$  is high or while both  $\overline{CS}$  and  $R/\overline{C}$  are low.

With a continuous clock the  $\overline{CS}$  pin cannot be tied low as it could be with a discontinuous clock. Use of a continuous clock, while a conversion is occurring, can increase the DNL and Transition Noise of the AD977/AD977A.

After a conversion is complete, indicated by  $\overline{\text{BUSY}}$  returning high, the result of that conversion can be read while  $\overline{\text{CS}}$  is low and  $R/\overline{\text{C}}$  is high. In Figure 8 clock pulse #0 is used to enable the generation of a SYNC pulse. The SYNC pulse is actually clocked out approximately 40 ns after the rising edge of clock pulse #1. The SYNC pulse will be valid on the falling edge of clock pulse #1 and the rising edge of clock pulse #2. The MSB will be valid on the falling edge of clock pulse #2 and the rising edge of clock pulse #3. The LSB will be valid on the falling edge of clock pulse #17 and the rising edge of clock pulse #18. Approximately 50 ns after the rising edge of clock pulse #18 the DATA output pin will reflect the state of the TAG input pin during the rising edge of clock pulse #2.

When reading data after the conversion is complete, with the highest frequency permitted for DATACLK (15.15 MHz) and, with the AD977A, the maximum possible throughput is approximately 195 kHz and not the rated 200 kHz.

For details on use of the TAG input with this mode see the Use of the TAG Input section.

Figure 8. Conversion and Read Timing Using an External Continuous Data Clock (EXT/INT Set to Logic High)

## EXTERNAL CONTINUOUS CLOCK DATA READ DURING CONVERSION WITH SYNC OUTPUT GENERATED

Figure 9 illustrates the method by which data from conversion "n-1" can be read during conversion "n" while using a continuous external clock with the generation of a SYNC output. What permits the generation of a SYNC output is a transition of DATACLK while either  $\overline{CS}$  is high or while both  $\overline{CS}$  and  $R/\overline{C}$  are low.

With a continuous clock the  $\overline{\text{CS}}$  pin cannot be tied low as it could be with a discontinuous clock. Use of a continuous clock while a conversion is occurring can increase the DNL and Transition Noise of the AD977/AD977A.

In Figure 9 a conversion is initiated by taking  $R/\overline{C}$  low with  $\overline{CS}$  held low. While this condition exists a transition of DATACLK, clock pulse #0, will enable the generation of a SYNC pulse. Less then 83 ns after  $R/\overline{C}$  is taken low the  $\overline{BUSY}$  output will go low to indicate that the conversion process has began. Figure 9 shows  $R/\overline{C}$  then going high and after a delay of greater than 15 ns ( $t_{15}$ ), clock pulse #1 can be taken high to request the SYNC output. The SYNC output will appear approximately 50 ns after this rising edge and will be valid on the falling edge of clock pulse #1 and the rising edge of clock pulse #2. The MSB will be valid approximately 40 ns after the rising edge of clock pulse #2 and can be latched off either the falling edge of clock pulse #2 or the rising edge of clock pulse #3. The LSB will be valid on the falling edge of clock pulse #17 and the rising edge of clock pulse #18. Approximately 40 ns after the rising edge of clock pulse #18, the DATA output pin will reflect the state of the TAG input pin during the rising edge of clock pulse #2.

For both the AD977 and the AD977A the data should be clocked out during the 1st half of  $\overline{\text{BUSY}}$  so as not to degrade conversion performance. For the AD977 this requires use of a 4.8 MHz DATACLK or greater with data being read out as soon as the conversion process begins. For the AD977A it requires use of a 10 MHz DATACLK or greater.

Figure 9. Conversion and Read Timing for Reading Previous Conversion Results During a Conversion Using An External Continuous Data Clock (EXT/INT Set to Logic High)

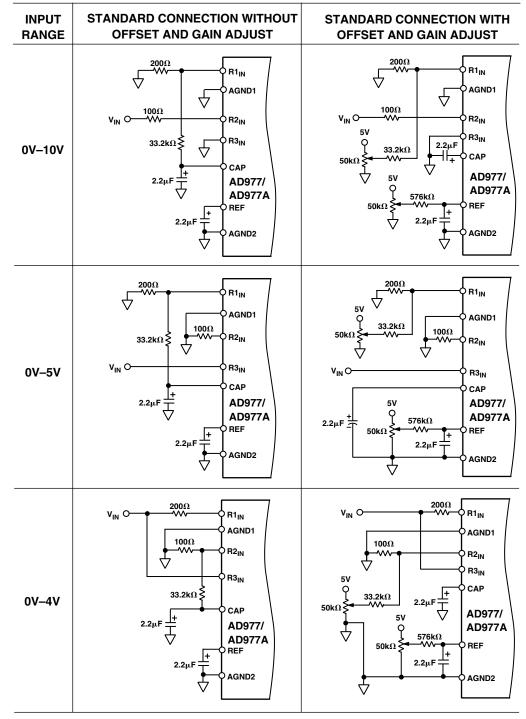

| Input Voltage<br>Range | Connect $R1_{IN}$<br>via 200 $\Omega$ to | Connect $R2_{IN}$<br>via 100 $\Omega$ to | Connect R3 <sub>IN</sub><br>to | Input<br>Impedance |

|------------------------|------------------------------------------|------------------------------------------|--------------------------------|--------------------|

| ±10 V                  | V <sub>IN</sub>                          | AGND                                     | 2.5 V                          | 11.5 kΩ            |

| ±5 V                   | AGND                                     | $V_{IN}$                                 | 2.5 V                          | 6.7 kΩ             |

| ±3.3 V                 | V <sub>IN</sub>                          | V <sub>IN</sub>                          | 2.5 V                          | 5.4 kΩ             |

| 0 V to 10 V            | AGND                                     | V <sub>IN</sub>                          | AGND                           | 6.7 kΩ             |

| 0 V to 5 V             | AGND                                     | AGND                                     | V <sub>IN</sub>                | 5.0 kΩ             |

| 0 V to 4 V             | V <sub>IN</sub>                          | AGND                                     | V <sub>IN</sub>                | 5.4 kΩ             |

### Table I. AD977A Analog Input Configuration

| Input Voltage<br>Range | $\begin{array}{c} \textbf{Connect } \textbf{R1}_{IN} \\ \textbf{via 200 } \Omega \text{ to} \end{array}$ | Connect $R2_{IN}$<br>via 100 $\Omega$ to | Connect R3 <sub>IN</sub><br>to | Input<br>Impedance |

|------------------------|----------------------------------------------------------------------------------------------------------|------------------------------------------|--------------------------------|--------------------|

| ±10 V                  | V <sub>IN</sub>                                                                                          | AGND                                     | CAP                            | 22.9 kΩ            |

| ±5 V                   | AGND                                                                                                     | V <sub>IN</sub>                          | CAP                            | 13.3 kΩ            |

| ±3.3 V                 | V <sub>IN</sub>                                                                                          | V <sub>IN</sub>                          | CAP                            | 10.7 kΩ            |

| 0 V to 10 V            | AGND                                                                                                     | $V_{IN}$                                 | AGND                           | 13.3 kΩ            |

| 0 V to 5 V             | AGND                                                                                                     | AGND                                     | V <sub>IN</sub>                | 10.0 kΩ            |

| 0 V to 4 V             | $V_{IN}$                                                                                                 | AGND                                     | V <sub>IN</sub>                | 10.7 kΩ            |

#### Table II. AD977 Analog Input Configuration

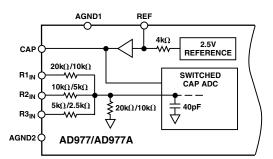

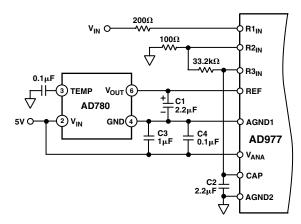

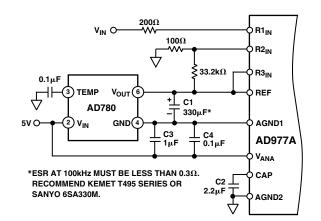

### ANALOG INPUTS

The AD977/AD977A is specified to operate with six full-scale analog input ranges. Connections required for each of the three analog inputs,  $R1_{IN}$ ,  $R2_{IN}$  and  $R3_{IN}$ , and the resulting full-scale ranges, are shown in Table I and Table II. The nominal input impedance for each analog input range is also shown. Table III shows the output codes for the ideal input voltages of each of the six analog input ranges.