# **Octal Channel Protectors**

**ADG467**

#### **FEATURES**

Fault and overvoltage protection up to ±40 V Signal paths open circuit with power off Signal path resistance of Ron with power on 44 V supply maximum ratings Low on resistance:  $62 \Omega$  typical ±1 nA maximum path current leakage @ +25°C Low R<sub>ON</sub> match (5 Ω maximum) Low power dissipation 0.8 µW typical **Latch-up proof construction**

#### **APPLICATIONS**

**ATE equipment** Sensitive measurement equipment Hot insertion rack systems

#### **GENERAL DESCRIPTION**

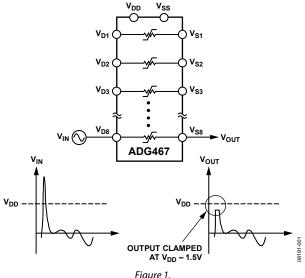

The ADG467 is an octal channel protector. The channel protector is placed in series with the signal path. The channel protector protects sensitive components from voltage transience in the signal path regardless if the power supplies are present or not. For this reason, the channel protectors are ideal for use in applications where correct power sequencing cannot always be guaranteed (for example, hot insertion rack systems) to protect analog inputs. This is described further, and some example circuits are given in the Applications Information section.

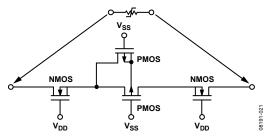

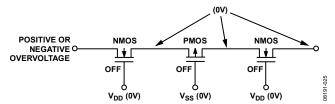

Each channel protector has an independent operation and consists of an N-channel MOSFET, a P-channel MOSFET, and an N-channel MOSFET, connected in series. The channel protector behaves just like a series resistor during normal operation, that is,  $(V_{SS} + 1.5 \text{ V}) < V_{IN} < (V_{DD} - 1.5 \text{ V})$ . When a channel's analog input exceeds the power supplies (including  $V_{DD}$  and  $V_{SS} = 0 \text{ V}$ ), one of the MOSFETs switches off, clamping the output to either  $V_{SS}$  + 1.5 V or  $V_{DD}$  – 1.5 V. Circuitry and signal source protection is provided in the event of an overvoltage or power loss. The channel protectors can withstand overvoltage inputs from −40 V to +40 V. See the Circuit Information section.

The ADG467 can operate off both bipolar and unipolar supplies. The channels are normally on when power is

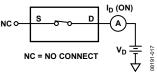

#### FUNCTIONAL BLOCK DIAGRAM

Figure 1.

connected and open circuit when power is disconnected. With power supplies of ±15 V, the on resistance of the ADG467 is 62  $\Omega$  typical with a leakage current of  $\pm 1$  nA maximum. When power is disconnected, the input leakage current is approximately ±0.5 nA typical.

The ADG467 is available in an 18-lead SOIC package and a 20-lead SSOP package.

#### **PRODUCT HIGHLIGHTS**

- Fault Protection.

- The ADG467 can withstand continuous voltage inputs from -40 V to +40 V. When a fault occurs due to the power supplies being turned off or due to an overvoltage being applied to the ADG467, the output is clamped. When power is turned off, current is limited to the microampere level.

- Low Power Dissipation.

- Low  $R_{ON}$ . 62  $\Omega$  typical.

- Trench Isolation Latch-Up Proof Construction. A dielectric trench separates the p- and n-channel MOSFETs thereby preventing latch-up.

| TABLE OF CONTENTS                                                                    |                                                         |

|--------------------------------------------------------------------------------------|---------------------------------------------------------|

| Features1                                                                            | Typical Performance Characteristics                     |

| Applications1                                                                        | Test Circuits                                           |

| Functional Block Diagram1                                                            | Circuit Information                                     |

| General Description1                                                                 | Overvoltage Protection                                  |

| Product Highlights                                                                   | Trench Isolation1                                       |

| Revision History                                                                     | Applications Information                                |

| Specifications                                                                       | Overvoltage and Power Supply Sequencing Protection 12   |

| Dual Supply 3                                                                        | High Voltage Surge Suppression 1:                       |

| Absolute Maximum Ratings                                                             | Outline Dimensions14                                    |

| ESD Caution4                                                                         | Ordering Guide1                                         |

| Pin Configuration and Function Descriptions5                                         |                                                         |

| REVISION HISTORY                                                                     |                                                         |

| 2/11—Rev. A to Rev. B                                                                | Added Test Circuits Section and Figure 16 to Figure 20  |

| Updated FormatUniversal                                                              | Changes to Overvoltage Protection Section and Figure 23 |

| Deleted ADG466                                                                       | Changes to Figure 24                                    |

| Changes to Features Section, General Description Section,                            | Change to Figure 26 1                                   |

| Figure 1, and Product Highlights Section 1                                           | Changes to Overvoltage and Power Supply Sequencing      |

| Changes to Power Requirements, V <sub>DD</sub> /V <sub>SS</sub> Parameter, Table 1 3 | Protection Section and Figure 27                        |

| Deleted 8-Lead DIP, SOIC, and μSOIC Pin Configuration 3                              | Changes to High Voltage Surge Suppression Section and   |

| Deleted Figure 12; Renumbered Sequentially5                                          | Figure 28 1                                             |

| Changes to Figure 4 to Figure 6                                                      | Changes to Outline Dimensions 1-                        |

| Added Figure 7; Renumbered Sequentially6                                             | Changes to Ordering Guide                               |

| Changes to Figure 11 to Figure 157                                                   |                                                         |

# **SPECIFICATIONS**

## **DUAL SUPPLY**

$V_{\text{DD}}$  = +15 V,  $V_{\text{SS}}$  = -15 V, GND = 0 V, unless otherwise noted.

Table 1.

| ADG467                                     |                       |                |           |                                                                     |  |

|--------------------------------------------|-----------------------|----------------|-----------|---------------------------------------------------------------------|--|

| Parameter                                  | +25°C                 | -40°C to +85°C | Unit      | Test Conditions/Comments                                            |  |

| FAULT PROTECTED CHANNEL                    |                       |                |           |                                                                     |  |

| Fault-Free Analog Signal Range             | $V_{SS} + 1.5$        |                | V typ     | Output open circuit                                                 |  |

|                                            | $V_{DD}-1.5$          |                | V typ     |                                                                     |  |

|                                            | V <sub>SS</sub> + 1.7 |                | V typ     | Output loaded, 1 mA                                                 |  |

|                                            | $V_{DD} - 1.7$        |                | V typ     |                                                                     |  |

| Ron                                        | 62                    | 80             | Ω typ     | $-10 \text{ V} \le V_{Sx} \le +10 \text{ V}, I_{Sx} = 1 \text{ mA}$ |  |

|                                            |                       | 95             | Ω max     |                                                                     |  |

| Ron Flatness                               |                       | 6              | Ω max     | $-5 \text{ V} \leq \text{V}_{\text{Sx}} \leq +5 \text{ V}$          |  |

| R <sub>ON</sub> Match between Channels     | 5                     | 6              | Ω max     | $V_{Sx} = \pm 10 \text{ V}, I_{Sx} = 1 \text{ mA}$                  |  |

| LEAKAGE CURRENTS                           |                       |                |           |                                                                     |  |

| Channel Output Leakage, Is(ON)             |                       |                |           | $V_{Sx} = V_{Dx} = \pm 10 \text{ V}$                                |  |

| (Without Fault Condition)                  | ±0.04                 | ±0.2           | nA typ    |                                                                     |  |

|                                            | ±1                    | ±5             | nA max    |                                                                     |  |

| Channel Input Leakage, I <sub>D(ON)</sub>  |                       |                |           | $V_{Sx} = \pm 25 \text{ V}$                                         |  |

| (with Fault Condition)                     | ±0.2                  | ±0.4           | nA typ    | $V_{Dx}$ = open circuit                                             |  |

|                                            | ±2                    | ±5             | nA max    |                                                                     |  |

| Channel Input Leakage, ID(OFF)             |                       |                |           | $V_{DD} = 0 V$ , $V_{SS} = 0 V$                                     |  |

| (with Power Off and Fault)                 | ±0.5                  | ±2             | nA typ    | $V_{Sx} = \pm 35 \text{ V}$                                         |  |

|                                            | ±2                    | ±10            | nA max    | $V_{Dx}$ = open circuit                                             |  |

| Channel Input Leakage, I <sub>D(OFF)</sub> |                       |                |           | $V_{DD} = 0 V, V_{SS} = 0 V$                                        |  |

| (with Power Off and Output Short Circuit)  | ±0.006                | ±0.16          | μA typ    | $V_{Sx} = \pm 35 \text{ V}, V_{Dx} = 0 \text{ V}$                   |  |

|                                            | ±0.015                | ±0.5           | μA max    |                                                                     |  |

| POWER REQUIREMENTS                         |                       |                |           |                                                                     |  |

| $I_{DD}$                                   | ±0.05                 |                | μA typ    |                                                                     |  |

|                                            | ±0.5                  | ±8             | μA max    |                                                                     |  |

| I <sub>SS</sub>                            | ±0.05                 |                | μA typ    |                                                                     |  |

|                                            | ±0.5                  | ±8             | μA max    |                                                                     |  |

| $V_{DD}/V_{SS}$                            |                       | ±4.5/±20       | V min/max |                                                                     |  |

## **ABSOLUTE MAXIMUM RATINGS**

$T_A = +25$ °C, unless otherwise noted.

Table 2

| 1 able 2.                                                                                |                          |

|------------------------------------------------------------------------------------------|--------------------------|

| Parameter                                                                                | Rating                   |

| V <sub>DD</sub> to V <sub>SS</sub>                                                       | +44 V                    |

| $V_{Sx_r}V_{Dx_r}$ Analog Input Overvoltage with Power On <sup>1</sup>                   | $V_{SS}-20VtoV_{DD}+20V$ |

| $V_{Sx}$ , $V_{Dx}$ , Analog Input Overvoltage with Power Off <sup>1</sup>               | -40 V to +40 V           |

| Continuous Current, V <sub>Sx</sub> , V <sub>Dx</sub>                                    | 20 mA                    |

| Peak Current, V <sub>sx</sub> , V <sub>Dx</sub> (Pulsed at 1 ms, 10% Duty Cycle Maximum) | 40 mA                    |

| Operating Temperature Range                                                              |                          |

| Industrial (B Version)                                                                   | -40°C to +85°C           |

| Storage Temperature Range                                                                | −65°C to +125°C          |

| Junction Temperature                                                                     | +150°C                   |

| SOIC Package                                                                             |                          |

| $\theta_{JA}$ , Thermal Impedance                                                        | 160°C/W                  |

| Lead Temperature, Soldering                                                              |                          |

| Vapor Phase (60 sec)                                                                     | +215°C                   |

| Infrared (15 sec)                                                                        | +220°C                   |

| SSOP Package                                                                             |                          |

| $\theta_{\scriptscriptstyle JA}$ , Thermal Impedance                                     | 130°C/W                  |

| Lead Temperature, Soldering                                                              |                          |

| Vapor Phase (60 sec)                                                                     | +215°C                   |

| Infrared (15 sec)                                                                        | +220°C                   |

|                                                                                          |                          |

$<sup>^1</sup>$  Overvoltages at  $V_{\text{sx}}$  or  $V_{\text{Dx}}$  are clamped by the channel protector; see the Circuit Information section.

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

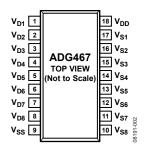

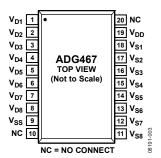

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 2. 18-Lead SOIC Pin Configuration

Figure 3. 20-Lead SSOP Pin Configuration

**Table 3. Pin Function Descriptions**

| Pir  | n No. |                 |                                                                                                           |

|------|-------|-----------------|-----------------------------------------------------------------------------------------------------------|

| SOIC | SSOP  | Mnemonic        | Description                                                                                               |

| 1    | 1     | V <sub>D1</sub> | Drain Terminal 1. This pin can be an input or an output.                                                  |

| 2    | 2     | $V_{D2}$        | Drain Terminal 2. This pin can be an input or an output.                                                  |

| 3    | 3     | $V_{D3}$        | Drain Terminal 3. This pin can be an input or an output.                                                  |

| 4    | 4     | $V_{D4}$        | Drain Terminal 4. This pin can be an input or an output.                                                  |

| 5    | 5     | $V_{D5}$        | Drain Terminal 5. This pin can be an input or an output.                                                  |

| 6    | 6     | $V_{D6}$        | Drain Terminal 6. This pin can be an input or an output.                                                  |

| 7    | 7     | $V_{D7}$        | Drain Terminal 7. This pin can be an input or an output.                                                  |

| 8    | 8     | $V_{D8}$        | Drain Terminal 8. This pin can be an input or an output.                                                  |

| 9    | 9     | V <sub>SS</sub> | Most Negative Power Supply Potential. In single-supply applications, this pin can be connected to ground. |

| N/A  | 10    | NC              | No Connect.                                                                                               |

| 10   | 11    | $V_{S8}$        | Source Terminal 1. This pin can be an input or an output.                                                 |

| 11   | 12    | $V_{S7}$        | Source Terminal 2. This pin can be an input or an output.                                                 |

| 12   | 13    | V <sub>S6</sub> | Source Terminal 3. This pin can be an input or an output.                                                 |

| 13   | 14    | $V_{S5}$        | Source Terminal 4. This pin can be an input or an output.                                                 |

| 14   | 15    | $V_{S4}$        | Source Terminal 5. This pin can be an input or an output.                                                 |

| 15   | 16    | $V_{S3}$        | Source Terminal 6. This pin can be an input or an output.                                                 |

| 16   | 17    | $V_{S2}$        | Source Terminal 7. This pin can be an input or an output.                                                 |

| 17   | 18    | V <sub>S1</sub> | Source Terminal 8. This pin can be an input or an output.                                                 |

| 18   | 19    | $V_{DD}$        | Most Positive Power Supply Potential.                                                                     |

| N/A  | 20    | NC              | No Connect. Do not connect to this pin.                                                                   |

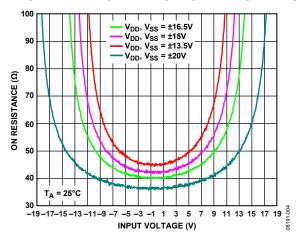

## TYPICAL PERFORMANCE CHARACTERISTICS

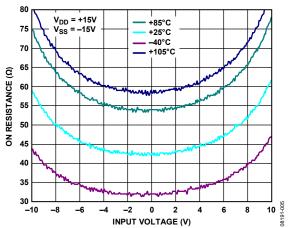

Figure 4. On Resistance as a Function of  $V_{DD}$  and  $V_{Sx}$  (Input Voltage), Dual Supply

Figure 5. On Resistance as a Function of Temperature and V<sub>Sx</sub> (Input Voltage)

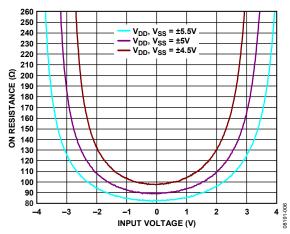

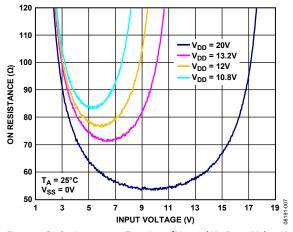

Figure 6. On Resistance as a Function of  $V_{DD}$  and  $V_{Sx}$  (Input Voltage), 5 V Dual Supply

Figure 7. On Resistance as a Function of  $V_{DD}$  and  $V_{Sx}$  (Input Voltage), Single Supply

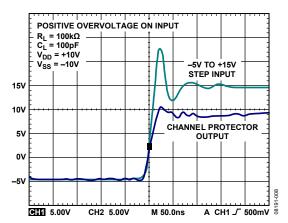

Figure 8. Positive Overvoltage Transience Response

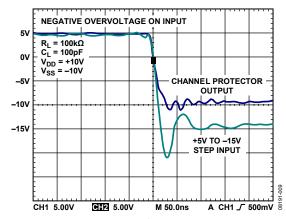

Figure 9. Negative Overvoltage Transience Response

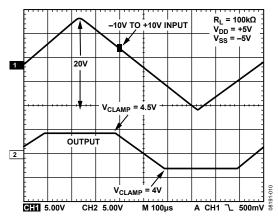

Figure 10. Overvoltage Ramp

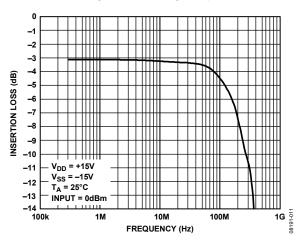

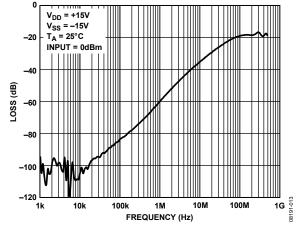

Figure 11. Frequency Response (Magnitude)

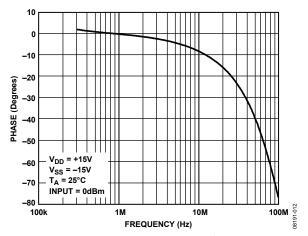

Figure 12. Frequency Response (Phase)

Figure 13. Crosstalk Between Adjacent Channels

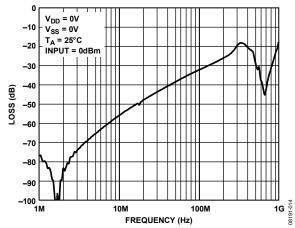

Figure 14. Off Isolation

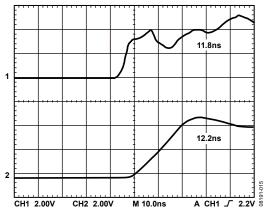

Figure 15. Propagation Delay

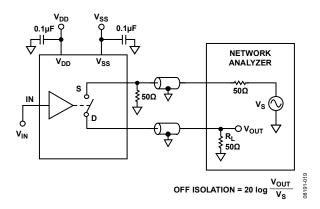

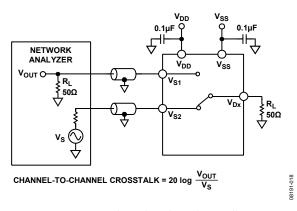

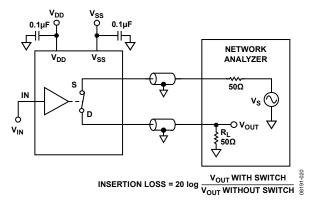

# **TEST CIRCUITS**

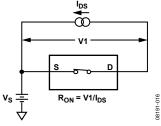

Figure 16. On Resistance

Figure 17. On Leakage

Figure 19. Off Isolation

Figure 18. Channel-to-Channel Crosstalk

Figure 20. Bandwidth

#### CIRCUIT INFORMATION

Figure 21 shows a simplified schematic of a channel protector circuit. The circuit is made up of four MOS transistors—two NMOS and two PMOS. One of the PMOS devices does not lie directly in the signal path but is used to connect the source of the second PMOS device to its backgate. This has the effect of lowering the threshold voltage and thus increasing the input signal range of the channel for normal operation. The source and backgate of the NMOS devices are connected for the same reason. During normal operation, the channel protectors have an on resistance of 62  $\Omega$  typical. The channel protectors are very low power devices, and even under fault conditions, the supply current is limited to sub microampere levels. All transistors are dielectrically isolated from each other using a trench isolation method. This makes it impossible to latch up the channel protectors. For further details, see the Trench Isolation section.

Figure 21. The Channel Protector Circuit

#### **OVERVOLTAGE PROTECTION**

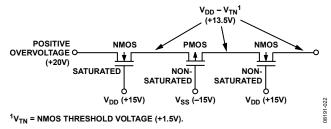

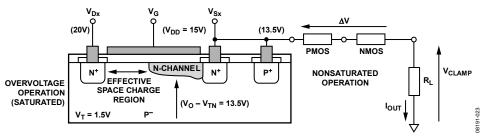

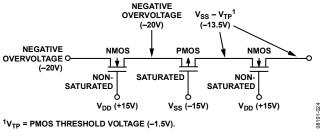

When a fault condition occurs on the input of a channel protector, the voltage on the input has exceeded some threshold voltage set by the supply rail voltages. The threshold voltages are related to the supply rails as follows. For a positive overvoltage, the threshold voltage is given by  $V_{\rm DD}-V_{\rm TN}$ , where  $V_{\rm TN}$  is the threshold voltage of the NMOS transistor (1.5 V typical). In the case of a negative overvoltage, the threshold voltage is given by  $V_{\rm SS}-V_{\rm TP}$ , where  $V_{\rm TP}$  is the threshold voltage of the PMOS device (–1.5 V typical). If the input voltage exceeds these threshold voltages,

the output of the channel protector (no load) is clamped at these threshold voltages. However, the channel protector output clamps at a voltage value that is inside these thresholds if the output is loaded. For example, with an output load of 1 k $\Omega$ ,  $V_{\rm DD}$  = 15 V, and a positive overvoltage on the input, the output clamps at  $V_{\rm DD}-V_{\rm TN}-\Delta V=15$  V -1.5 V -0.6 V = 12.9 V, where  $\Delta V$  is due to an I  $\times$  R voltage drop across the channels of the MOS devices (see Figure 23). As can be seen from Figure 23, the current during fault condition is determined by the load on the output (that is, V CLAMP/RL). However, if the supplies are off, the fault current is limited to the nano-ampere level.

Figure 22, Figure 24, and Figure 25 show the operating conditions of the signal path transistors during various fault conditions. Figure 22 shows how the channel protectors operate when a positive overvoltage is applied to the channel protector.

Figure 22. Positive Overvoltage on the Channel Protector

The first NMOS transistor goes into a saturated mode of operation as the voltage on its drain exceeds the gate voltage  $(V_{DD})$  – the threshold voltage  $(V_{TN})$ . This situation is shown in Figure 23. The potential at the source of the NMOS device is equal to  $V_{DD}-V_{TN}$ . The other MOS devices are in a nonsaturated mode of operation.

Figure 23. Positive Overvoltages Operation of the Channel Protector

When a negative overvoltage is applied to the channel protector circuit, the PMOS transistor enters a saturated mode of operation as the drain voltage exceeds  $V_{\text{SS}} - V_{\text{TP}}$  (see Figure 24). As in the case of the positive overvoltage, the other MOS devices are nonsaturated.

Figure 24. Negative Overvoltage on the Channel Protector

The channel protector is also functional when the supply rails are down (for example, power failure) or momentarily unconnected (for example, rack system). This is where the channel protector has an advantage over more conventional protection methods such as diode clamping (see the Applications Information section). When  $V_{\rm DD}$  and  $V_{\rm SS}$  equal 0 V, all transistors are off and the current is limited to subnano-ampere levels (see Figure 25).

Figure 25. Channel Protector Supplies Equal to 0 V

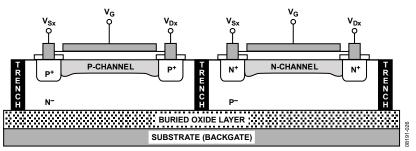

## TRENCH ISOLATION

The MOS devices that make up the channel protector are isolated from each other by an oxide layer (trench) (see Figure 26). When the NMOS and PMOS devices are not electrically isolated from each other, parasitic junctions between CMOS transistors may cause latch-up. Latch-up is caused when P-N junctions that are normally reverse biased become forward biased, causing large currents to flow, which can be destructive.

CMOS devices are normally isolated from each other by junction isolation. In junction isolation, the N and P wells of the CMOS transistors form a diode that is reverse biased under normal operation. However, during overvoltage conditions, this diode becomes forward biased. A silicon-controlled rectifier (SCR) type circuit is formed by the two transistors causing a significant amplification of the current that, in turn, leads to latch-up. With trench isolation, this diode is removed; the result is a latch-up-proof circuit.

Figure 26. Trench Isolation

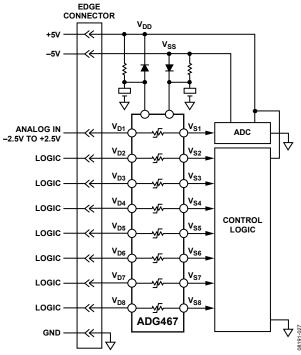

# APPLICATIONS INFORMATION OVERVOLTAGE AND POWER SUPPLY SEQUENCING PROTECTION

The ADG467 is ideal for use in applications where input overvoltage protection is required and correct power supply sequencing cannot always be guaranteed. The overvoltage protection ensures that the output voltage of the channel protector does not exceed the threshold voltages set by the supplies (see the Circuit Information section) when there is an overvoltage on the input. When the input voltage does not exceed these threshold voltages, the channel protector behaves like a series resistor (62  $\Omega$  typical). The resistance of the channel protector does vary slightly with operating conditions (see the Typical Performance Characteristics section).

The power sequencing protection is provided by the channel protector, which becomes a high resistance device when the supplies to the channel protector are not connected. Under this condition, all transistors in the channel protector are off and the only currents that flow are leakage currents, which are at the microampere level.

Figure 27 shows a typical application that requires overvoltage and power supply sequencing protection. The application shows a hot insertion rack system. This involves plugging a circuit board or module into a live rack via an edge connector. In this type of application, it is not possible to guarantee correct power supply sequencing. Correct power supply sequencing means that the power supplies should be connected before any external signals. Incorrect power sequencing can cause a CMOS device to latch up. This is true of most CMOS devices regardless of the functionality. RC networks are used on the supplies of the channel protector (see Figure 27) to ensure that the rest of the circuitry is powered up before the channel protectors. In this way, the outputs of the channel protectors are clamped well below V<sub>DD</sub> and Vss until the capacitors are charged. The diodes ensure that the supplies on the channel protector never exceed the supply rails of the board when it is being disconnected. This ensures that signals on the inputs of the CMOS devices never exceed the supplies.

Figure 27. Overvoltage and Power Supply Sequencing Protection

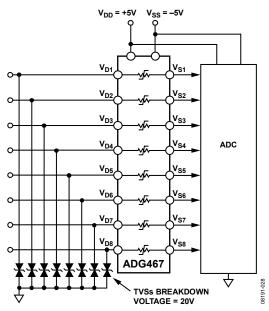

#### **HIGH VOLTAGE SURGE SUPPRESSION**

The ADG467 is not intended for use in high voltage applications like surge suppression. The ADG467 has breakdown voltages in excess of  $V_{SS}$  – 20 V and  $V_{DD}$  + 20 V on the inputs when the power supplies are connected. When the power supplies are disconnected, the breakdown voltages on the input of the channel protector are  $\pm 40$  V. In applications where inputs are likely to be subject to overvoltages exceeding the breakdown voltages specified for the channel protectors, transient voltage suppressors (TVSs) should be used. These devices are commonly used to protect vulnerable circuits from electric overstress such as that caused by electrostatic discharge, inductive load switching, and induced lightning. However, TVSs can have a substantial standby (leakage) current (300  $\mu$ A typical) at the reverse stand-off

voltage of a TVS is the normal peak operating voltage of the circuit. Also, a TVS offers no protection against latch-up of sensitive CMOS devices when the power supplies are off. The ideal solution is to use a channel protector in conjunction with a TVS to provide the optimal leakage current specification and circuit protection.

Figure 28 shows an input protection scheme that uses both a TVS and a channel protector. The TVS is selected with a reverse standoff voltage that is much greater than the operating voltage of the circuit (TVSs with higher breakdown voltages tend to have better standby leakage current specifications) but is inside the breakdown voltage of the channel protector. This circuit protects the circuitry regardless of whether the power supplies are present.

Figure 28. High Voltage Protection

## **OUTLINE DIMENSIONS**

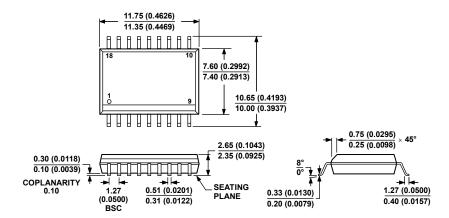

COMPLIANT TO JEDEC STANDARDS MS-013-AB

CONTROLLING DIMENSIONS ARE IN MILLIMETERS; INCH DIMENSIONS

(IN PARENTHESES) ARE ROUNDED-OFF MILLIMETER EQUIVALENTS FOR

REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN.

Figure 29. 18-Lead Standard Small Outline Package [SOIC\_W] Wide Body (RW-18) Dimensions shown in millimeters and (inches)

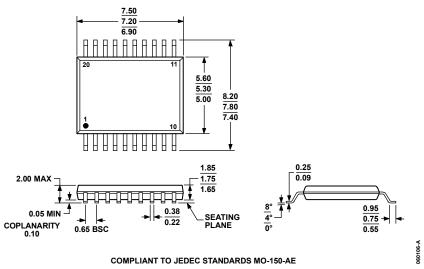

Figure 30. 20-Lead Shrink Small Outline Package [SSOP] (RS-20) Dimensions shown in millimeters

#### **ORDERING GUIDE**

| Model <sup>1</sup> Temperature Range |                | Package Description                             | Package Option |

|--------------------------------------|----------------|-------------------------------------------------|----------------|

| ADG467BR                             | −40°C to +85°C | 18-Lead Standard Small Outline Package [SOIC_W] | RW-18          |

| ADG467BR-REEL                        | −40°C to +85°C | 18-Lead Standard Small Outline Package [SOIC_W] | RW-18          |

| ADG467BR-REEL7                       | −40°C to +85°C | 18-Lead Standard Small Outline Package [SOIC_W] | RW-18          |

| ADG467BRZ                            | -40°C to +85°C | 18-Lead Standard Small Outline Package [SOIC_W] | RW-18          |

| ADG467BRZ-REEL                       | −40°C to +85°C | 18-Lead Standard Small Outline Package [SOIC_W] | RW-18          |

| ADG467BRZ-REEL7                      | -40°C to +85°C | 18-Lead Standard Small Outline Package [SOIC_W] | RW-18          |

| ADG467BRS                            | −40°C to +85°C | 20-Lead Shrink Small Outline Package [SSOP]     | RS-20          |

| ADG467BRS-REEL                       | -40°C to +85°C | 20-Lead Shrink Small Outline Package [SSOP]     | RS-20          |

| ADG467BRSZ                           | -40°C to +85°C | 20-Lead Shrink Small Outline Package [SSOP]     | RS-20          |

| ADG467BRSZ-REEL                      | −40°C to +85°C | 20-Lead Shrink Small Outline Package [SSOP]     | RS-20          |

$<sup>^{1}</sup>$  Z = RoHS Compliant Part.

NOTES

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

## **Analog Devices Inc.:**

ADG467BRZ-REEL7 ADG467BRSZ ADG467BRZ ADG467BR ADG467BR-REEL7 ADG467BRS ADG467BRSZ-REEL ADG467BRS-REEL ADG467BRZ-REEL ADG467BR-REEL