# AT24C32E

# **Atmel**

# I<sup>2</sup>C-Compatible (2-wire) Serial EEPROM 32-Kbit (4,096 x 8)

### DATASHEET

### **Features**

- Low Voltage Operation

- V<sub>CC</sub> = 1.7V to 3.6V

- Internally Organized as 4,096 x 8 (32K)

- I<sup>2</sup>C-compatible (2-wire) Serial Interface

- 100kHz Standard Mode, 1.7V to 3.6V

- 400kHz Fast Mode, 1.7V to 3.6V

- 1MHz Fast Mode Plus (FM+), 2.5V to 3.6V

- Schmitt Trigger Filtered Inputs for Noise Suppression

- Bidirectional Data Transfer Protocol

- Write Protect Pin for Full Array Hardware Data Protection

- Ultra Low Active Current (1mA max) and Standby Current (0.8µA Max)

- 32-byte Page Write Mode

- Partial Page Writes Allowed

- Random and Sequential Read Modes

- Self-timed Write Cycle Within 5ms Max

- High Reliability

- Endurance: 1,000,000 Write Cycles

- Data Retention: 100 Years

- Green Package Options (Lead-free/Halide-free/RoHS Compliant)

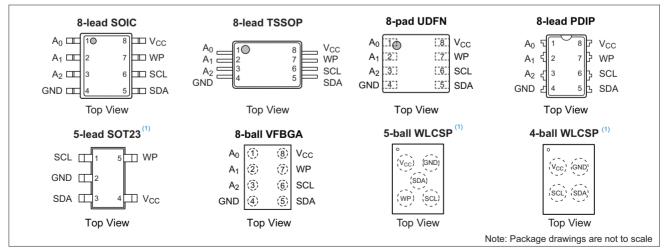

- 8-lead SOIC, 8-lead TSSOP, 8-pad UDFN, 8-lead PDIP<sup>(1)</sup>, 5-lead SOT23, 8-ball VFBGA, and 4-ball/5-ball WLCSP

- Die Sale Options: Wafer Form and Tape and Reel Available

### **Description**

The Atmel<sup>®</sup> AT24C32E provides 32,768 bits of Serial Electrically Erasable and Programmable Read-Only Memory (EEPROM) organized as 4,096 words of 8 bits each. The device's cascadable feature allows up to eight devices to share a common 2-wire bus. This device is optimized for use in many industrial and commercial applications where low-power and low voltage operation are essential. The device is available in space-saving 8-lead SOIC, 8-lead TSSOP, 8-pad UDFN, 8-lead PDIP<sup>(1)</sup>, 5-lead SOT23, 8-ball VFBGA, and 4- or 5-ball WLCSP packages. The entire family of packages operates from 1.7V to 3.6V.

Note: 1. Contact Atmel Sales for the availability of this package.

# 1. Pin Descriptions and Pinouts

| Pin<br>Number | Pin<br>Symbol                                    | Pin Name and Functional Description                                                                                                                                                                                                                                                                                                                                               | Asserted<br>State | Pin<br>Type |

|---------------|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-------------|

| 1, 2, 3       | A <sub>0</sub> , A <sub>1</sub> , A <sub>2</sub> | <b>Device Address Inputs:</b> The A <sub>0</sub> , A <sub>1</sub> , and A <sub>2</sub> pins are used to select the hardware device address and correspond to the fifth, sixth, and seventh bit of the I <sup>2</sup> C seven bit slave address. These pins can be directly connected to V <sub>CC</sub> or GND, allowing up to eight devices on the same bus.                     | _                 | Input       |

|               |                                                  | Refer to Note 1 for behavior of the pin when not connected.                                                                                                                                                                                                                                                                                                                       |                   |             |

| 4             | GND                                              | <b>Ground:</b> The ground reference for the power supply. GND should be connected to the system ground.                                                                                                                                                                                                                                                                           | —                 | Power       |

|               |                                                  | <b>Serial Data:</b> The SDA pin is an open-drain bidirectional input/output pin used to serially transfer data to and from the device.                                                                                                                                                                                                                                            |                   | Input/      |

| 5             | SDA                                              | The SDA pin must be pulled-high using an external pull-up resistor (not to exceed $10K\Omega$ in value) and may be wire-ORed with any number of other open-drain or open-collector pins from other devices on the same bus.                                                                                                                                                       | _                 | Output      |

| 6             | SCL                                              | <b>Serial Clock:</b> The SCL pin is used to provide a clock to the device and to control the flow of data to and from the device. Command and input data present on the SDA pin is always latched in on the rising edge of SCL, while output data on the SDA pin is clocked out on the falling edge of SCL. The SCL pin must either be forced high when the serial bus is idle or | _                 | Input       |

|               |                                                  | pulled-high using an external pull-up resistor.                                                                                                                                                                                                                                                                                                                                   |                   |             |

| 7             | WP                                               | <b>Write Protect:</b> Connecting the WP pin to GND will ensure normal write operations. When the WP pin is connected to $V_{CC}$ , all write operations to the memory are inhibited.                                                                                                                                                                                              | High              | Input       |

|               |                                                  | Refer to Note 1 for behavior of the pin when not connected.                                                                                                                                                                                                                                                                                                                       |                   |             |

| 8             | V <sub>CC</sub>                                  | <b>Device Power Supply:</b> The $V_{CC}$ pin is used to supply the source voltage to the device. Operations at invalid $V_{CC}$ voltages may produce spurious results and should not be attempted.                                                                                                                                                                                | _                 | Power       |

Table 1-1. Pin Descriptions

If the A<sub>0</sub>, A<sub>1</sub>, A<sub>2</sub>, or WP pins are not driven, they are internally pulled down to GND. In order to operate in a wide variety of application environments, the pull-down mechanism is intentionally designed to be somewhat strong. Once these pins are biased above the CMOS input buffer's trip point (~0.5 x V<sub>CC</sub>), the pull-down mechanism disengages. Atmel recommends connecting these pins to a known state whenever possible.

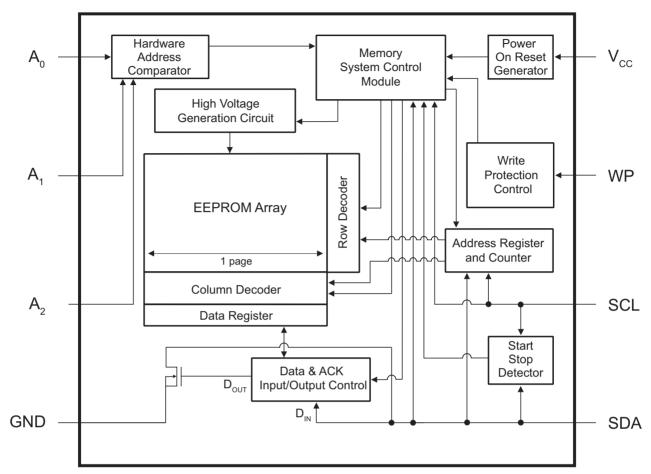

# 2. Device Block Diagram and System Configuration

Figure 2-1. Block Diagram

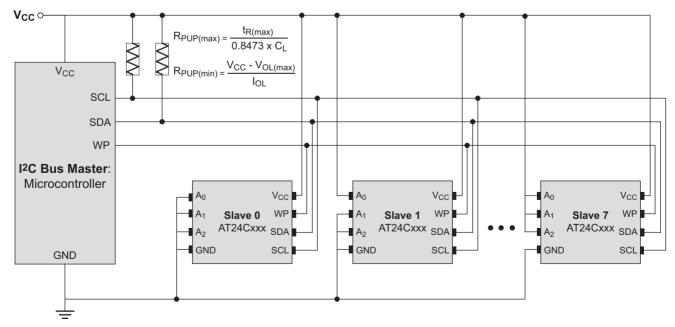

Figure 2-2. System Configuration Using 2-Wire Serial EEPROMs

Atmel

# 3. Device Operation and Communication

The AT24C32E operates as a slave device and utilizes a simple I<sup>2</sup>C-compatible 2-wire digital serial interface to communicate with a host controller, commonly referred to as the bus Master. The Master initiates and controls all read and write operations to the slave devices on the serial bus, and both the Master and the slave devices can transmit and receive data on the bus.

The serial interface is comprised of just two signal lines: Serial Clock (SCL) and Serial Data (SDA). The SCL pin is used to receive the clock signal from the Master, while the bidirectional SDA pin is used to receive command and data information from the Master, as well as, to send data back to the Master. Data is always latched into the AT24C32E on the rising edge of SCL and always output from the device on the falling edge of SCL. Both the SCL and SDA pin incorporate integrated spike suppression filters and Schmitt Triggers to minimize the effects of input spikes and bus noise.

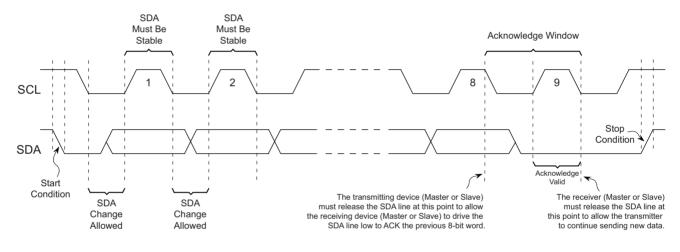

All command and data information is transferred with the Most-Significant Bit (MSB) first. During bus communication, one data bit is transmitted every clock cycle, and after eight bits (one byte) of data have been transferred, the receiving device must respond with either an Acknowledge (ACK) or a No-Acknowledge (NACK) response bit during a ninth clock cycle (ACK/NACK clock cycle) generated by the Master. Therefore, nine clock cycles are required for every one byte of data transferred. There are no unused clock cycles during any read or write operation, so there must not be any interruptions or breaks in the data stream during each data byte transfer and ACK or NACK clock cycle.

During data transfers, data on the SDA pin must only change while SCL is low, and the data must remain stable while SCL is high. If data on the SDA pin changes while SCL is high, then either a Start or a Stop condition will occur. Start and Stop conditions are used to initiate and end all serial bus communication between the Master and the slave devices. The number of data bytes transferred between a Start and a Stop condition is not limited and is determined by the Master. In order for the serial bus to be idle, both the SCL and SDA pins must be in the logic-high state at the same time.

### 3.1 Clock and Data Transition Requirements

The SDA pin is an open drain terminal and therefore must be pulled high with an external pull-up resistor. Data on the SDA pin may change only during SCL low time periods. Data changes during SCL high periods will indicate a Start or Stop condition as defined below.

### 3.2 Start and Stop Conditions

### 3.2.1 Start Condition

A Start condition occurs when there is a high-to-low transition on the SDA pin while the SCL pin is at a stable Logic 1 state and will bring the device out of standby mode. The Master uses a Start condition to initiate any data transfer sequence, therefore every command must begin with a Start condition. The device will continuously monitor the SDA and SCL pins for a Start condition but will not respond unless one is detected. Please refer to Figure 3-1 for more details.

### 3.2.2 Stop Condition

A Stop condition occurs when there is a low-to-high transition on the SDA pin while the SCL pin is stable in the Logic 1 state. The Master can use the Stop condition to end a data transfer sequence with the AT24C32E which will subsequently return to standby mode. The Master can also utilize a repeated Start condition instead of a Stop condition to end the current data transfer if the Master will perform another operation. Please refer to Figure 3-1 for more details.

### 3.3 Acknowledge and No-Acknowledge

After every byte of data is received, the receiving device must confirm to the Master that it has successfully received the data byte by responding with what is known as an acknowledge (ACK). An ACK is accomplished by the transmitting device first releasing the SDA line at the falling edge of the eighth clock cycle followed by the receiving device responding with a Logic 0 during the entire high period of the ninth clock cycle.

When the AT24C32E is transmitting data to the Master, the Master can indicate that it is done receiving data and wants to end the operation by sending a Logic 1 response to the AT24C32E instead of an ACK response during the ninth clock cycle. This is known as a no-acknowledge (NACK) and is accomplished by the Master sending a Logic 1 during the ninth clock cycle, at which point the AT24C32E will release the SDA line so the Master can then generate a Stop condition.

The transmitting device, which can be the bus Master or the Serial EEPROM, must release the SDA line at the falling edge of the eighth clock cycle to allow the receiving device to drive the SDA line to a Logic 0 to ACK the previous 8-bit word. The receiving device must release the SDA line at the end of the ninth clock cycle to allow the transmitter to continue sending new data. A timing diagram has been provided in Figure 3-1 to better illustrate these requirements.

### Figure 3-1. Start Condition, Data Transitions, Stop Condition and Acknowledge

### 3.4 Standby Mode

The AT24C32E features a low-power standby mode which is enabled when any one of the following occurs:

- A valid power-up sequence is performed (see Section 8.6, "Power-Up Requirements and Reset Behavior").

- A Stop condition is received by the device unless it initiates an internal write cycle (see Section 5., "Write Operations").

- At the completion of an internal write cycle (see Section 5.).

- An unsuccessful match of the device type identifier or hardware address in the Device Address byte occurs (see Section 4.1, "Device Addressing").

- The bus Master does not ACK the receipt of data read out from the device; instead it sends a NACK response. (see Section 6., "Read Operations").

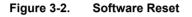

### 3.5 Software Reset

After an interruption in protocol, power loss, or system reset, any 2-wire part can be protocol reset by following these steps:

- 1. Create a Start condition (if possible).

- 2. Clock nine cycles.

- 3. Create another Start condition followed by a Stop condition as seen in Figure 3-2.

The device will be ready for the next communication after the above steps have been completed. The device should be ready for the next communication after above steps have been completed. In the event that the device is still non-responsive or remains active on the SDA bus, a power cycle must be used to reset the device (see Section 8.6.1, "Device Reset").

# 4. Memory Organization

The AT24C32E is internally organized as 128 pages of 32 bytes each.

### 4.1 Device Addressing

Accessing the device requires an 8-bit Device Address word following a Start condition to enable the device for a read or write operation. Since multiple slave devices can reside on the serial bus each slave device must have its own unique address so the Master can access each device independently.

The most significant four bits of the Device Address word is referred to as the device type identifier. The device type identifier `1010' (Ah) is required in bits seven through four of the Device Address byte (Table 4-1).

Following the 4-bit device type identifier are the hardware slave address bits,  $A_0$ ,  $A_1$ , and  $A_2$ . These bits can be used to expand the address space by allowing up to eight 32-Kbit Serial EEPROM devices on the same bus. These hardware slave address bits must correlate with the voltage level on the corresponding hardwired input pins  $A_0$ ,  $A_1$ , and  $A_2$ .

The  $A_0$ ,  $A_1$ , and  $A_2$  pins use an internal proprietary circuit that automatically biases the pin to a Logic 0 state if the pin is allowed to float. In order to operate in a wide variety of application environments, the pull-down mechanism is intentionally designed to be somewhat strong. Once the pin is biased above the CMOS input buffer's trip point (~0.5 x V<sub>CC</sub>), the pull-down mechanism disengages. Atmel recommends connecting the  $A_0$ ,  $A_1$ , and  $A_2$  pin to a known state whenever possible.

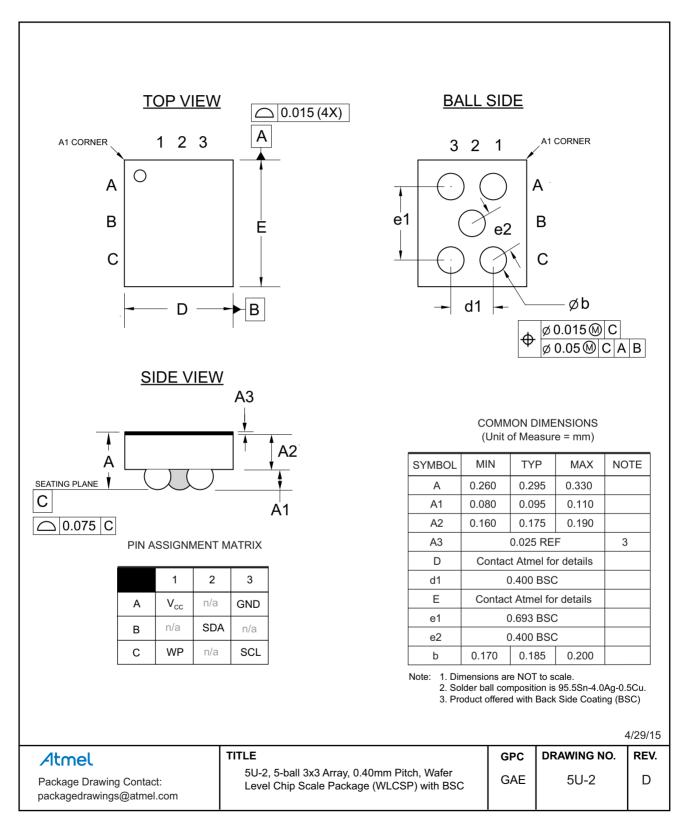

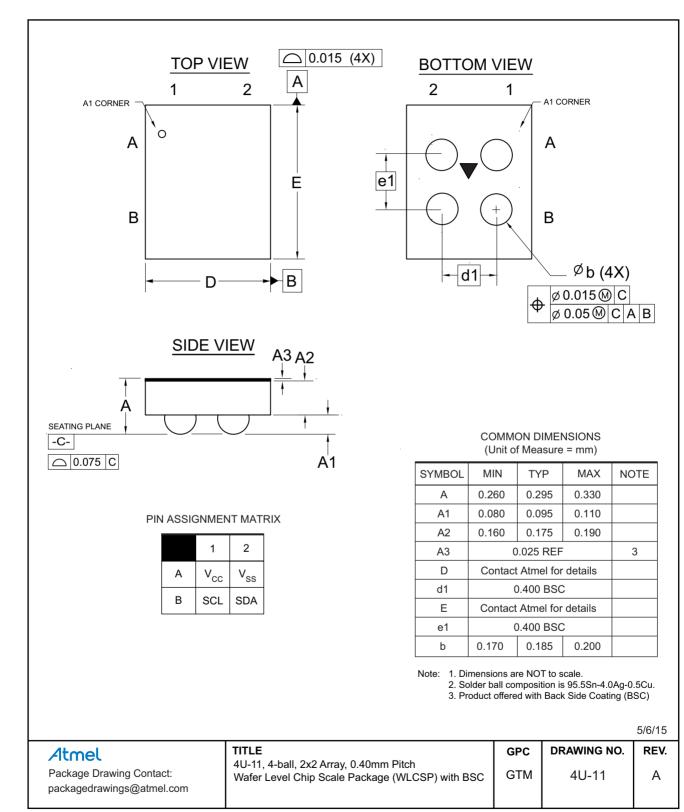

When using the SOT23 and WLCSP packages, the  $A_0$ ,  $A_1$ , and  $A_2$  pins are not accessible and are left floating. The previously mentioned automatic pull-down circuit will set this pin to a Logic 0 state. As a result, to properly communicate with the device in the SOT23 and WLCSP packages, the  $A_0$ ,  $A_1$ , and  $A_2$  software bits must always be set to Logic 0 for any operation.

The eighth bit (bit 0) of the Device Address byte is the read/write operation select bit. A read operation is initiated if this bit is high and a write operation is initiated if this bit is low.

Upon the successful comparison of the Device Address byte, the AT24C32E will return an ACK. If a valid comparison is not made, the device will NACK and return to a standby state.

|                                   | Device Type Identifier |       |       | Hardware | Read/<br>Write |                |                |       |

|-----------------------------------|------------------------|-------|-------|----------|----------------|----------------|----------------|-------|

| Package                           | Bit 7                  | Bit 6 | Bit 5 | Bit 4    | Bit 3          | Bit 2          | Bit 1          | Bit 0 |

| SOIC, TSSOP, UDFN,<br>PDIP, VFBGA | 1                      | 0     | 1     | 0        | A <sub>2</sub> | A <sub>1</sub> | A <sub>0</sub> | R/W   |

| SOT23, WLCSP                      | 1                      | 0     | 1     | 0        | 0              | 0              | 0              | R/W   |

### Table 4-1. Device Address Byte

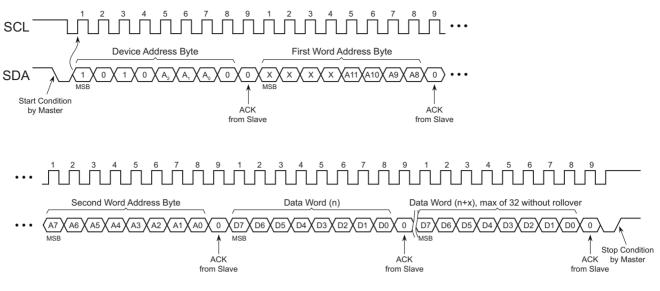

For all operations (except the Current Address Read), a two 8-bit Word Address byte must be transmitted to the device immediately following the Device Address byte. The Word Address bytes consist of the 12-bit memory array word address, and is used to specify which byte location in the EEPROM to start reading or writing.

The first Word Address byte contains the four most significant bits of the word address (A11 through A8) in bit positions three through zero, as seen in Table 4-2. The remainder of the first Word Address byte are don't care bits and (in bit positions seven through four) as they all outside of the addressable 32-Kbit range. Upon completion of the first Word Address byte, the AT24C32E will return an ACK.

### Table 4-2. First Word Address Byte

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| Х     | Х     | x     | Х     | A11   | A10   | A9    | A8    |

Note: Bit 7 through Bit 4 are don't care values as they fall outside the addressable 32-Kbit range.

Next, the second Word Address byte is sent to the device which provides the remaining eight bits of the word address (A7 though A0). Upon completion of the second Word Address byte, the AT24C32E will return an ACK. Please consult Table 4-3 to review these bit positions.

### Table 4-3. Second Word Address Byte

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| A7    | A6    | A5    | A4    | A3    | A2    | A1    | A0    |

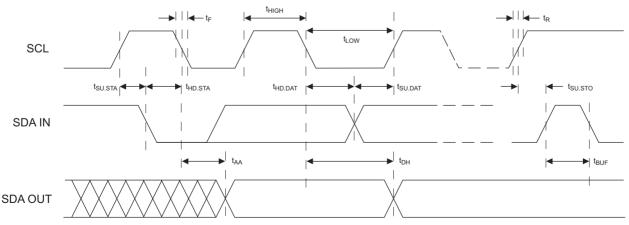

The relationship of the AC timing parameters with respect to SCL and SDA for the AT24C32E are shown in the timing waveform Figure 8-1 on page 15. The AC timing characteristics and specifications are outlined in Section 8.4 "AC Characteristics" on page 15.

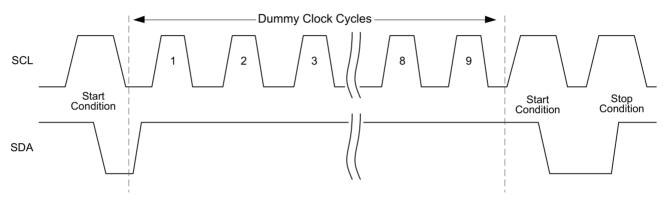

## 5. Write Operations

All write operations for the AT24C32E begin with the Master sending a Start condition, followed by a Device Address byte with the R/W bit set to 0', and then by the Word Address bytes. The data value(s) to be written to the device immediately follow the Word Address bytes.

### 5.1 Byte Write

The AT24C32E supports the writing of single 8-bit bytes. Selecting a data word in the AT24C32E requires a 12-bit word address.

Upon receipt of the proper Device Address and Word Address bytes, the EEPROM will send an Acknowledge. The device will then be ready to receive the first 8-bit data word. Following receipt of the 8-bit data word, the EEPROM will respond with an Acknowledge. The addressing device, such as a bus Master, must then terminate the Write operation with a Stop condition. At that time the EEPROM will enter an internally self-timed write cycle, which will be completed within  $t_{WR}$ , while the data word is being programmed into the nonvolatile EEPROM. All inputs are disabled during this write cycle, and the EEPROM will not respond until the Write is complete.

### Figure 5-1. Byte Write

### 5.2 Page Write

A Page Write operation allows up to 32 bytes to be written in the same write cycle, provided all bytes are in the same row of the memory array (where address bits A11 through A5 are the same). Partial Page Writes of less than 32 bytes are also allowed.

A Page Write is initiated the same way as a Byte Write, but the bus Master does not send a Stop condition after the first data word is clocked in. Instead, after the EEPROM acknowledges receipt of the first data word, the bus Master can transmit up to thirty one additional data words. The EEPROM will respond with an ACK after each data word is received. Once all data to be written has been sent to the device, the bus Master must issue a Stop condition (Figure 5-2) at which time the internally self-timed write cycle will begin.

The lower five bits of the word address are internally incremented following the receipt of each data word. The higher order address bits are not incremented and retain the memory page row location. Page Write operations are limited to writing bytes within a single physical page, regardless of the number of bytes actually being written. When the incremented word address reaches the page boundary, the address counter will "roll over" to the beginning of the same page. Nevertheless, creating a roll over event should be avoided as previously loaded data in the page could become unintentionally altered.

# Atmel

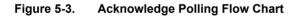

### 5.3 Acknowledge Polling

An Acknowledge Polling routine can be implemented to optimize time sensitive applications that would prefer not to wait the fixed maximum write cycle time ( $t_{WR}$ ). This method allows the application to know immediately when the Serial EEPROM write cycle has completed, so a subsequent operation can be started.

Once the internally self-timed write cycle has started, an Acknowledge Polling routine can be initiated. This involves repeatedly sending a Start condition followed by a valid Device Address byte with the R/W bit set at Logic 0. The device will not respond with an ACK while the write cycle is ongoing. Once the internal write cycle has completed, the EEPROM will respond with an ACK, allowing a new Read or Write operation to be immediately initiated. A flow chart has been included below in Figure 5-3 to better illustrate this technique.

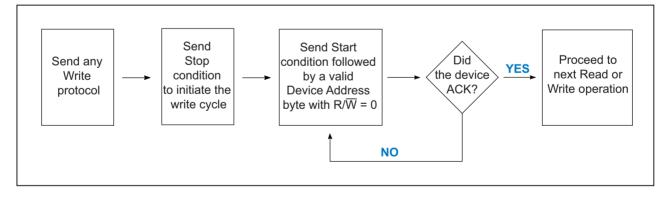

### 5.4 Write Cycle Timing

The length of the self-timed write cycle, or  $t_{WR}$ , is defined as the amount of time from the Stop condition that begins the internal Write operation, to the Start condition of the first Device Address byte sent to the AT24C32E that it subsequently responds to with an ACK. Figure 5-4 has been included to show this measurement. During the internally self-timed write cycle, any attempts to read from or write to the memory array will not be processed.

Atmel

Figure 5-4. Write Cycle Timing

### 5.5 Write Protection

Atmel

The AT24C32E utilizes a hardware data protection scheme that allows the user to write protect the entire memory contents when the WP pin is at  $V_{CC}$  (or a valid  $V_{IH}$ ). No write protection will be set if the WP pin is at GND or left floating. The 4-ball WLCSP version of the device does not include any write protection features.

| Table 5-1. | AT24C32E Write Protect Behavior |

|------------|---------------------------------|

|------------|---------------------------------|

| WP Pin Voltage  | Part of the Array Protected         |

|-----------------|-------------------------------------|

| V <sub>CC</sub> | Full Array                          |

| GND             | None — Write Protection Not Enabled |

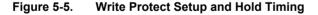

The status of the WP pin is sampled at the Stop condition for every Byte Write or Page Write command prior to the start of an internally self-timed Write operation. Changing the WP pin state after the Stop condition has been sent will not alter or interrupt the execution of the write cycle. The WP pin state must be valid with respect to the associated setup ( $t_{SU.WP}$ ) and hold ( $t_{HD.WP}$ ) timing as shown in the Figure 5-5 below. The WP setup time is the amount of time that the WP state must be stable before the Stop condition is issued. The WP hold time is the amount of time after the Stop condition that the WP state must remain stable.

If an attempt is made to write to the device while the WP pin has been asserted, the device will acknowledge the Device Address, Word Address, and Data bytes but no write cycle will occur when the Stop condition is issued, and the device will immediately be ready to accept a new Read or Write command.

## 6. Read Operations

Read operations are initiated the same way as Write operations with the exception that the Read/Write Select bit in the Device Address word must be a Logic 1. There are three Read operations:

- Current Address Read

- Random Address Read

- Sequential Read

### 6.1 Current Address Read

The internal data word address counter maintains the last address accessed during the last read or write operation, incremented by one. This address stays valid between operations as long as the  $V_{CC}$  is maintained to the part. The address "roll over" during read is from the last byte of the last page to the first byte of the first page of the memory.

A Current Address Read operation will output data according to the location of the internal data word address counter. This is initiated with a Start condition, followed by a valid Device Address byte with the  $R/\overline{W}$  bit set to Logic 1. The device will ACK this sequence and the current address data word is serially clocked out on the SDA line. All types of Read operations will be terminated if the bus Master does not respond with an ACK (it NACKs) during the ninth clock cycle, which will force the device into standby mode. After the NACK response, the Master may send a Stop condition to complete the protocol, or it can send a Start condition to begin the next sequence.

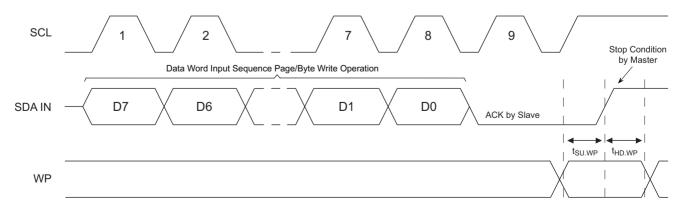

#### Figure 6-1. Current Address Read

### 6.2 Random Read

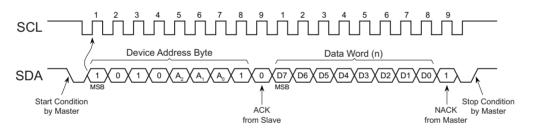

A Random Read begins in the same way as a Byte Write operation does to load in a new data word address. This is known as a "dummy write" sequence; however, the Data Byte and Stop condition of the Byte Write must be omitted to prevent the part from entering an internal write cycle. Once the Device Address and Word Address bytes are clocked in and acknowledged by the EEPROM, the bus Master must generate another Start condition. The bus Master now initiates a Current Address Read by sending a Start condition, followed by a valid Device Address byte with the R/W bit set to Logic 1. The EEPROM will ACK the Device Address and serially clock out the data word on the SDA line. All types of Read operations will be terminated if the bus Master does not respond with an ACK (it NACKs) during the ninth clock cycle, which will force the device into standby mode. After the NACK response, the Master may send a Stop condition to complete the protocol, or it can send a Start condition to begin the next sequence.

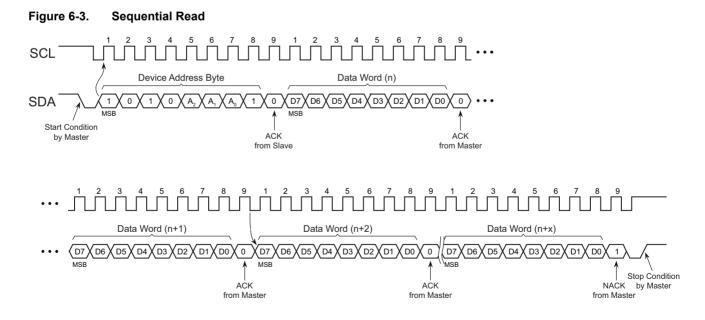

### 6.3 Sequential Read

Sequential Reads are initiated by either a Current Address Read or a Random Read. After the bus Master receives a data word, it responds with an acknowledge. As long as the EEPROM receives an ACK, it will continue to increment the word address and serially clock out sequential data words. When the maximum memory address is reached, the data word address will "roll over" and the sequential read will continue from the beginning of the memory array. All types of Read operations will be terminated if the bus Master does not respond with an ACK (it NACKs) during the ninth clock cycle, which will force the device into standby mode. After the NACK response, the Master may send a Stop condition to complete the protocol, or it can send a Start condition to begin the next sequence.

# 7. Device Default Condition from Atmel

The AT24C32E is delivered with the EEPROM array set to Logic 1, resulting in FFh data in all locations.

# Atmel

# 8. Electrical Specifications

### 8.1 Absolute Maximum Ratings

| Temperature under Bias55°C to +125°C                                              |

|-----------------------------------------------------------------------------------|

| Storage Temperature65°C to +150°C                                                 |

| Supply Voltage with respect to ground0.5V to +4.10V                               |

| Voltage on any pin with respect to ground $\dots -0.6V$ to V <sub>CC</sub> + 0.5V |

| DC Output Current 5.0mA                                                           |

Functional operation at the "Absolute Maximum Ratings" or any other conditions beyond those indicated in Section 8.2 "DC and AC Operating Range" is not implied or guaranteed. Stresses beyond those listed under "Absolute Maximum Ratings" and/or exposure to the "Absolute Maximum Ratings" for extended periods may affect device reliability and cause permanent damage to the device.

The voltage extremes referenced in the "Absolute Maximum Ratings" are intended to accommodate short duration undershoot/overshoot pulses that the device may be subjected to during the course of normal operation and does not imply or guarantee functional device operation at these levels for any extended period of time.

### 8.2 DC and AC Operating Range

### Table 8-1. DC and AC Operating Range

|                              |                              | AT24C32E       |

|------------------------------|------------------------------|----------------|

| Operating Temperature (Case) | Industrial Temperature Range | -40°C to +85°C |

| V <sub>CC</sub> Power Supply | Low Voltage Grade            | 1.7V to 3.6V   |

### 8.3 DC Characteristics

#### Table 8-2.DC Characteristics

Parameters are applicable over the operating range in specified Section 8.2, unless otherwise noted.

| Symbol           | Parameter                       | Test Conditio                         | ns                                       | Min                   | Typical <sup>(1)</sup> | Мах                   | Units |

|------------------|---------------------------------|---------------------------------------|------------------------------------------|-----------------------|------------------------|-----------------------|-------|

| V <sub>cc</sub>  | Supply Voltage                  |                                       |                                          | 1.7                   |                        | 3.6                   | V     |

| 1                | Supply Current, Read            | $V_{\rm CC} = 1.8V^{(2)}$             | Read at 400kHz                           |                       | 0.08                   | 0.3                   | mA    |

| I <sub>CC1</sub> | Supply Current, Reau            | V <sub>CC</sub> = 3.6V                | Read at 1MHz                             |                       | 0.15                   | 0.5                   | mA    |

| I <sub>CC2</sub> | Supply Current, Write           | V <sub>CC</sub> = 3.6V                | Write at 1MHz                            |                       | 0.20                   | 1.0                   | mA    |

| 1                | Standby Current                 | $V_{\rm CC} = 1.8V^{(2)}$             | $V_{IN} = V_{CC} \text{ or } V_{SS}$     |                       | 0.08                   | 0.4                   | μA    |

| I <sub>SB</sub>  |                                 | V <sub>CC</sub> = 3.6V                | $v_{\rm IN} - v_{\rm CC}  O  v_{\rm SS}$ |                       | 0.10                   | 0.8                   | μA    |

| ILI              | Input Leakage Current           | $V_{IN} = V_{CC} \text{ or } V_{S}$   | S                                        |                       | 0.10                   | 3.0                   | μA    |

| I <sub>LO</sub>  | Output Leakage Current          | $V_{OUT} = V_{CC} \text{ or } V_{CC}$ | V <sub>SS</sub>                          |                       | 0.05                   | 3.0                   | μA    |

| V <sub>IL</sub>  | Input Low Level <sup>(2)</sup>  |                                       |                                          | -0.6                  |                        | V <sub>CC</sub> x 0.3 | V     |

| V <sub>IH</sub>  | Input High Level <sup>(2)</sup> |                                       |                                          | V <sub>CC</sub> x 0.7 |                        | V <sub>CC</sub> + 0.5 | V     |

| V <sub>OL1</sub> | Output Low Level                | V <sub>CC</sub> = 1.8V                | I <sub>OL</sub> = 0.15mA                 |                       |                        | 0.2                   | V     |

| V <sub>OL2</sub> | Output Low Level                | V <sub>CC</sub> = 3.0V                | I <sub>OL</sub> = 2.1mA                  |                       |                        | 0.4                   | V     |

Notes: 1. Typical values characterized at  $T_A = +25^{\circ}C$  unless otherwise noted.

2. This parameter is characterized but is not 100% tested in production.

### 8.4 AC Characteristics

### Table 8-3. AC Characteristics

Parameters are applicable over operating range in Section 8.2 unless otherwise noted. Test conditions shown in Note 2.

|                     |                                                         | Standard Mode<br>V <sub>CC</sub> = 1.7V to 3.6V |       | Fast                           | Mode | Fast Mo                 | ode Plus |       |

|---------------------|---------------------------------------------------------|-------------------------------------------------|-------|--------------------------------|------|-------------------------|----------|-------|

|                     |                                                         |                                                 |       | V <sub>CC</sub> = 1.7V to 3.6V |      | $V_{CC} = 2.5V$ to 3.6V |          |       |

| Symbol              | Parameter                                               | Min                                             | Max   | Min                            | Max  | Min                     | Max      | Units |

| f <sub>SCL</sub>    | Clock Frequency, SCL                                    |                                                 | 100   |                                | 400  |                         | 1000     | kHz   |

| t <sub>LOW</sub>    | Clock Pulse Width Low                                   | 4,700                                           |       | 1300                           |      | 500                     |          | ns    |

| t <sub>HIGH</sub>   | Clock Pulse Width High                                  | 4,000                                           |       | 600                            |      | 400                     |          | ns    |

| t <sub>i</sub>      | Input Filter Spike Suppression (SCL,SDA) <sup>(1)</sup> |                                                 | 100   |                                | 100  |                         | 100      | ns    |

| t <sub>AA</sub>     | Clock Low to Data Out Valid                             |                                                 | 4,500 |                                | 900  |                         | 450      | ns    |

| t <sub>BUF</sub>    | Bus Free Time between Stop and Start <sup>(1)</sup>     | 4,700                                           |       | 1300                           |      | 500                     |          | ns    |

| t <sub>HD.STA</sub> | Start Condition Hold Time                               | 4,000                                           |       | 600                            |      | 250                     |          | ns    |

| t <sub>SU.STA</sub> | Start Condition Set-up Time                             | 4,700                                           |       | 600                            |      | 250                     |          | ns    |

| t <sub>HD.DAT</sub> | Data In Hold Time                                       | 0                                               |       | 0                              |      | 0                       |          | ns    |

| t <sub>SU.DAT</sub> | Data In Set-up Time                                     | 200                                             |       | 100                            |      | 100                     |          | ns    |

| t <sub>R</sub>      | Inputs Rise Time <sup>(1)</sup>                         |                                                 | 1,000 |                                | 300  |                         | 100      | ns    |

| t <sub>F</sub>      | Inputs Fall Time <sup>(1)</sup>                         |                                                 | 300   |                                | 300  |                         | 100      | ns    |

| t <sub>SU.STO</sub> | Stop Condition Set-up Time                              | 4,700                                           |       | 600                            |      | 250                     |          | ns    |

| t <sub>SU.WP</sub>  | Write Protect Setup Time                                | 4,000                                           |       | 600                            |      | 100                     |          | ns    |

| t <sub>HD.WP</sub>  | Write Protect Hold Time                                 | 4,000                                           |       | 600                            |      | 400                     |          | ns    |

| t <sub>DH</sub>     | Data Out Hold Time                                      | 100                                             |       | 50                             |      | 50                      |          | ns    |

| t <sub>WR</sub>     | Write Cycle Time                                        |                                                 | 5     |                                | 5    |                         | 5        | ms    |

Notes: 1. These parameters are determined through product characterization and are not 100% tested in production.

- 2. AC measurement conditions:

- C<sub>L</sub> : 100pF

- $R_{PUP}^{-}$  (SDA bus line pull-up resistor to V<sub>CC</sub>): 1.3k $\Omega$  (1000kHz), 4k $\Omega$  (400kHz), 10k $\Omega$  (100kHz)

- Input pulse voltages: 0.3 x V<sub>CC</sub> to 0.7 x V<sub>CC</sub>

- Input rise and fall times:  $\leq$  50ns

- Input and output timing reference voltages: 0.5 x V<sub>CC</sub>

#### Figure 8-1. Bus Timing

### 8.5 Pin Capacitance

#### Table 8-4.Pin Capacitance<sup>(1)</sup>

Applicable over recommended operating range from  $T_A = 25^{\circ}C$ , f = 1.0MHz,  $V_{CC} = 3.6V$

| Symbol           | Test Condition                                                             | Мах | Units | Conditions           |

|------------------|----------------------------------------------------------------------------|-----|-------|----------------------|

| C <sub>I/O</sub> | Input/Output Capacitance (SDA)                                             | 8   | pF    | $V_{I/O} = 0V$       |

| C <sub>IN</sub>  | Input Capacitance (A <sub>0</sub> , A <sub>1</sub> , A <sub>2</sub> , SCL) | 6   | pF    | V <sub>IN</sub> = 0V |

Note: 1. This parameter is characterized but is not 100% tested in production.

### 8.6 Power-Up Requirements and Reset Behavior

During a power-up sequence, the V<sub>CC</sub> supplied to the AT24C32E should monotonically rise from GND to the minimum V<sub>CC</sub> level as specified in Section 8.2, "DC and AC Operating Range" with a slew rate no greater than  $1V/\mu s$ .

#### 8.6.1 Device Reset

To prevent inadvertent write operations or other spurious events from happening during a power-up sequence, the AT24C32E includes a power-on-reset (POR) circuit. Upon power-up, the device will not respond to any commands until the  $V_{CC}$  level crosses the internal voltage threshold ( $V_{POR}$ ) that brings the device out of reset and into standby mode.

The system designer must ensure that instructions are not sent to the device until the V<sub>CC</sub> supply has reached a stable value greater than or equal to the minimum V<sub>CC</sub> level. Additionally, once the V<sub>CC</sub> is greater than or equal to the minimum V<sub>CC</sub> level, the bus Master must wait at least t<sub>PUP</sub> before sending the first command to the device. See Table 8-5 for the values associated with these power-up parameters.

#### Table 8-5.Power-up Conditions<sup>(1)</sup>

| Symbol            | Parameter                                                                            | Min | Max | Units |

|-------------------|--------------------------------------------------------------------------------------|-----|-----|-------|

| t <sub>PUP</sub>  | Time required after $V_{\text{CC}}$ is stable before the device can accept commands. | 100 |     | μs    |

| V <sub>POR</sub>  | Power-On Reset Threshold Voltage                                                     |     | 1.5 | V     |

| t <sub>POFF</sub> | Minimum time at $V_{CC}$ = 0V between power cycles.                                  | 1   |     | ms    |

Note: 1. These parameters are characterized but they are not 100% tested in production.

If an event occurs in the system where the  $V_{CC}$  level supplied to the AT24C32E drops below the maximum  $V_{POR}$  level specified, it is recommended that a full power cycle sequence be performed by first driving the  $V_{CC}$  pin to GND, waiting at least the minimum  $t_{POFF}$  time, and then performing a new power-up sequence in compliance with the requirements defined in this section.

### 8.7 EEPROM Cell Performance Characteristics

#### Table 8-6. EEPROM Cell Performance Characteristics

| Operation                      | Test Condition                                                                     | Min       | Мах | Units        |

|--------------------------------|------------------------------------------------------------------------------------|-----------|-----|--------------|

| Write Endurance <sup>(1)</sup> | $T_A = 25^{\circ}C, V_{CC}(min) < V_{CC} < V_{CC}(max)$<br>Byte or Page Write Mode | 1,000,000 | _   | Write Cycles |

| Data Retention <sup>(2)</sup>  | $T_A = 55^{\circ}C, V_{CC}(min) < V_{CC} < V_{CC}(max)$                            | 100       | _   | Years        |

Notes: 1. Write endurance performance is determined through characterization and the qualification process.

2. The data retention capability is determined through qualification and is checked on each device in production.

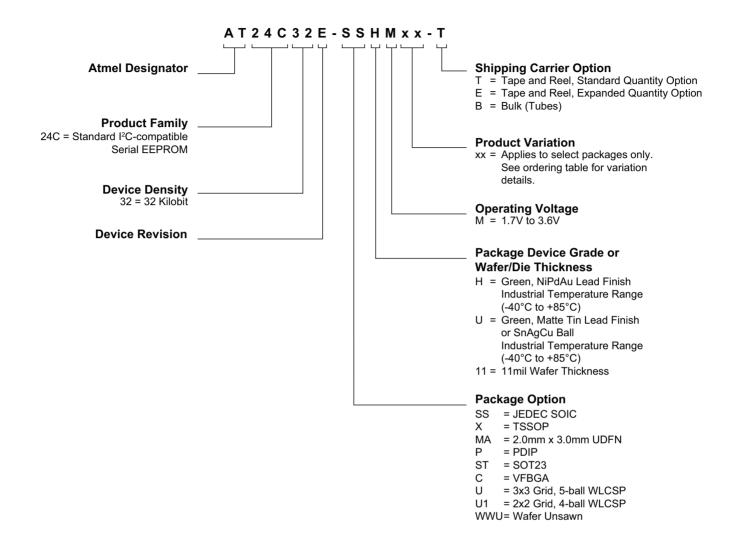

### 9. Ordering Code Detail

# 10. Ordering Information

|                                  |                                    |               | Delivery I    | Operation       |                                |

|----------------------------------|------------------------------------|---------------|---------------|-----------------|--------------------------------|

| Atmel Ordering Code              | Lead Finish                        | Package       | Form          | Quantity        | Range                          |

| AT24C32E-SSHM-T                  | -                                  | 8S1           | Tape and Reel | 4,000 per Reel  |                                |

| AT24C32E-SSHM-B                  |                                    |               | Bulk (Tubes)  | 100 per Tube    | -                              |

| AT24C32E-XHM-T                   | -                                  | 8X            | Tape and Reel | 5,000 per Reel  |                                |

| AT24C32E-XHM-B                   | NiPdAu<br>(Lead-free/Halogen-free) |               | Bulk (Tubes)  | 100 per Tube    | -                              |

| AT24C32E-MAHM-T                  |                                    | 8MA2          |               | 5,000 per Reel  |                                |

| AT24C32E-MAHM-E                  |                                    |               | Tape and Reel | 15,000 per Reel | -                              |

| AT24C32E-MAHMML-T                |                                    |               |               | 5,000 per Reel  | Industrial                     |

| AT24C32E-PUM                     | Matte Tin                          | 8P3           | Bulk (Tubes)  | 50 per Tube     | Temperature<br>(-40°C to 85°C) |

| AT24C32E-STUM-T                  | (Lead-free/Halogen-free)           | 5TS1          | Tape and Reel | 5,000 per Reel  | ( 40 0 10 00 0)                |

| AT24C32E-CUM-T                   |                                    | 8U3-1         | Tape and Reel | 5,000 per Reel  |                                |

| AT24C32E-UUM0B-T <sup>(1)</sup>  | SnAgCu Ball                        | 5U-2          |               |                 |                                |

| AT24C32E-U1UM0B-T <sup>(1)</sup> | (Lead-free/Halogen-free)           | 4U-11         |               |                 |                                |

| AT24C32E-U1UMML-T <sup>(1)</sup> |                                    |               |               |                 |                                |

| AT24C32E-WWU11M <sup>(2)</sup>   | N/A                                | Wafer<br>Sale | Note 2        |                 |                                |

Notes: 1. WLCSP Package:

- This device includes a backside coating to increase product robustness.

- CAUTION: Exposure to ultraviolet (UV) light can degrade the data stored in the EEPROM cells. Therefore, customers who use a WLCSP product must ensure that exposure to ultraviolet light does *not* occur.

- 2. For wafer sales, please contact Atmel Sales.

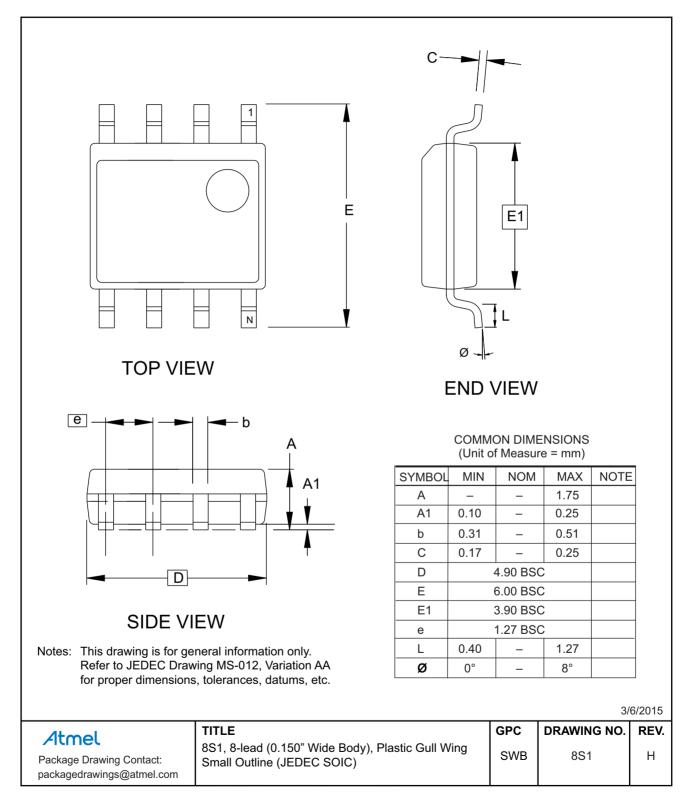

|       | Package Type                                                                          |

|-------|---------------------------------------------------------------------------------------|

| 8S1   | 8-lead, 0.150" wide, Plastic Gull Wing Small Outline (JEDEC SOIC)                     |

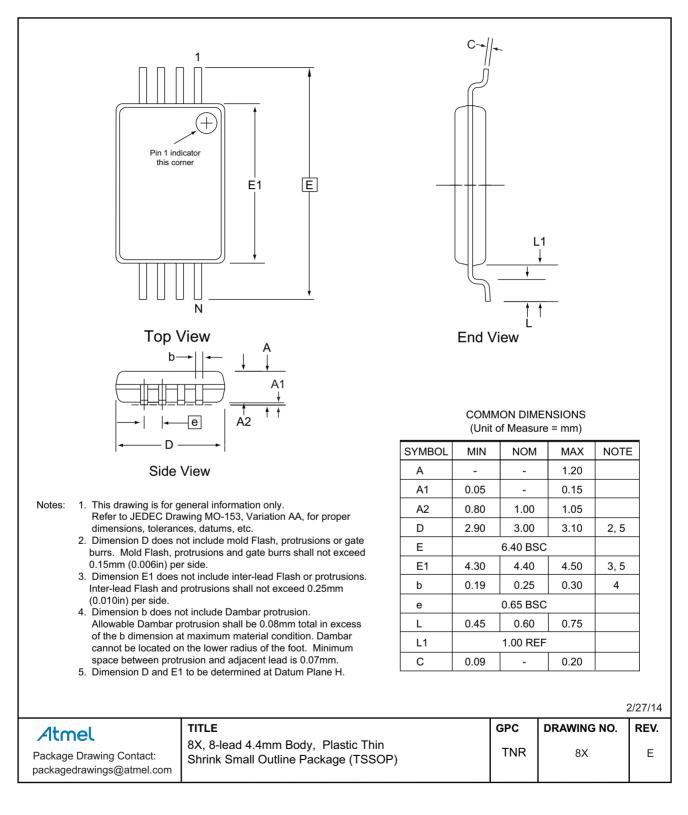

| 8X    | 8-lead, 4.4mm body, Plastic Thin Shrink Small Outline Package (TSSOP)                 |

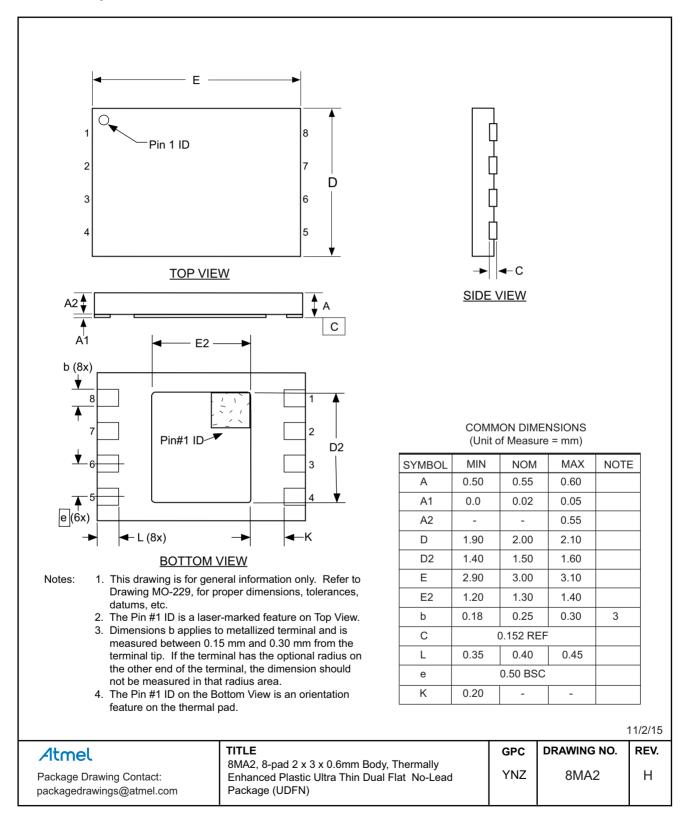

| 8MA2  | 8-pad, 2.0mm x 3.0mm x 0.6mm body, 0.5mm Pitch, Ultra Thin Dual Flat No Lead (UDFN)   |

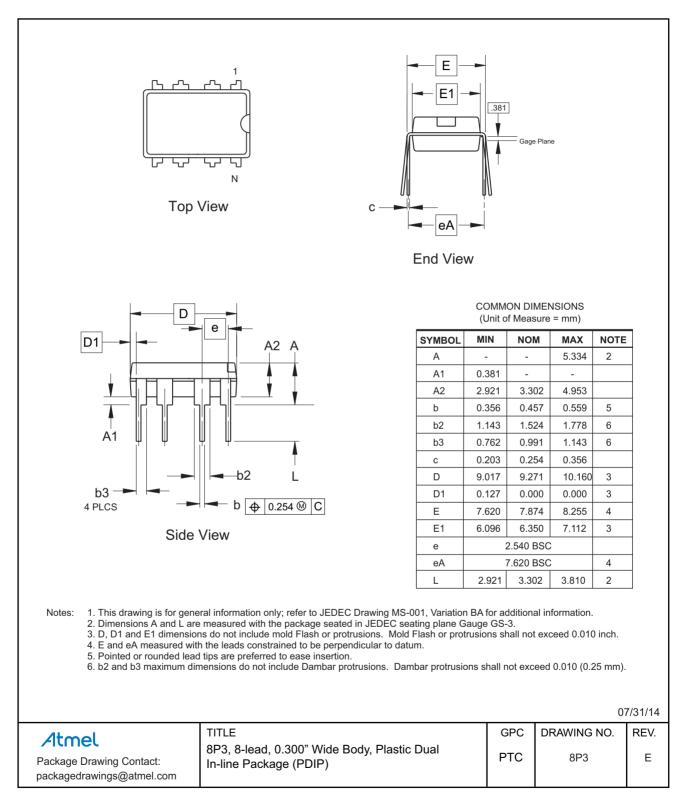

| 8P3   | 8-lead, 0.300" wide, Plastic Dual Inline Package (PDIP)                               |

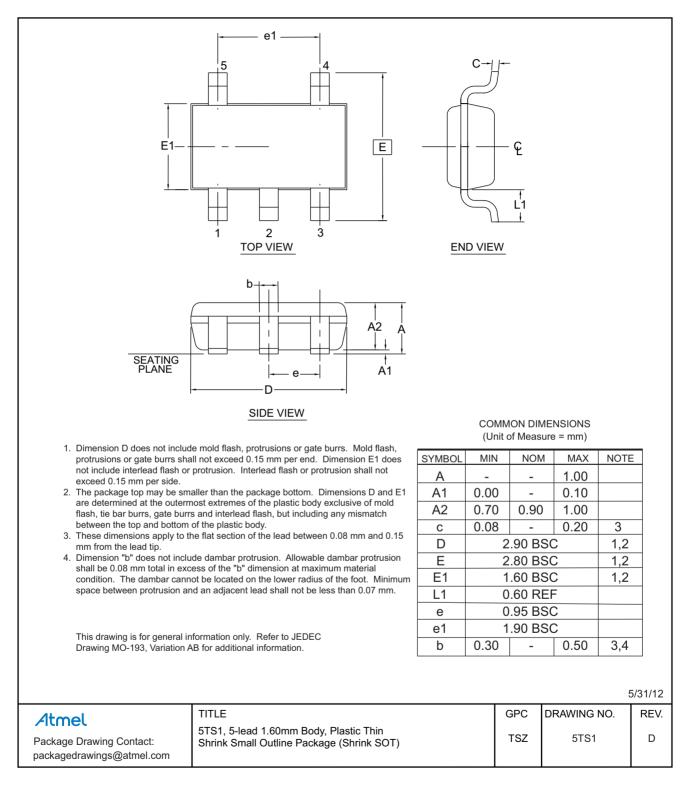

| 5TS1  | 5-lead, 1.6mm body, Plastic Thin Shrink Small Outline (SOT23)                         |

| 8U3-1 | 8-ball, 1.5mm x 2.0mm body, 0.5mm pitch, Very thin Fine Ball Grid Array (VFBGA)       |

| 5U-2  | 5-ball, 3 x 3 Grid Array, 0.4mm minimum pitch, Wafer Level Chip Scale Package (WLCSP) |

| 4U-11 | 4-ball, 2 x 2 Grid Array, 0.4mm minimum pitch, Wafer Level Chip Scale Package (WLCSP) |

# 11. Part Markings

| 8-lead SOIC                                                                                                                                                                                                                                                                                                                                  | 8-lead SOIC 8-lead TSSO                                                                         |                                                                                                                         | 8-pad UDFN                                               | ١            | 8-lead                                                                                              | I PDIP                                                                                                                |     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|--------------|-----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|-----|

| ATMLHYWW<br>###%<br>AAAAAAAA<br>•                                                                                                                                                                                                                                                                                                            |                                                                                                 | ATHYWW<br>###% @<br>AAAAAAA                                                                                             | 2.0 x 3.0 mm Body<br>###<br>H%@<br>YXX<br>●              |              |                                                                                                     | ATMLUYWW<br>###%<br>AAAAAAA<br>G G G G                                                                                |     |

| 5-lea                                                                                                                                                                                                                                                                                                                                        | ad SOT-23                                                                                       | 4-ball / 5-ba                                                                                                           | all WLCSP                                                | 8-ball V     | /FBGA                                                                                               |                                                                                                                       |     |

| Note 1: @                                                                                                                                                                                                                                                                                                                                    | HHH<br>AAA<br>YMXX Bottom                                                                       | •                                                                                                                       | XX                                                       |              | ###U<br>YMXX<br>PIN 1                                                                               |                                                                                                                       |     |

|                                                                                                                                                                                                                                                                                                                                              | designates pin 1<br>:kage drawings are not to si                                                | cale                                                                                                                    |                                                          |              |                                                                                                     |                                                                                                                       |     |

|                                                                                                                                                                                                                                                                                                                                              | kage drawings are not to so                                                                     |                                                                                                                         | n Code ###: 32                                           |              |                                                                                                     |                                                                                                                       |     |

| Note 2: Par<br>Catalog Number Trunc                                                                                                                                                                                                                                                                                                          | kage drawings are not to so                                                                     |                                                                                                                         | n Code ###: 32                                           | E            | Voltages                                                                                            |                                                                                                                       |     |

| Note 2: Par<br>Catalog Number Truno<br>AT24C32E                                                                                                                                                                                                                                                                                              | kage drawings are not to so                                                                     | Truncatio                                                                                                               | n Code ###: 32<br>ork Week of Ass                        |              | Voltages<br>% = M                                                                                   | inimum Voltage                                                                                                        |     |

| Catalog Number Trunc           AT24C32E           Date Codes           Y = Year           5: 2015         9: 2019           6: 2016         0: 2020           7: 2017         1: 2021                                                                                                                                                        | ation<br>M = Month<br>A: Januar<br>B: Februa                                                    | Truncatio<br>WW = W<br>y 02: Weel<br>ry 04: Weel<br>                                                                    | ork Week of Ass<br>< 2<br>< 4                            |              |                                                                                                     |                                                                                                                       |     |

| Y = Year           5: 2015         9: 2019           6: 2016         0: 2020           7: 2017         1: 2021           8: 2018         2: 2022                                                                                                                                                                                             | ation<br>M = Month<br>A: Januar                                                                 | Truncatio           WW = W           y         02: Weel           ry         04: Weel              ber         52: Weel | ork Week of Ass<br>< 2<br>< 4                            |              | % = M<br>M: 1.                                                                                      | 7V min                                                                                                                |     |

| Catalog Number Trunc           AT24C32E           Date Codes           Y = Year           5: 2015         9: 2019           6: 2016         0: 2020           7: 2017         1: 2021                                                                                                                                                        | M = Month<br>A: Januar<br>B: Februa<br><br>L: Decem                                             | Truncatio<br>WW = W<br>y 02: Weel<br>ry 04: Weel<br>                                                                    | ork Week of Ass<br>< 2<br>< 4<br>< 52                    | sembly       | % = M<br>M: 1.<br>Grade/Lead<br>U: In                                                               |                                                                                                                       |     |

| Catalog Number Trunc           AT24C32E           Date Codes           Y = Year           5: 2015         9: 2019           6: 2016         0: 2020           7: 2017         1: 2021           8: 2018         2: 2022           Country of Assembly                                                                                        | M = Month<br>A: Januar<br>B: Februa<br><br>L: Decem                                             | Truncatio<br>WW = W<br>y 02: Weel<br>ry 04: Weel<br><br>ber 52: Weel<br>Lot Number                                      | ork Week of Ass<br>< 2<br>< 4<br>< 52                    | sembly       | % = M<br>M: 1.<br>Grade/Lead<br>U: In                                                               | 7V min<br><b>d Finish Material</b><br>dustrial/Matte Tin/Sn<br>dustrial/NiPdAu                                        | Ag( |

| Catalog Number Trunc           AT24C32E           Date Codes           Y = Year           5: 2015         9: 2019           6: 2016         0: 2020           7: 2017         1: 2021           8: 2018         2: 2022           Country of Assembly           @ = Country of Assembly                                                      | M = Month<br>A: Januar<br>B: Februa<br>L: Decem                                                 | Truncatio WW = W y y 02: Weel 04: Weel ber 52: Weel Lot Number AAAA = Atmel W                                           | ork Week of Ass<br>< 2<br>< 4<br>< 52                    | sembly       | % = M<br>M: 1.<br>Grade/Lead<br>U: In<br>H: In                                                      | 7V min<br><b>d Finish Material</b><br>dustrial/Matte Tin/Sn<br>dustrial/NiPdAu<br>cation<br>mel<br>mel                | Age |

| Catalog Number Trunc           AT24C32E           Date Codes           Y = Year           5: 2015         9: 2019           6: 2016         0: 2020           7: 2017         1: 2021           8: 2018         2: 2022           Country of Assembly           @ = Country of Assembly           Trace Code           XX = Trace Code (Atme | M = Month<br>A: Januar<br>B: Februa<br>L: Decem                                                 | Truncatio WW = W y y 02: Weel 04: Weel ber 52: Weel Lot Number AAAA = Atmel W                                           | ork Week of Ass<br>< 2<br>< 4<br>< 52                    | sembly       | % = M<br>M: 1.<br>Grade/Lead<br>U: In<br>H: In<br>H: In<br>Atmel Trun<br>AT: At                     | 7V min<br><b>d Finish Material</b><br>dustrial/Matte Tin/Sn<br>dustrial/NiPdAu<br>cation<br>mel<br>mel                |     |

| Catalog Number Trunc           AT24C32E           Date Codes           Y = Year           5: 2015         9: 2019           6: 2016         0: 2020           7: 2017         1: 2021           8: 2018         2: 2022           Country of Assembly           @ = Country of Assembly           XX = Trace Code (Atme<br>Example: AA, AB   | M = Month<br>A: Januar<br>B: Februa<br>L: Decem                                                 | Truncatio WW = W y 02: Weel 04: Weel ber 52: Weel Lot Number AAAA = Atmel W Correspond to Code)                         | ork Week of Ass<br>< 2<br>< 4<br>< 52                    | sembly       | % = M<br>M: 1.<br>Grade/Lead<br>U: In<br>H: In<br>H: In<br>Atmel Trun<br>AT: At                     | 7V min<br><b>d Finish Material</b><br>dustrial/Matte Tin/Sn<br>dustrial/NiPdAu<br>cation<br>mel<br>mel                | 6,  |

| Catalog Number Trunc           AT24C32E           Date Codes           Y = Year           5: 2015         9: 2019           6: 2016         0: 2020           7: 2017         1: 2021           8: 2018         2: 2022           Country of Assembly           @ = Country of Assembly           Trace Code           XX = Trace Code (Atme | Ation<br>M = Month<br>A: Januar<br>B: Februa<br><br>L: Decem<br>Iy<br>I Lot Numbers 0<br>YZ, ZZ | Truncatio WW = W y 02: Weel 04: Weel ber 52: Weel Lot Number AAAA = Atmel W Correspond to Code)                         | ork Week of Ass<br>< 2<br>< 4<br>< 52<br>/afer Lot Numbe | sembly<br>er | % = M<br>M: 1.<br>Grade/Lead<br>U: In<br>H: In<br>H: In<br>AT: At<br>ATME At<br>ATM: At<br>ATML: At | 7V min<br><b>d Finish Material</b><br>dustrial/Matte Tin/Sn<br>dustrial/NiPdAu<br><b>ication</b><br>mel<br>mel<br>mel | AgC |

# 12. Packaging Information

### 12.1 8S1 — 8-lead JEDEC SOIC

### 12.2 8X — 8-lead TSSOP

### 12.3 8MA2 — 8-pad UDFN

Atmel

### 12.5 5TS1 — 5-lead SOT23

# **Atmel**

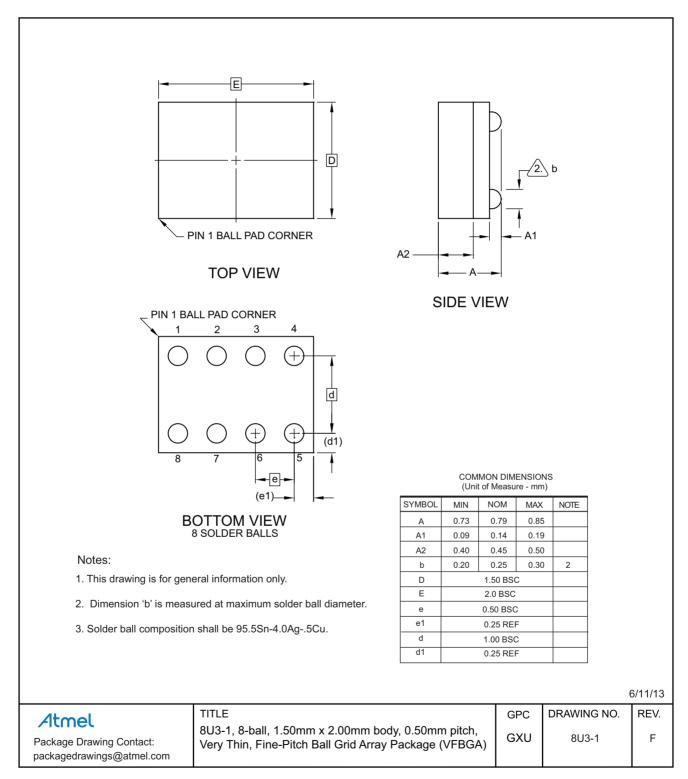

### 12.6 8U3-1 — 8-ball VFBGA

Atmel

### 12.8 4U-11 - 4-ball WLCSP

Atmel

# 13. Revision History

| Doc. No. | Date    | Comments                                                                                                                                                                                                                                                                                                |

|----------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8905F    | 05/2016 | Corrected the device share from two to eight on a common 2-wire bus.                                                                                                                                                                                                                                    |

| 8905E    | 11/2015 | Added the AT24C32E-MAHMML-T and AT24C32E-U1UMML-T package options.<br>Updated the 8MA2 package drawing.                                                                                                                                                                                                 |

| 8905D    | 06/2015 | Updated the part marking page.                                                                                                                                                                                                                                                                          |

| 8905C    | 05/2015 | Added the 4-ball WLCSP, AT24C32E-U1UM0B-T option and updated the package drawings.                                                                                                                                                                                                                      |

| 8905B    | 01/2015 | Added the 100kHz timing set for reference, the UDFN extended quantity option, and the figure for "System Configuration Using 2-Wire Serial EEPROMs".<br>Updated Software Reset section, and the 8X, 8MA2, and 8P3 package outline drawings.<br>Replaced the 5U-4 with the 5U-2 package outline drawing. |

| 8905A    | 05/2014 | Initial document release.                                                                                                                                                                                                                                                                               |

# Atmel Enabling Unlimited Possibilities®

Т

Atmel Corporation 1600 Technolo

1600 Technology Drive, San Jose, CA 95110 USA T: (+1)(4

T: (+1)(408) 441.0311

F: (+1)(408) 436.4200

www.atmel.com

© 2016 Atmel Corporation. / Rev.: Atmel-8905F-SEEPROM-AT24C32E-Datasheet\_052016.

Atmel<sup>®</sup>, Atmel logo and combinations thereof, Enabling Unlimited Possibilities<sup>®</sup>, and others are registered trademarks or trademarks of Atmel Corporation in U.S. and other countries. Other terms and product names may be trademarks of others.

DISCLAIMER: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN THE ATMEL TERMS AND CONDITIONS OF SALES LOCATED ON THE ATMEL WEBSITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDENTAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS AND PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and products descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.

SAFETY-CRITICAL, MILITARY, AND AUTOMOTIVE APPLICATIONS DISCLAIMER: Atmel products are not designed for and will not be used in connection with any applications where the failure of such products would reasonably be expected to result in significant personal injury or death ("Safety-Critical Applications") without an Atmel officer's specific written consent. Safety-Critical Applications include, without limitation, life support devices and systems, equipment or systems for the operation of nuclear facilities and weapons systems. Atmel products are not designed nor intended for use in military or aerospace applications or environments unless specifically designated by Atmel as military-grade. Atmel products are not designed nor intended for use in automotive applications unless specifically designated by Atmel as automotive-grade.

# **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Atmel:

AT24C32E-XHM-B AT24C32E-SSHM-T AT24C32E-XHM-T