August 2014

# FPF3042 IntelliMAX™ 18 V-Rated, Dual-Input, Single-Output, Power-Source-Selector Switch

#### **Features**

- Dual-Input, Single-Output Load Switch (DISO)

- Input Supply Operating Range:

- 4.0 V~12.4 V at V<sub>IN</sub>

- 4.0 V~12.4 V at V<sub>BUS</sub>

- Typical R<sub>on</sub>:

- 95 m $\Omega$  at V<sub>IN</sub>=5 V

- 70 m $\Omega$  at V<sub>BUS</sub>=5 V

- Bidirectional Switch for V<sub>IN</sub> and V<sub>BUS</sub>

- Slew Rate Controlled:

- 50  $\mu$ s at  $V_{IN}$  for  $< 4.7 \mu$ F  $C_{OUT}$

- 90 μs at V<sub>BUS</sub> for < 4.7 μF C<sub>OUT</sub>

- Maximum I<sub>SW</sub>: 2.7 A per Channel

- Break-Before-Make Transition

- Under-Voltage Lockout (UVLO)

- Over-Voltage Lockout (OVLO)

- Thermal Shutdown

- Logic CMOS IO Meets JESD76 Standard for GPIO Interface and Related Power Supply Requirements

- ESD Protected:

- Human Body Model: >3 kV

Charged Device Model: >1.5 kV

IEC 61000-4-2 Air Discharge: >15 kV

- IEC61000-4-2 Contact Discharge: >8 kV

# Description

The FPF3042 is an 18 V-rated Dual-Input Single-Output (DISO) load switch consisting of two channels of slew-rate-controlled, low-on-resistance, N-channel MOSFET switches with protection features. The slew-rate-controlled turn-on characteristic prevents inrush current and the resulting excessive voltage droop on the input power rails. The input voltage range operates from 4.0 V to 12.4 V at both  $V_{\text{BUS}}$  and  $V_{\text{IN}}$  to align with the needs of high-voltage portable device power rails.

Both  $V_{\text{IN}}$  and  $V_{\text{BUS}}$  have the over-voltage protection of 14 V (typical) to avoid damage to the system.

$V_{\text{IN}}$  and  $V_{\text{BUS}}$  bidirectional switching allows reverse current from  $V_{\text{OUT}}$  to  $V_{\text{IN}}$  or  $V_{\text{BUS}}$  for On-The-Go, (OTG) Mode. The switching is controlled by logic input EN and  $V_{\text{IN\_SEL}}$  is capable of interfacing directly with low-voltage control signal General-Purpose Input / Output (GPIO).

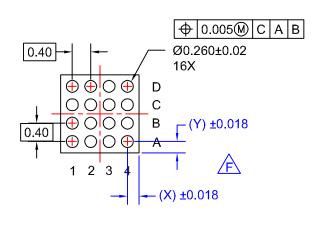

FPF3042 is available in 1.76 mm x 1.96 mm Wafer-Level Chip-Scale Package (WLCSP), 16-bump, 0.4 mm pitch.

#### **Applications**

- Input Power-Selection Block Supporting USB and Wireless Charging

- Smart Phone / Tablet PC

# **Ordering Information**

| Part Number | Top<br>Mark      | Channel | Typical R <sub>ON</sub> per<br>Channel at 5 V <sub>IN</sub> | Rise Time (t <sub>R</sub> ) | Package                                                   |

|-------------|------------------|---------|-------------------------------------------------------------|-----------------------------|-----------------------------------------------------------|

|             |                  |         | 95 m $\Omega$ for $V_{\text{IN}}$                           | 50 $\mu s$ for $V_{IN}$     | 16-Bump, 1.76 mm x 1.96 mm,                               |

| FPF3042UCX  | F3042UCX TR DISO |         | 70 m $\Omega$ for $V_{\text{BUS}}$                          | 90 μs for V <sub>BUS</sub>  | Wafer-Level Chip-Scale Package<br>  (WLCSP), 0.4 mm Pitch |

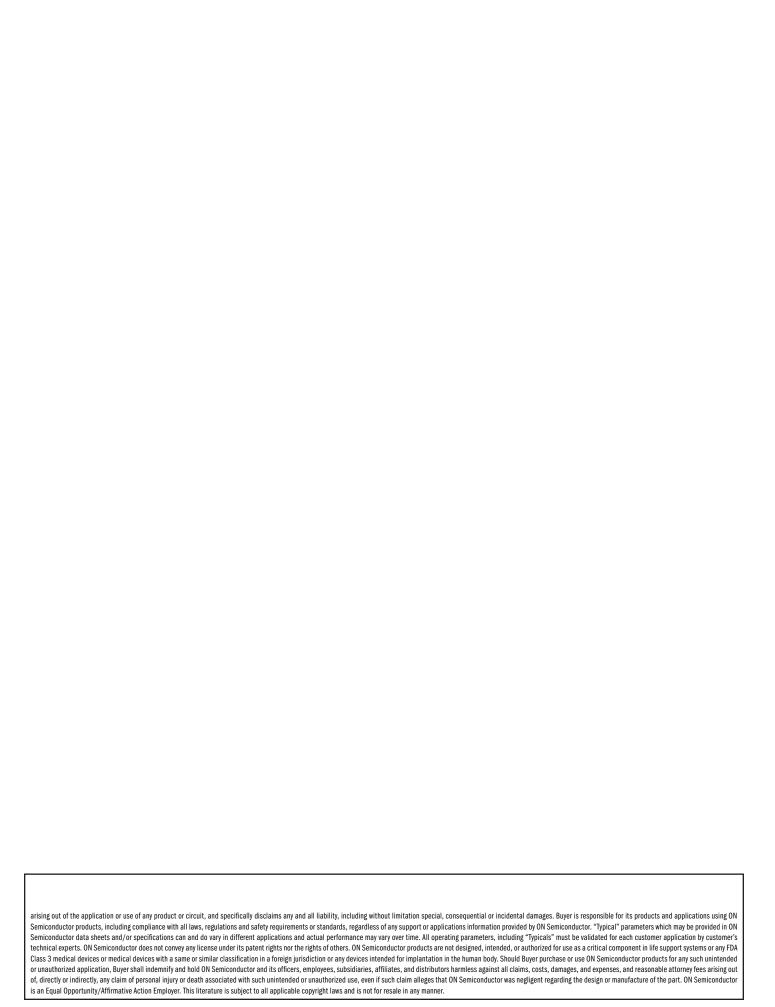

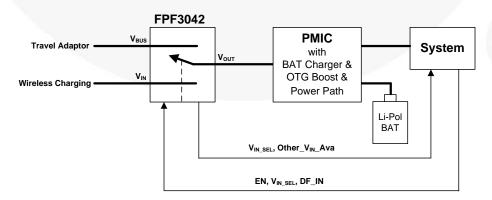

## **Application Diagram**

Figure 1. Typical Application

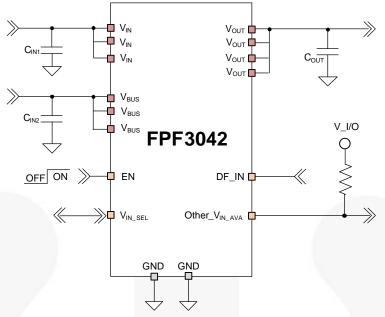

Figure 2. Example Circuit for OTG Operation with Low-Voltage GPIO

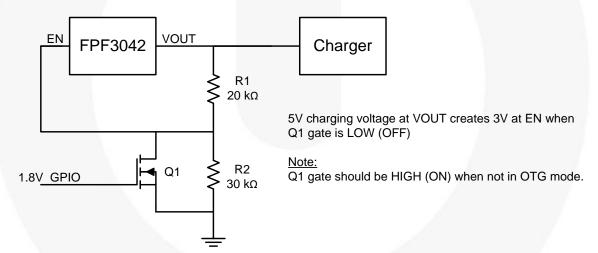

# **Block Diagram**

Figure 3. Functional Block Diagram

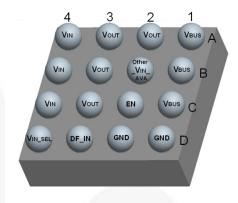

# **Pin Configuration**

Figure 4. Pin Assignment (Top View)

Figure 5. Pin Assignment (Bottom View)

# **Pin Description**

| Pin #          | Name                      | Input / Output | Description                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|----------------|---------------------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| A1, B1, C1     | V <sub>BUS</sub>          | Input / Output | V <sub>BUS</sub> at USB: Power input / output; bi-directional switch when V <sub>IN_SEL</sub> = LOW.                                                                                                                                                                                                                                                                                                  |  |  |

| A4, B4, C4     | V <sub>IN</sub>           | Input / Output | V <sub>IN</sub> Supply Input: Power input / output; bi-directional switch when V <sub>IN_SEL</sub> = HIGH.                                                                                                                                                                                                                                                                                            |  |  |

| A2, A3, B3, C3 | V <sub>OUT</sub>          | Input / Output | Switch Output: Power input / output                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| C2             | EN                        | Input          | Enable: Active HIGH;<br>EN voltage ≥ 2.5 V can power internal circuit when V <sub>IN</sub> and V <sub>BUS</sub> are absent.<br>1 MΩ pull-down resistor is included.                                                                                                                                                                                                                                   |  |  |

| D4             | V <sub>IN_SEL</sub>       | Input / Output | Supply Selector & Status: Input power source selection input and status output. This signal is ignored during EN=LOW. Selector input during EN=HIGH: HIGH = switch V <sub>IN</sub> to V <sub>OUT</sub> / LOW = switch V <sub>BUS</sub> to V <sub>OUT</sub> . Status output during EN=LOW: HIGH = V <sub>IN</sub> is used for V <sub>OUT</sub> / LOW = V <sub>BUS</sub> is used for V <sub>OUT</sub> . |  |  |

| D3             | DF_IN                     | Input          | Default Supply Selector during EN=LOW: Floating = $V_{BUS}$ connects to $V_{OUT}$ . LOW = $V_{IN}$ connects to $V_{OUT}$ . This signal is ignored during EN=HIGH. 1 $\mu$ A pull-up current source is included.                                                                                                                                                                                       |  |  |

| B2             | Other_V <sub>IN_AVA</sub> | Output         | Other Supply Input Status: Open-drain output.<br>HIGH-Z = both $V_{IN}$ and $V_{BUS}$ are valid.<br>LOW = the other power source is not valid.                                                                                                                                                                                                                                                        |  |  |

| D1, D2         | GND                       |                | Ground                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

Table 1. **Truth Table**

| EN   | V <sub>IN</sub> >V <sub>UVLO</sub> | V <sub>BUS</sub> >V <sub>UVLO</sub> | $V_{\text{IN\_SEL}}$ | DF_IN    | Other_V <sub>IN_AVA</sub>                                                          | V <sub>OUT</sub> | Comment                                             |

|------|------------------------------------|-------------------------------------|----------------------|----------|------------------------------------------------------------------------------------|------------------|-----------------------------------------------------|

| HIGH | Х                                  | Х                                   | LOW                  | Х        | HI-Z if $V_{IN}$ & $V_{BUS} > V_{UVLO}$<br>LOW if $V_{IN}$ or $V_{BUS} < V_{UVLO}$ | $V_{BUS}$        | V <sub>OUT</sub> is selected by V <sub>IN SEL</sub> |

| HIGH | Х                                  | Х                                   | HIGH                 | Х        | HI-Z if $V_{IN}$ & $V_{BUS} > V_{UVLO}$<br>LOW if $V_{IN}$ or $V_{BUS} < V_{UVLO}$ | V <sub>IN</sub>  | Bidirectional channel                               |

| LOW  | YES                                | NO                                  | HIGH                 | Х        | LOW                                                                                | $V_{IN}$         | Automatic selection to                              |

| LOW  | NO                                 | YES                                 | LOW                  | Х        | LOW                                                                                | $V_{BUS}$        | valid input<br>V <sub>IN_SEL</sub> is output.       |

| LOW  | YES                                | YES                                 | LOW                  | Floating | HIGH-Z                                                                             | $V_{BUS}$        | V <sub>OUT</sub> is selected by                     |

| LOW  | YES                                | YES                                 | HIGH                 | LOW      | HIGH-Z                                                                             | V <sub>IN</sub>  | DF_IN<br>V <sub>IN_SEL</sub> is output.             |

| LOW  | NO                                 | NO                                  | Х                    | Х        | LOW                                                                                | Floating         | OFF                                                 |

#### Notes:

- Internal pull-down at EN.

1 µA pull-up current source at DF\_IN.

### **Absolute Maximum Ratings**

Stresses exceeding the Absolute Maximum Ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

| Symbol          |                                                 | Parameters                                                                |                                                              |      |                   |      |

|-----------------|-------------------------------------------------|---------------------------------------------------------------------------|--------------------------------------------------------------|------|-------------------|------|

|                 | V V to CND                                      | Continuous                                                                |                                                              |      | 10.0              |      |

| \/              | V <sub>IN,</sub> V <sub>BUS</sub> to GND        | Pulsed, 100 ms Maximum No                                                 | n-Repetitive                                                 | -2.0 | 18.0              | V    |

| $V_{PIN}$       | V <sub>OUT</sub> to GND <sup>(3)</sup>          |                                                                           |                                                              | -0.3 | 16.0              | V    |

|                 | EN, DF_IN, V <sub>IN_SEL</sub> , Ot             | her_V <sub>IN_AVA</sub> to GND                                            |                                                              | -0.3 | 6.0               |      |

|                 |                                                 |                                                                           | T <sub>A</sub> =25°C                                         |      | 2.70              |      |

|                 | Maximum Cantinuous                              | T <sub>A</sub> =65°C                                                      |                                                              |      |                   |      |

| I <sub>SW</sub> | Maximum Continuous                              | Switch Current per Channel                                                | T <sub>A</sub> =75°C                                         |      | 2.50              | Α    |

|                 |                                                 |                                                                           | T <sub>A</sub> =85°C                                         |      | 2.25              |      |

| t <sub>PD</sub> | Total Power Dissipation at T <sub>A</sub> =25°C |                                                                           |                                                              |      | 2.25              | W    |

| $T_J$           | Operating Junction Temperature                  |                                                                           |                                                              |      | +150              | °C   |

| $T_{STG}$       | Storage Junction Temperature                    |                                                                           |                                                              |      | +150              | °C   |

| ӨЈА             | Thermal Resistance, J                           | Thermal Resistance, Junction-to-Ambient (1in. Square Pad of 2 oz. Copper) |                                                              |      | 55 <sup>(4)</sup> | °C/W |

|                 | /                                               | Human Body Model, ANSI/ESDA/JEDEC JS-001-2012                             |                                                              | 3.0  |                   |      |

|                 | 7                                               | Charged Device Model, JESD22-C101                                         |                                                              |      |                   |      |

| ESD             | Electrostatic Discharge Capability              | JE 004000 4 0 0 4 1 (5)                                                   | Air Discharge<br>(V <sub>IN</sub> , V <sub>BUS</sub> to GND) | 15.0 |                   | kV   |

|                 |                                                 | IEC61000-4-2 System Level <sup>(5</sup>                                   | Contact Discharge (V <sub>IN,</sub> V <sub>BUS</sub> to GND) | 8.0  |                   |      |

#### Notes:

- If an external voltage of more than 13 V is applied to V<sub>OUT</sub>, the slew rate should be <1 V/ms from 13 V.</li>

- 4. Measured using 2S2P JEDEC standard PCB.

- 5. System-level ESD can be guaranteed by design.

# **Recommended Operating Conditions**

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance to the datasheet specifications. Fairchild does not recommend exceeding them or designing to Absolute Maximum Ratings.

| Symbol         | Parameters                    | Min. | Max. | Unit |

|----------------|-------------------------------|------|------|------|

| \/             | V <sub>IN</sub>               | 4.0  | 12.4 | V    |

| $V_{PIN}$      | V <sub>BUS</sub>              | 4.0  | 12.4 | V    |

| T <sub>A</sub> | Ambient Operating Temperature |      | +85  | °C   |

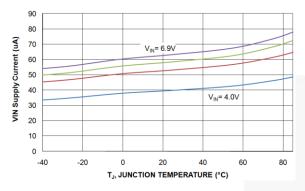

#### **Electrical Characteristics**

$V_{IN}$ =4 to 12.4 V,  $V_{BUS}$ =4 to 12.4 V,  $T_A$ =-40 to 85°C unless otherwise noted. Typical values are at  $V_{IN}$ = $V_{BUS}$ =5 V, EN=HIGH and  $T_A$ =25°C unless otherwise noted.

| Symbol               | Parameters                                                    | Condition                                                                                           | Min. | Тур. | Max. | Unit |  |

|----------------------|---------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|------|------|------|------|--|

| $V_{IN}$             | Input Voltage from V <sub>IN</sub>                            |                                                                                                     | 4.0  |      | 12.4 | V    |  |

| V <sub>BUS</sub>     | Input Voltage from V <sub>BUS</sub>                           |                                                                                                     | 4.0  |      | 12.4 | V    |  |

|                      | Outro and Outro                                               | I <sub>OUT</sub> =0 mA, EN=HIGH, V <sub>IN</sub> or V <sub>BUS</sub> =5 V                           |      | 55   | 120  | μA   |  |

| IQ                   | Quiescent Current                                             | I <sub>OUT</sub> =0 mA, EN=5 V, V <sub>IN</sub> and V <sub>BUS</sub> =GND                           |      | 33   | 70   | μA   |  |

|                      |                                                               | V <sub>IN</sub> =12 V, I <sub>OUT</sub> =200 mA, T <sub>A</sub> =25°C                               |      | 95   |      |      |  |

|                      |                                                               | V <sub>IN</sub> =8 V, I <sub>OUT</sub> =200 mA, T <sub>A</sub> =25°C                                |      | 95   |      | mΩ   |  |

|                      | On Resistance for V <sub>IN</sub>                             | V <sub>IN</sub> =5 V, I <sub>OUT</sub> =200 mA, T <sub>A</sub> =25°C                                |      | 95   | 150  |      |  |

| Б                    |                                                               | V <sub>IN</sub> =5 V, I <sub>OUT</sub> =200 mA,<br>T <sub>A</sub> =25°C to 85°C <sup>(6)</sup>      |      |      | 200  |      |  |

| $R_{ON}$             | /A                                                            | V <sub>BUS</sub> =12 V, I <sub>OUT</sub> =200 mA, T <sub>A</sub> =25°C                              |      | 70   |      |      |  |

|                      |                                                               | V <sub>BUS</sub> =6 V, I <sub>OUT</sub> =200 mA, T <sub>A</sub> =25°C                               |      | 70   |      |      |  |

|                      | On Resistance for V <sub>BUS</sub>                            | V <sub>BUS</sub> =5 V, I <sub>OUT</sub> =200 mA, T <sub>A</sub> =25°C                               |      | 70   | 100  | mΩ   |  |

|                      |                                                               | V <sub>BUS</sub> =5 V, I <sub>OUT</sub> =200 mA,<br>T <sub>A</sub> =25°C to 85°C <sup>(6)</sup>     |      |      | 140  |      |  |

| V <sub>IH</sub>      | Input Logic High Voltage                                      | V <sub>IN</sub> , V <sub>BUS</sub> = 4.0 V~12.4 V                                                   | 1.15 |      |      | V    |  |

| $V_{IL}$             | Input Logic Low Voltage                                       | V <sub>IN</sub> , V <sub>BUS</sub> =4.0 V~12.4 V                                                    |      |      | 0.52 | V    |  |

| V <sub>EN(OTG)</sub> | EN Voltage in OTG Mode <sup>(6)</sup>                         | V <sub>IN</sub> & V <sub>BUS</sub> =Float or V <sub>IN</sub> & V <sub>BUS</sub> <v<sub>UVLO</v<sub> | 2.5  |      |      | V    |  |

| R <sub>EN_PD</sub>   | Pull-Down Resistance at EN                                    |                                                                                                     |      | 1000 |      | kΩ   |  |

| Protectio            | n                                                             |                                                                                                     |      |      | •    |      |  |

|                      | Linder Voltage Leekeut Threehold                              | V <sub>IN</sub> or V <sub>BUS</sub> Rising                                                          | 3.05 | 3.50 | 4.00 | V    |  |

| $V_{UVLO}$           | Under-Voltage Lockout Threshold                               | V <sub>IN</sub> or V <sub>BUS</sub> Falling                                                         | 2.55 | 3.00 | 3.55 | V    |  |

| $V_{\text{UVHYS}}$   | Under-Voltage Lockout Hysteresis                              |                                                                                                     |      | 0.5  |      | V    |  |

|                      |                                                               | V <sub>IN</sub> Rising Threshold                                                                    | 12.9 | 14.0 | 15.0 | V    |  |

| \/                   | Over-Voltage Lockout Threshold                                | V <sub>IN</sub> Falling Threshold                                                                   | 12.4 | 13.5 | 14.5 | V    |  |

| $V_{OVLO}$           |                                                               | V <sub>BUS</sub> Rising Threshold                                                                   | 12.9 | 14.0 | 15.0 | V    |  |

| - N                  |                                                               | V <sub>BUS</sub> Falling Threshold                                                                  | 12.4 | 13.5 | 14.5 | V    |  |

| V                    | Over Veltage Leekeut Hystoresis                               | VIN                                                                                                 |      | 0.5  |      | V    |  |

| V <sub>OVHYS</sub>   | Over-Voltage Lockout Hysteresis                               | V <sub>BUS</sub>                                                                                    |      | 0.5  |      | V    |  |

| $T_{SDN}$            | Thermal Shutdown Threshold                                    |                                                                                                     |      | 150  |      | °C   |  |

| T <sub>SDNHYS</sub>  | Thermal Shutdown Hysteresis                                   |                                                                                                     |      | 20   |      | °C   |  |

|                      | Current Blocking (RCB)                                        |                                                                                                     |      |      |      |      |  |

| $I_{RCB}$            | V <sub>IN</sub> or V <sub>BUS</sub> Current During RCB        | V <sub>OUT</sub> =8 V, V <sub>IN</sub> or V <sub>BUS</sub> =GND                                     |      |      | 30   | μΑ   |  |

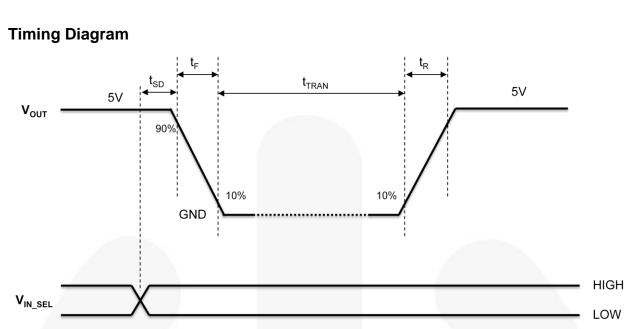

| Dynamic              | Characteristics                                               |                                                                                                     |      |      | V.I  |      |  |

| 4_                   | V <sub>OUT</sub> Rise Time, V <sub>BUS</sub> <sup>(6,7)</sup> |                                                                                                     |      | 90   |      | 0    |  |

| t <sub>R</sub>       | V <sub>OUT</sub> Rise Time, V <sub>IN</sub> <sup>(6,7)</sup>  | V V 5V B 45000 15 5                                                                                 |      | 50   |      | μs   |  |

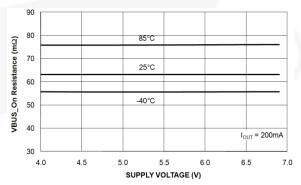

| t <sub>F</sub>       | V <sub>OUT</sub> Fall Time <sup>(6,7)</sup>                   | $V_{IN}=V_{BUS}=5$ V, $R_L=150$ $\Omega$ , $C_L=4.7$ $\mu F$ , $T_A=25$ °C                          |      | 1.4  |      | ms   |  |

| t <sub>TRAN</sub>    | Transition Delay <sup>(6,7)</sup>                             | 1 <sub>A</sub> =25°C                                                                                |      | 100  |      | ms   |  |

| t <sub>SD</sub>      | Selection Delay <sup>(6,7)</sup>                              |                                                                                                     |      | 50   |      | μs   |  |

#### Notes:

- 6. This parameter is guaranteed by characterization and/or design; not production tested.

- 7. t<sub>SD</sub>/t<sub>TRAN</sub>/t<sub>R</sub>/t<sub>F</sub> are defined in Figure 6.

Figure 6. Transition Delay ( $V_{IN}=V_{BUS}=5~V$ )

# **Typical Characteristics**

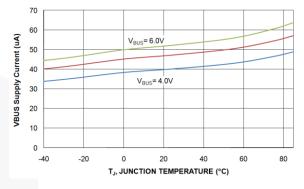

Figure 7. VIN Quiescent Current (Iq) vs. Temperature Figure 8. VBUS Quiescent Current (Iq) vs. Temperature

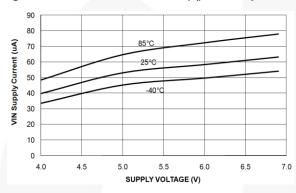

Figure 9. VIN Quiescent Current vs. Supply Voltage

Figure 10. $V_{\text{BUS}}$  Quiescent Current vs. Supply Voltage

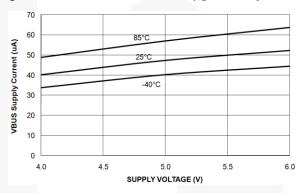

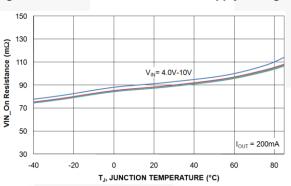

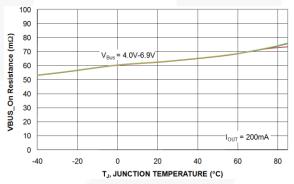

Figure 11. V<sub>IN</sub> On Resistance (mΩ) vs. Temperature

Figure 12.V  $_{\text{BUS}}$  On Resistance (m $\Omega$ ) vs. Temperature

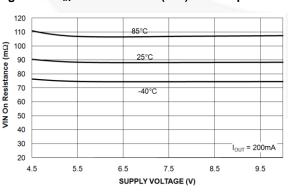

Figure 13.V<sub>IN</sub> On Resistance (mΩ) vs. Supply Voltage Figure 14.V<sub>BUS</sub> On Resistance (mΩ) vs. Supply Voltage

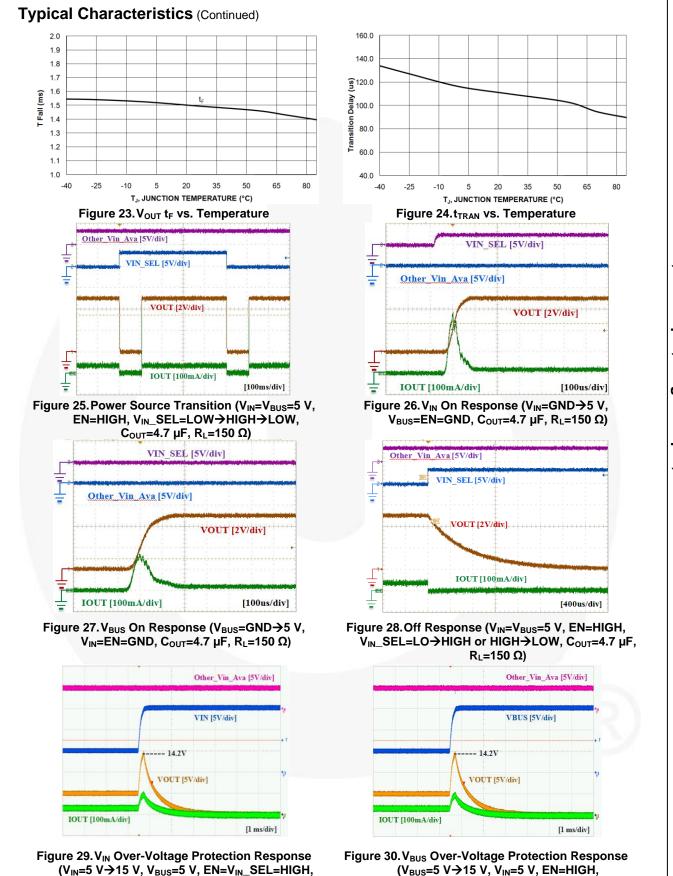

#### Typical Characteristics (Continued) 1.00 Voltage (V) VSEL VIH Voltage (V) 0.95 0.95 0.90 0.90 0.90 0.85 0.80 0.75 0.70 0.85 EN Input Logic High 0.80 VSEL\_VIL 0.75 0.70 0.65 20 35 50 20 50 35 T<sub>J</sub>, JUNCTION TEMPERATURE (°C) T<sub>J</sub>, JUNCTION TEMPERATURE (°C) Figure 15.V<sub>IN</sub>\_SEL Input Logic HIGH & Low Voltage Figure 16.EN Input Logic HIGH & Low Voltage vs. Temperature vs. Temperature <u>ء</u> 1.00 DFIN VIH 5 Voltage 0.95 4.5 (A) 3.5 3 2.5 2 1.5 1.5 Vin\_UVLO\_Rising 0.90 0.85 DEIN Input Logic High L 0.80 0.75 0.70 0.65 0.60 0.60 Vin\_UVLO\_Falling DFIN VIL Ę 0.5 0.60 0 -40 -25 -10 5 20 35 50 80 -40 -25 -10 20 35 50 65 80 T<sub>J</sub>, JUNCTION TEMPERATURE (°C) Tj, Junction Temperature(°C) Figure 17.DF\_IN Logic HIGH & Low Voltage Figure 18. V<sub>IN\_VULVO</sub> vs. Temperature vs. Temperature 18 5 4.5 16 Vin\_OV\_Rising Vbus UVLO Threshold(V) 4 OV Threshold(V) 10 8 6 Vbus\_UVLO\_Rising Vin\_OV\_Falling 3 Vbus\_UVLO\_Falling 2 6 1.5 Ę 1 2 0.5 0 20 -40 -25 -10 35 50 65 80 -40 20 35 50 -25 65 80 Tj, Junction Temperature(°C) Tj, Junction Temperature(°C) Figure 19. V<sub>BUS\_VULVO</sub> vs. Temperature Figure 20.V<sub>IN\_VOVLO</sub> vs. Temperature 18 140.0 16 Vin\_OV\_Rising 14 OV Threshold(V) 120.0 Vin\_OV\_Falling 12 S 100.0 10 8 80.0 6 Ē 4 60.0 2 0 40.0 20 -40 -25 35 50 65 80 -40 80 Tj, Junction Temperature(°C) T<sub>J</sub>, JUNCTION TEMPERATURE (°C) Figure 21. V<sub>BUS\_VOVLO</sub> vs. Temperature Figure 22. Vout t<sub>R</sub> vs. Temperature

$C_{OUT}=4.7 \mu F, R_{L}=150 \Omega$

$V_{IN}$  SEL=LOW,  $C_{OUT}$ =4.7  $\mu$ F,  $R_L$ =150  $\Omega$ )

#### **Operation and Application Information**

The FPF3042 is an 18 V, 2.7 A-rated, Dual-Input Single-Output (DISO) N-channel MOSFET load switch with slew-rate-controlled and low on resistance. The input operating range is from 4 V to 12.4 V at  $V_{\text{BUS}}$  and at  $V_{\text{IN}}$ . The internal circuitry is powered from the highest voltage source among  $V_{\text{IN}}, V_{\text{BUS}},$  and EN.

#### **Input Power-Source Selection**

The input power source can be selected by  $V_{IN\_SEL}$  and DF\_IN, respectively, depending on the EN state. When EN is HIGH, the input source is selected by  $V_{IN\_SEL}$  regardless of DF\_IN. If  $V_{IN\_SEL}$  is LOW,  $V_{BUS}$  is selected. If  $V_{IN\_SEL}$  is HIGH,  $V_{IN}$  is selected.

Table 2. Input Power Selection by VIN\_SEL

| EN   | V <sub>IN</sub> >V <sub>UVLO</sub> | V <sub>BUS</sub> >V <sub>UVLO</sub> | V <sub>IN_SEL</sub> | DF_IN | V <sub>OUT</sub> |

|------|------------------------------------|-------------------------------------|---------------------|-------|------------------|

| HIGH | Χ                                  | Χ                                   | LOW                 | Χ     | $V_{\text{BUS}}$ |

| HIGH | Χ                                  | X                                   | HIGH                | X     | $V_{IN}$         |

When EN is LOW, the input source is selected by DF\_IN and the number of valid input sources. If only one input source is valid (greater than  $V_{\text{UVLO}(\text{MAX})}$ ), the source is selected automatically, regardless of DF\_IN, to make charging path in case the battery is depleted. If both  $V_{\text{BUS}}$  and  $V_{\text{IN}}$  have valid input sources, the input source is selected by DF\_IN. If DF\_IN is LOW,  $V_{\text{IN}}$  is selected. If DF\_IN is HIGH or floating,  $V_{\text{BUS}}$  is selected. DF\_IN is biased HIGH with an internal 1  $\mu\text{A}$  pull-up current source.

Table 3. Input Power Selection by DF\_IN

| EN  | $V_{IN} > V_{UVLO}$ | V <sub>BUS</sub> >V <sub>UVLO</sub> | $V_{\text{IN\_SEL}}$ | DF_IN    | V <sub>out</sub> |

|-----|---------------------|-------------------------------------|----------------------|----------|------------------|

| LOW | YES                 | NO                                  | HIGH                 | X        | $V_{\text{IN}}$  |

| LOW | NO                  | YES                                 | LOW                  | Х        | $V_{BUS}$        |

| LOW | YES                 | YES                                 | LOW                  | Floating | $V_{\text{BUS}}$ |

| LOW | YES                 | YES                                 | HIGH                 | LOW      | $V_{IN}$         |

| LOW | NO                  | NO                                  | Χ                    | Χ        | Floating         |

$V_{IN\_SEL}$  can be the status output to indicate which input power source is used during EN is LOW. If  $V_{IN}$  is used,  $V_{IN\_SEL}$  shows HIGH. If  $V_{BUS}$  is used,  $V_{IN\_SEL}$  shows LOW. The voltage level of HIGH signal is 5.3 V if any one of  $V_{IN}$ ,  $V_{BUS}$ , or EN is higher than 5.3 V. The signal

is highest voltage among  $V_{IN}$ ,  $V_{BUS}$ , and EN if none of them is higher than 5.3 V.

#### **EN Voltage for Control Logic Power Supply**

Internal control logic is powered from the highest voltage among  $V_{IN}$ ,  $V_{BUS}$ , and  $V_{EN}$ . If valid  $V_{IN}$  or  $V_{BUS}$  higher than UVLO is applied, ON/OFF control by EN should be accomplished with  $V_{IH}/V_{IL}$ . If EN powers the internal control block without valid  $V_{IN}$  and  $V_{BUS}$ , more than 2.5 V is required on the EN pin to operate properly.

#### **Over-Voltage Protection (OVP)**

The FPF3042 includes over-voltage protection at both  $V_{IN}$  and  $V_{BUS}$ . If  $V_{IN}$  or  $V_{BUS}$  is higher than 14 V (typical), the power switch is off until input voltage is lower than the over-voltage trip level by a hysteresis voltage of 0.5 V.

#### **Reverse Power Supply for OTG**

The bidirectional switch allows reverse power for On-The-Go (OTG) operation. Even if both  $V_{\text{IN}}$  and  $V_{\text{BUS}}$  are unavailable, reverse power can be supported if internal control circuitry is powered by EN.

#### **Reverse-Current Blocking (RCB)**

FPF3042 supports reverse-current blocking during EN LOW and an unselected channel.

#### Thermal Shutdown

During thermal shutdown, the power switch is turned off if junction temperature exceeds 150°C to avoid damage.

#### Wireless Charging System

FPF3042 can be used as an input power selector supporting Travel Adaptor (TA) and Wireless Charging (WC) with a single-input-based battery charger or Power Management IC (PMIC), including a charging block as shown in Figure 31. The system can recognize an input power source change between 5 V TA and 5 V WC without detection circuitry because FPF3042 has a 100 ms transition delay. OTG Mode can be supported without an additional power path, such as a MOSFET.

Figure 31.Input Power Selector for Wireless Charging System

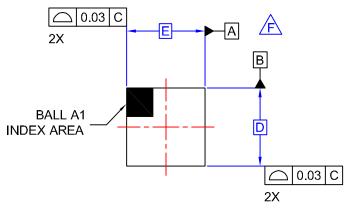

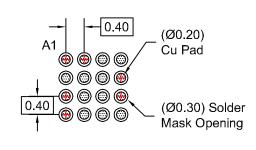

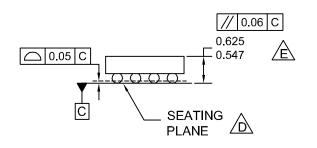

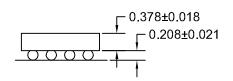

# **Product Specific Package Information**

| D                | E                | X       | Υ       |  |

|------------------|------------------|---------|---------|--|

| 1.96 mm ±0.03 mm | 1.76 mm ±0.03 mm | 0.28 mm | 0.38 mm |  |

**TOP VIEW**

RECOMMENDED LAND PATTERN (NSMD PAD TYPE)

#### NOTES:

SIDE VIEWS

- A. NO JEDEC REGISTRATION APPLIES.

- B. DIMENSIONS ARE IN MILLIMETERS.

- C. DIMENSIONS AND TOLERANCE PER ASME Y14.5M, 1994.

- DATUM C IS DEFINED BY THE SPHERICAL CROWNS OF THE BALLS.

- PACKAGE NOMINAL HEIGHT IS 586 MICRONS ±39 MICRONS (547-625 MICRONS).

- F. FOR DIMENSIONS D, E, X, AND Y SEE PRODUCT DATASHEET.

- G. DRAWING FILNAME: MKT-UC016AArev2.

**BOTTOM VIEW**

#### TRADEMARKS

The following includes registered and unregistered trademarks and service marks, owned by Fairchild Semiconductor and/or its global subsidiaries, and is not intended to be an exhaustive list of all such trademarks.

AccuPower™ F-PFS™ AttitudeEngine™ FRFET®

Global Power Resource<sup>SM</sup> Awinda<sup>®</sup>

AX-CAP®\* GreenBridge™ BitSiC™ Green FPS™ Build it Now™

Green FPS™ e-Series™ CorePLUS™ Gmax™ CorePOWER™  $\mathsf{GTO}^{\mathsf{TM}}$ CROSSVOLT™ IntelliMAX™

CTL™ ISOPLANAR™ Current Transfer Logic™ Making Small Speakers Sound Louder

**DEUXPEED®** and Better™ Dual Cool™ MegaBuck™ EcoSPARK® MIČROCOUPLER™ EfficientMax™ MicroFET™

**ESBC™** MicroPak™ MicroPak2™ MillerDrive™ Fairchild® MotionMax™

Fairchild Semiconductor® MotionGrid® FACT Quiet Series™ MTi<sup>®</sup> FACT<sup>®</sup> MTx® FastvCore™ MVN® FETBench™ mWSaver® FPS™ OptoHiT™ OPTOLOGIC® OPTOPLANAR®

Power Supply WebDesigner™ PowerTrench®

PowerXSTI

Programmable Active Droop™

OFFT QS™ Quiet Series™ RapidConfigure™

Saving our world, 1mW/W/kW at a time™

SignalWise™ SmartMax™ SMART START™

Solutions for Your Success™

SPM® STEALTH™ SuperFET® SuperSOT™-3 SuperSOT™-6 SuperSOT™-8 SupreMOS® SyncFET™ Sync-Lock™

SYSTEM SYSTEM TinyBoost<sup>®</sup> TinyBuck<sup>®</sup> TinyCalc™ TinyLogic<sup>®</sup> TINYOPTO™ TinvPower™ TinyPWM™ TinyWire™ TranSiC™ TriFault Detect™ TRUECURRENT®\* սSerDes™

UHC Ultra FRFET™ UniFET™ VCX™ VisualMax™

VoltagePlus™ XSTM. Xsens™ 仙童®

**-**®

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION, OR DESIGN. TO OBTAIN THE LATEST, MOST UP-TO-DATE DATASHEET AND PRODUCT INFORMATION, VISIT OUR <u>AIRCHILDSEMI.COM.</u> FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS. THESE SPECIFICATIONS DO NOT EXPAND THE TERMS OF FAIRCHILD'S WORLDWIDE TERMS AND CONDITIONS, SPECIFICALLY THE WARRANTY THEREIN, WHICH COVERS THESE PRODUCTS.

Unless otherwise specified in this data sheet, this product is a standard commercial product and is not intended for use in applications that require extraordinary levels of quality and reliability. This product may not be used in the following applications, unless specifically approved in writing by a Fairchild officer: (1) automotive or other transportation, (2) military/aerospace, (3) any safety critical application - including life critical medical equipment - where the failure of the Fairchild product reasonably would be expected to result in personal injury, death or property damage. Customer's use of this product is subject to agreement of this Authorized Use policy. In the event of an unauthorized use of Fairchild's product, Fairchild accepts no liability in the event of product failure. In other respects, this product shall be subject to Fairchild's Worldwide Terms and Conditions of Sale, unless a separate agreement has been signed by both Parties.

#### ANTI-COUNTERFEITING POLICY

Fairchild Semiconductor Corporation's Anti-Counterfeiting Policy. Fairchild's Anti-Counterfeiting Policy is also stated on our external website, www.fairchildsemi.com,

Counterfeiting of semiconductor parts is a growing problem in the industry. All manufacturers of semiconductor products are experiencing counterfeiting of their parts. Customers who inadvertently purchase counterfeit parts experience many problems such as loss of brand reputation, substandard performance, failed applications, and increased cost of production and manufacturing delays. Fairchild is taking strong measures to protect ourselves and our customers from the proliferation of counterfeit parts. Fairchild strongly encourages customers to purchase Fairchild parts either directly from Fairchild or from Authorized Fairchild Distributors who are listed by country on our web page cited above. Products customers buy either from Fairchild directly or from Authorized Fairchild Distributors are genuine parts, have full traceability, meet Fairchild's quality standards for handling and storage and provide access to Fairchild's full range of up-to-date technical and product information. Fairchild and our Authorized Distributors will stand behind all warranties and will appropriately address any warranty issues that may arise. Fairchild will not provide any warranty coverage or other assistance for parts bought from Unauthorized Sources. Fairchild is committed to combat this global problem and encourage our customers to do their part in stopping this practice by buying direct or from authorized distributors.

#### PRODUCT STATUS DEFINITIONS

#### **Definition of Terms**

| Deminition of Terms      |                       |                                                                                                                                                                                                     |

|--------------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Datasheet Identification | Product Status        | Definition                                                                                                                                                                                          |

| Advance Information      | Formative / In Design | Datasheet contains the design specifications for product development. Specifications may change in any manner without notice.                                                                       |

| Preliminary              | First Production      | Datasheet contains preliminary data; supplementary data will be published at a later date. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve design. |

| No Identification Needed | Full Production       | Datasheet contains final specifications. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve the design.                                               |

| Obsolete                 | Not In Production     | Datasheet contains specifications on a product that is discontinued by Fairchild Semiconductor. The datasheet is for reference information only.                                                    |

Rev 177

<sup>\*</sup> Trademarks of System General Corporation, used under license by Fairchild Semiconductor.