# **IR High Voltage IC**

AUIR08152S

# **BUFFER GATE DRIVER INTEGRATED CIRCUIT**

#### Features

- High peak output current

- Negative turn-off bias

- Separate Ron / Roff resistors

- Low supply current

- Under-voltage lockout

- Full time ON capability

- Low propagation delay time

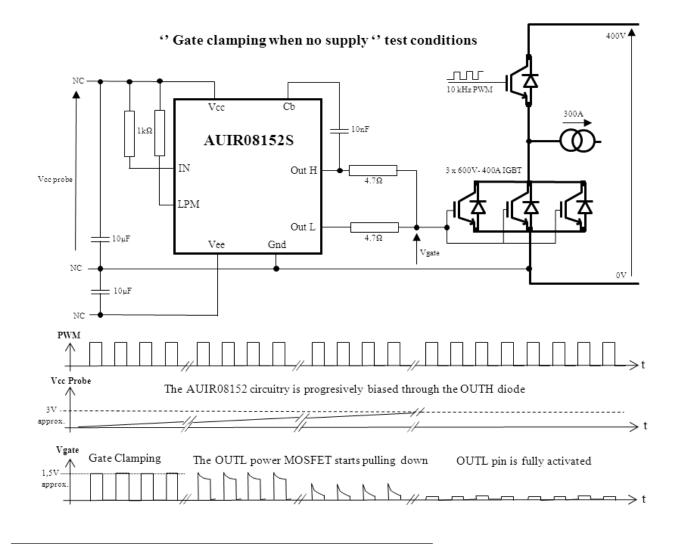

- Gate clamping when no supply

- Automotive qualified

#### Applications

- High power inverters

- EV/HEV power trains

#### **Product Summary**

| Outputs Current:    | +/- 10A    |

|---------------------|------------|

| Operating Voltage:  | 13V to 25V |

| Negative Gate Bias: | 0 to -10V  |

#### Package

#### Description

The AUIR08152 buffer brings high power gate drive capability to all pre-driver stages. It is the output extension of the wide I.R gate driver families. It features a negative Gate bias for applications requiring high levels of dv/dt immunity, a low power consumption mode as well as the full time ON gate drive ability. Shoot-through prevention is extended even when the AUIR08152S supplies are absent by mean of a Gate to Emitter self-clamping impedance.

#### **Ordering Information**

| Dece Dert Number |              | Standard Pack |          |                       |

|------------------|--------------|---------------|----------|-----------------------|

| Base Part Number | Package Type | Form          | Quantity | Orderable Part Number |

|                  | 50109        | Tube          | 95       | AUIR08152S            |

| AUIR08152S       | SOIC8        | Tape and reel | 2500     | AUIR08152STR          |

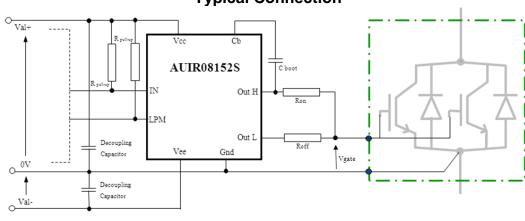

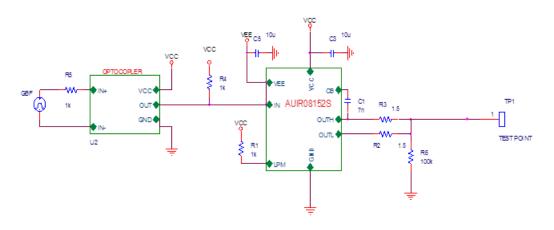

### **Typical Connection**

Absolute Maximum Ratings Absolute maximum ratings indicate sustained limits beyond which permanent damage to the device may occur. These are stress ratings only, functional operation of the device at these or any other condition beyond those indicated in the "Recommended Operating Condition" is not implied. Exposure to absolute maximum-rated conditions for extended periods may affect device reliability. All voltage parameters are absolute voltages referenced to GND unless otherwise stated in the table. The thermal resistance and power dissipation ratings are measured mounted on board in free air condition.

| Symbol   | Definition                                                                  | Min                   | Max                   | Units |

|----------|-----------------------------------------------------------------------------|-----------------------|-----------------------|-------|

| Vcc-Gnd  | Vcc to Gnd maximum voltage                                                  | -0.3                  | +37                   |       |

| Vcc-Vee  | Vcc to Vee maximum voltage                                                  | -0.3                  | +37                   |       |

| Vcc-VIN  | Vcc to Vin maximum voltage                                                  | -0.3                  | +37                   | V     |

| Vcc-Vlpm | Vcc to VLPM maximum voltage                                                 | -0.3                  | +37                   |       |

| VCB      | CB to OUTH max voltage                                                      | -0.3                  | +5.5                  |       |

| ILPM     | LPM pin maximum current                                                     | -10                   | +10                   |       |

| lin      | IN pin maximum current                                                      | -10                   | +10                   | mA    |

| VOUTH    | OUTH pin maximum voltage, DC operation                                      | Vcc - 37              | V <sub>CC</sub> + 0.3 | V     |

| VOUTL    | OUTL pin maximum voltage, DC operation                                      | V <sub>EE</sub> - 0.2 | V <sub>CC</sub> + 0.3 |       |

| IOUTH    | Maximum input transient current to OUTH pin (t < 1us,Ron = $2\Omega$ )      |                       | 2                     | ^     |

| IOUTL    | Maximum output transient current from OUTL pin (t < 1us, Roff = $2\Omega$ ) |                       | 1.5                   | A     |

| PD       | Package power dissipation @ $T_A \le 25 \text{ °C}$                         | _                     | 1                     | W     |

| RthJA    | Thermal resistance, junction to ambient                                     | _                     | 80                    | K/W   |

| TJ       | Junction temperature                                                        | -40                   | 150                   |       |

| TS       | Storage temperature                                                         | -55                   | 150                   | °C    |

| TL       | Lead temperature (soldering, 10 seconds)                                    | _                     | 300                   |       |

#### **Recommended Operating Conditions**

The recommended conditions represent the AUIR08152 optimum performances for the typical application

| Symbol    | Definition                                       | Min.     | Max.            | Units |  |

|-----------|--------------------------------------------------|----------|-----------------|-------|--|

| VCC-GND   | Gate driver positive supply voltage              | 15       | 25              |       |  |

| GND-VEE   | Recommended negative gate bias                   | 0        | -10             |       |  |

| VCC-VEE   | Total supply voltage                             | 15       | 35              | V     |  |

| VOUTH     | OUTH Output voltage                              | Vcc - 35 | Vcc             |       |  |

| VIN,Ipm   | IN and LPM pins voltage range                    | Vcc-35   | V <sub>CC</sub> | 1     |  |

| Cboot     | Recommended bootstrap ceramic capacitor          | 10       | 47              |       |  |

| Cload     | Maximum recommended equivalent gate capacitor    | —        | 240             | – nF  |  |

| Cdec      | Recommended Vcc & Vee decoupling capacitors*     | 22       | 33              | μF    |  |

| Ron       | OUTH series resistor to gate                     | 1.5      | 20              |       |  |

| Roff      | OUTL series resistor to gate                     | 1.5      | 20              | Ω     |  |

| R pull-up | Recommended pull-up resistor for IN and LPM pins | 10       | 100             | kΩ    |  |

| PWoff     | Minimum recommended OFF time on the IN pin       | 1        | _               |       |  |

| PWon      | Minimum recommended ON time on the IN pin        | 1        | —               | μs    |  |

\* Due to the high current application a good quality low ESR capacitor has to be used.

Numbers are indicative, a value about 40 times the load capacitance seen at the OutH and OutL pins is suggested.

#### **Static Electrical Characteristics**

| Symbol                | Definition                                                | Min | Тур  | Max  | Units | Test Conditions                                                    |

|-----------------------|-----------------------------------------------------------|-----|------|------|-------|--------------------------------------------------------------------|

| V <sub>CCUV+</sub>    | V <sub>CC</sub> -GND under-voltage rising edge            | _   | 11.7 | 12.8 |       |                                                                    |

| V <sub>CCUV-</sub>    | V <sub>cc</sub> -GND under-voltage falling edge           | 9.6 | 10.5 |      | V     | LPM = X, IN = Vcc, Vee = Gnd;                                      |

| V <sub>CCUVH</sub>    | V <sub>CC</sub> -GND under-voltage hysteresis             | 0.5 | 1.2  |      |       |                                                                    |

| VCB <sub>UV (*)</sub> | VCB under-voltage lockout                                 | 2.8 | 4    | 5.7  |       |                                                                    |

| I <sub>QGG</sub>      | Current out of the Gnd pin                                |     | 20   | 60   |       | IN = X, LPM = X                                                    |

| I <sub>QOUTL1</sub>   | Current flowing into the OUTL pin                         |     | 0    | 1.5  | μA    | IN = Vcc,LPM = X,<br>OUTH = NC, VoutL–Gnd = 15V                    |

| I <sub>QEESW</sub>    | V <sub>EE</sub> pin current, IN cycling                   |     | 3    | 8    |       | IN = 10 kHz - 50% duty cycle<br>LPM = Vcc, C <sub>LOAD</sub> = 0nF |

| I <sub>QEE0</sub>     | V <sub>EE</sub> pin current – output OFF – normal mode    |     | 1.5  | 4    |       | IN = Gnd, LPM = Vcc                                                |

| I <sub>QEE1</sub>     | V <sub>EE</sub> pin current – output ON – normal mode     |     | 0.8  | 1.6  |       | IN = Vcc, LPM = Vcc                                                |

| I <sub>QEELQ0</sub>   | V <sub>EE</sub> pin current – output OFF – low power mode |     | 0.6  | 2.0  |       | IN = Gnd, LPM = Gnd                                                |

| I <sub>QEELQ1</sub>   | V <sub>EE</sub> pin current – output ON – low power mode  | _   | 0.8  | 1.6  |       | IN = Vcc, LPM = Gnd                                                |

| I <sub>QEEUV</sub>    | V <sub>EE</sub> pin current at low Vcc supply             |     | 0.6  | 1.6  | mA    | $IN = X$ , $LPM = X$ , $V_{CC} < V_{CCUV}$ .                       |

| I <sub>QB</sub>       | CB pin sink current                                       |     | 0.5  | 1    |       | IN = Vcc, LPM = Vcc, Vcв-Vouth = 5.5                               |

| I <sub>QOUTH0</sub>   | OUTH pin sourced current – normal mode                    |     | 1    | 3.5  |       | IN = Gnd, LPM = Vcc<br>OUTH = $V_{EE}$ , OUTL = NC                 |

| IQOUTHOLQ             | OUTH pin sourced current – low power mode                 |     | 0.2  | 0.5  |       | IN = Gnd, LPM = Gnd<br>OUTH = $V_{EE}$ , OUTL = NC                 |

| I <sub>BOUTH</sub>    | CB pin sourced current – normal mode                      | 30  | 90   |      |       | IN = Gnd, LPM = Vcc,<br>OUTL = NC, CB = OUTH = Vee                 |

| I <sub>BOUTH_PI</sub> | CB pin pulsed sourced current – normal mode               | 90  | 200  | _    |       | Min pulse length 2us guaranteed by desi                            |

| I <sub>BOUTHLQ</sub>  | CB pin sourced current – low power mode                   | 0.5 | 5    | 23   |       | IN = Gnd, LPM = Gnd,<br>OUTL = NC, CB = OUTH = Vee                 |

| OUTH+ /IOUTL-         | OUTH /OUTL pins output current capability                 | 10  | _    | _    | Α     | LPM = X<br>VOUTL-: t < 100us, VOUTH+: CB charg                     |

| Vcc-VinH              | IN pin – output ON voltage                                | 1.5 | 2.5  | _    |       |                                                                    |

| Vcc-VinL              | IN pin – output OFF voltage                               | _   | 4.5  | 5.5  |       |                                                                    |

| V <sub>INhys</sub>    | IN pin voltage hysteresis                                 | 1   | 2    | _    |       |                                                                    |

| Vcc-VLPMH             | LPM pin normal mode voltage                               | 1.4 | 2    | _    | V     | Vcc-Gnd > Vccuv+                                                   |

| Vcc-VLPML             | LPM pin low power mode voltage                            |     | 3.2  | 3.8  |       |                                                                    |

| $V_{LPMhys}$          | LPM pin voltage hysteresis                                | 0.3 | 1.1  |      |       |                                                                    |

| I <sub>IN15</sub>     | IN pin sourced current                                    | 40  | 90   | 180  |       | IN = Gnd                                                           |

| I <sub>LPM15</sub>    | LPM pin sourced current                                   | 10  | 25   | 50   | μA    | LPM = Gnd                                                          |

|                       | OUTH transistor Rdson                                     |     | 100  | 200  |       | IN = Vcc, lout 10A, t < 100us,<br>Gnd = Vee, Vcв = Vоυтн + 5.5V    |

|                       | OUTL transistor Rdson                                     | _   | 200  | 400  | mΩ    | -IN = Gnd, lout = 10A,<br>t < 100us, Gnd = Vee                     |

| I <sub>PMOS (*)</sub> | OUTH Pulling- up current source                           | 15  | 30   | 120  | mA    | IN = Vcc, LPM = X,<br>Vcc - Vouth = 1.5V                           |

$V_{CC}$  – Gnd = 15V,  $V_{EE-}$  Gnd = -5V,  $C_{boot}$  = 15nF, Ron = Roff = 3 $\Omega$ , -40 °C < T<sub>A</sub> < 125 °C unless otherwise specified.

(\*)When VCB – VOUTH < VCB<sub>UV</sub>, OUTH pin remaining pulled-up to Vcc is guaranteed for at least 3usec with low impedance (=Ron) via Vdmos then continuously with larger impedance via Pmos (= Ipmos, see block diagram).

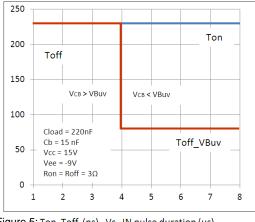

#### **Switching Electrical Characteristics**

$V_{CC}$  - Gnd = 15V, Vee - Gnd = -9V, Cboot = 15nF, Ron= Roff = 3 $\Omega$ ,  $C_{LOAD}$  = 220nF, -40 °C < T<sub>A</sub> < 125 °C unless otherwise specified.

| Symbol                         | Definition                                                  | Min. | Тур. | Max. | Units        | Test Conditions                       |

|--------------------------------|-------------------------------------------------------------|------|------|------|--------------|---------------------------------------|

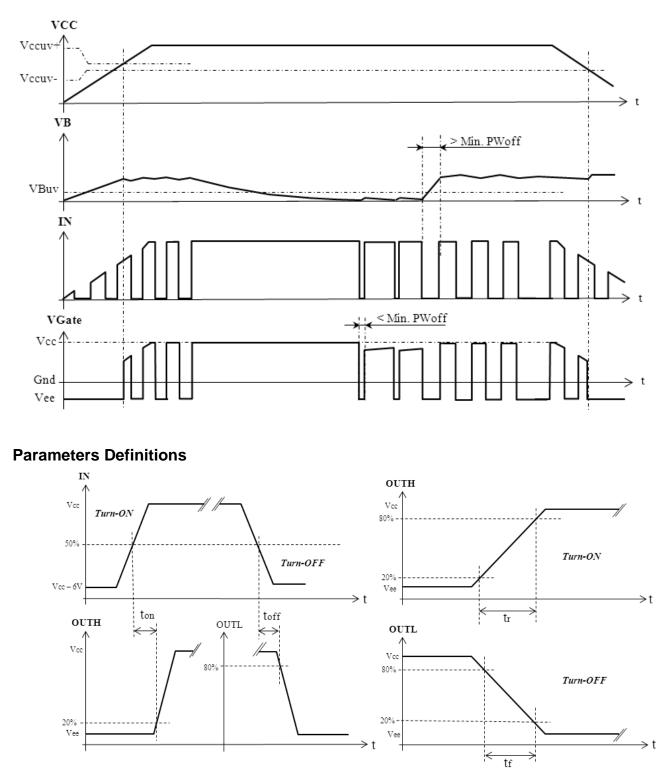

| t <sub>on</sub>                | OUTH turn on propagation delay                              | _    | 150  | 350  |              |                                       |

| t <sub>off</sub>               | OUTL turn off propagation delay                             |      | 230  | 350  |              | Coo poromotoro dofinitiono            |

| $t_{\text{off}\_\text{VCBuv}}$ | OUTL turn off prop. delay when Vcb < VCBuv $^*$             |      | 90   | 350  |              | See parameters definitions<br>LPM = X |

| tr                             | OUTH rise time                                              |      | 50   | 150  |              |                                       |

| t <sub>f</sub>                 | OUTL fall time                                              | _    | 50   | 150  | ns           |                                       |

| t <sub>rLQ</sub>               | OUTH rise time (IN=1, Vcc ramping up, LPM = Gnd)            | _    | 50   | 250  |              | $V_{EE}$ = LPM = Gnd, IN = Vcc        |

| t <sub>fLQ</sub>               | OUTL fall time (IN=1, Vcc ramping down, LPM = Gnd)          |      | 50   | 250  |              | $V_{EE}$ = LPM = Gnd, IN = Vcc        |

| Min Out-ON                     | ON time for 0.5µs IN pulse                                  | 200  | 600  | 900  |              | Cload = open                          |

| Min Out-OFF<br>cb discharged   | OFF time for 0.5µs IN pulse, CB discharged                  | 200  | 500  | 900  |              | Cload = open, CB = 15 nF              |

| Min Out-OFF<br>cb charged      | OFF time for 0.5µs IN pulse, CB charged                     | 200  | 400  | 900  |              | Cload = open, CB = 15 nF              |

| t <sub>onLPM</sub>             | LPM activation time (from LPM edge to $I_{CB} < IBOUTH/2$ ) | _    | 0.6  | 3    | 10           | by design                             |

| t <sub>offLPM</sub>            | LPM deactivation time (from LPM edge to ICB > IBOUTH/2)     | _    | 0.6  | 3    | μs by design |                                       |

\* See also Fig. 5

#### **Truth Table**

| IN  | LPM | VCC     | OUTH | OUTL | Status                                |

|-----|-----|---------|------|------|---------------------------------------|

| Х   | Х   | < Vccuv | Open | Vee  | IGBT or MOSFET = OFF – Low power mode |

| Gnd | Gnd | > Vccuv | Open | Vee  | IGBT or MOSFET = OFF – Low power mode |

| Gnd | Vcc | > Vccuv | Open | Vee  | IGBT or MOSFET = OFF – Normal mode    |

| Vcc | Gnd | > Vccuv | Vcc  | Open | IGBT or MOSFET = ON – Low power mode  |

| Vcc | Vcc | > Vccuv | Vcc  | Open | IGBT or MOSFET = ON – Normal mode     |

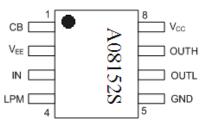

#### Lead Assignments

#### **Lead Definitions**

| Symbol | Description                                                                        | Pin |

|--------|------------------------------------------------------------------------------------|-----|

| СВ     | External Bootstrap capacitor (cf. typical connection schematic)                    | 1   |

| Vee    | Negative Supply Pin                                                                | 2   |

| IN     | Gate Drive Input, (IN= Vcc forces OutH = high)                                     | 3   |

| LPM    | Low Power Mode Input, LPM= GND activates the Low Power Mode                        | 4   |

| GND    | 0V – IGBT Emitter or MOSFET Source Connection (cf. typical connection schematic) 5 |     |

| OUTL   | Gate Drive Output Pull down                                                        | 6   |

| OUTH   | Gate Drive Output Pull up                                                          |     |

| Vcc    | Positive Supply Pin                                                                | 8   |

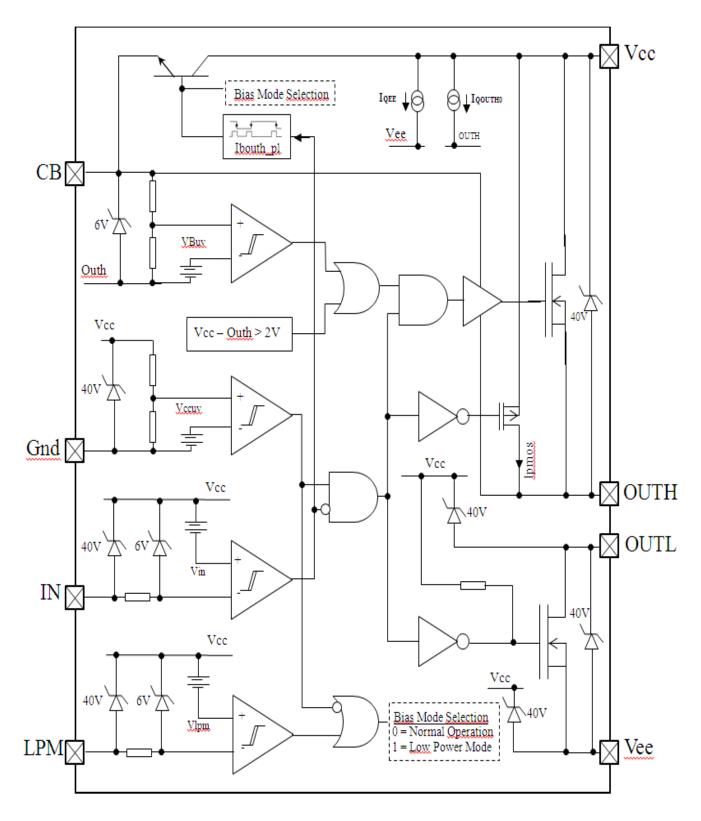

### **Functional Block Diagram**

#### **Timing Diagram**

Propagation delay definitions

Rise and fall time definitions

#### Parameters

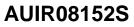

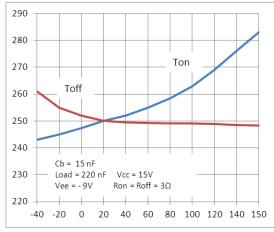

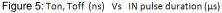

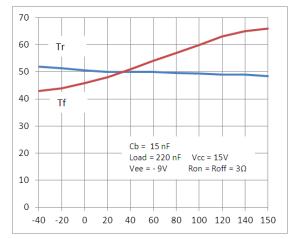

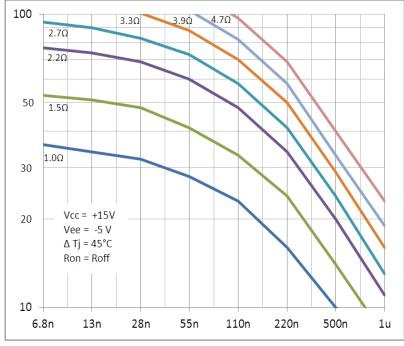

Figures are given for typical value @ Tj=25°C otherwise specified

Figure 3: Vccuv+, Vccuv- and Vcbuv (V) Vs Temperature (°C)

Figure 2: Tr and Tf (ns) Vs Temperature (°C)

Figure 4: OUTH & OUTL Rdson's Vs Temperature (°C)

DC+

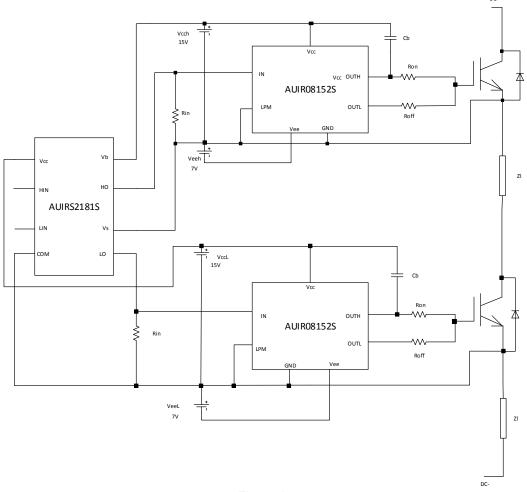

#### Examples of system schematics with HVIC

This section shows how the AUIR08152S can be driven by IR High Voltage IC (HVIC).

All the examples refer to an inverter leg; floating voltage sources to supply the high side AUIR08152S are named Vcch and Veeh, while voltage sources to supply the low side AUIR08152S are named Vccl and Veel.

In the examples, a 7V negative Veeh(I) is shown; this is usually enough to keep even big die size IGBT firmly clamped in their OFF state during dV/dt transients; in case the IGBTs do not require a negative gate voltage, Veeh(I) sources can simply be shorted to their relevant IC GND (h or I).

It is straightforward to say that, when multiple legs are considered, floating supplies must have galvanic isolation between each other (and w.r.to low side); low side supplies could be shared between the different legs but the choice if using multiple or shared low side supplies mostly depend upon the system layout.

Especially important in the emitter impedance ZI, as shown in the figures. Non negligible value of the emitter inductance creates imbalance between the emitter returns and may suggest using separate supplies also for the low side gate drivers.

**Example1 :** IGBT gate driving by AUIRS2181S and two AUIR08152S buffer ICs.

The AUIRS2181S is a 8 pin SOIC and does not have separate COM (power GND) and Vss (signal GND) pins. Therefore, COM is directly connected to the GND of the low side buffer IC but special care has to be taken when layouting power and control section.

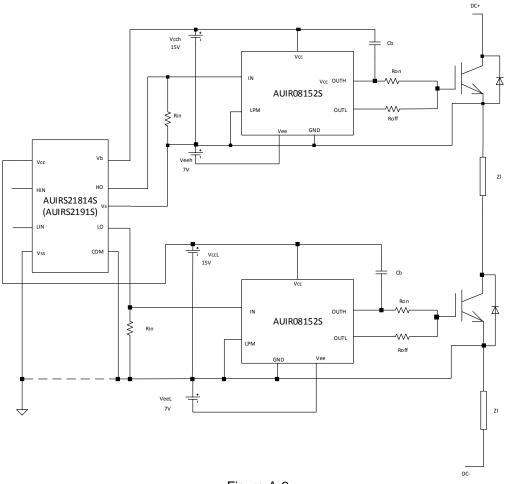

**Example 2:** IGBT gate driving by AUIRS21814S ( or AUIRS2191S) and two AUIR08152S buffer ICs.

Figure A-2

The AUIRS21814S (and the AUIRS2191S) have separate Vss and COM pins. They can be simply connected together or, better, connected to separate logic and power GND.

In any case, the low side AUIR08152S GND pin has to be connected to the low side IGBT emitter, and layouting care has to be taken that, in case of separate Vss and COM grounding, the imbalance between these two points doesn't exceed the data sheet value (usually +/-5V).

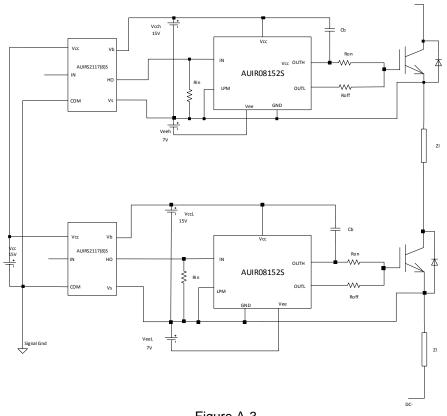

**Example 3:** IGBT gate driving by two AUIRS2117(8)S and two AUIR08152S buffer ICs.

Here, the situation is partially better in term of separation between logic and power GND, in that even the low side power GND can float -5V to +600V with respect to COM, which is connected to signal GND. Actually, because the negative Vs transient capability of the AUIRS2117(8), much more room is allowed for both positive and negative transients of the IGBT emitters w.r.to COM.

DC+

#### Figure A-3

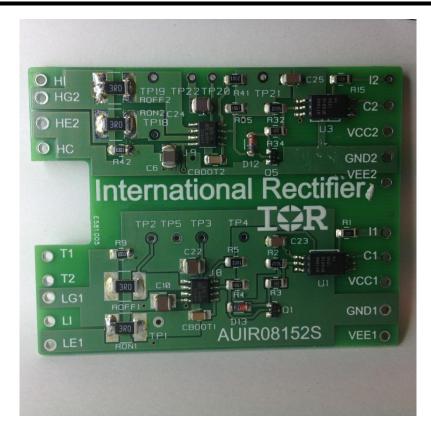

#### Examples of system schematics with Opto

The example in Figure A-4 is, again, a leg gate driver where the AUIR08152 are driven by optocouplers. The optocoupler only needs to drive a logic signal (the input of the buffer) so there is no need for high current capability. Its speed mostly depends upon system switching frequency and control aspects. The propagation delays and rise and fall times of the opto's stage must preferably be well below the buffer IC ones, to avoid introducing further delays which affect both the system control loop stability and the modulation depth. Figure A-4 shows the schematic of one of the leg sections ( high or low ) while Figure A-5 shows the layout.

Figure A-5

#### **General Application Hints**

#### IN & LPM interface

IN and LPM have a current capability of 10mA max (source and sink); these limits only apply in case the stage driving these signals may go above Vcc or below Vcc-40V.

In the majority of cases, when the driving stage is only an open collector, referenced at GND or –Vee, when looking at the functional block diagram, it appears the internal comparators have 6V zener clamp diodes, whose current is limited to much lower current by internal limiting resistors. These currents are  $I_{IN15}$  and  $I_{LPM15}$  and are reported in the static electrical characteristics for Vcc=15V and IN and LPM being pulled down at GND level. In any case, when driving IN and LPM via open collector outputs, a pull-up resistor is needed, to guarantee clean rise times (fall time are uniquely determined by the speed the open collectors turns-on).

Rise time is determined by the pull-up resistor and the equivalent pin capacitance to Vcc. Typically few hundred Ohm to few kOhm are placed here.

If a push pull, and not an open collector, stage is used to drive IN and LPM, no pull-up resistor is needed but pay attention the push pull stage is fed between Vcc and GND or Vcc and –Vee.

A pull down resistor (few hundred kOhm) is suggested instead, especially if long traces or cables connect the predriver to the buffer IC.

#### IC power dissipation

This figure is mostly related to the switching frequency, the value of external gate resistances, and the equivalent load capacitance (the IGBT gate Ciss).

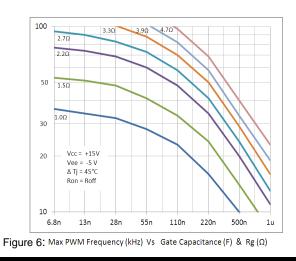

A complete characterization of the IC capabilities is given in figure 6, and shown here again for sake of clarity.

Max PWM Frequency (kHz) Vs Gate Capacitance (F) & Rg ( $\Omega$ )

The AUIR08152S features a self-clamping gate protection in case of the auxiliary power supply disappears. A resistor is pulling up the gate of the OUTL internal power MOSFET to keep OutL pulled down until a minimum Vcc is applied, when Vcc disappears (< about 3V) then the Vgate is clamped via the OUTH ESD diode. In this situation forcing OutL high injects current into the pin that charges the Vcc decoupling capacitor and reactivates the internal OUTL output power MOSFET (for more info see the Functional Block Diagram).

🔿 OUTH2 If no negative bias is used, Vee shall be connected to Gnd a) OUTH and OUTL pins shall never be shorted together b) Decoupling capacitors shall be ceramic types and implemented c) as close as possible of the AUIR08152S supply pins The decoupling capacitors shall be at least 40 times bigger than d) the max. Cload and of low ESR type, in order to avoid any Vccuv oscillations n e) IN and LPM pins shall never be left open PCB Layout Example

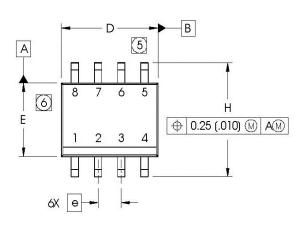

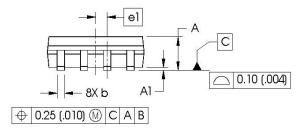

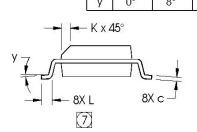

#### Case Outline – SO8

Dimensions are shown in millimeters (inches)

| DIM | INC     | ЖES   | MILLIN | <b>M</b> ETERS |

|-----|---------|-------|--------|----------------|

|     | MIN     | MAX   | MIN    | MAX            |

| Α   | .0532   | .0688 | 1.35   | 1.75           |

| A1  | .0040   | .0098 | 0.10   | 0.25           |

| b   | .013    | .020  | 0.33   | 0.51           |

| С   | .0075   | .0098 | 0.19   | 0.25           |

| D   | .189    | .1968 | 4.80   | 5.00           |

| Е   | .1497   | .1574 | 3.80   | 4.00           |

| е   | .050 B. | ASIC  | 1.27 E | BASIC          |

| e1  | .025 B  | ASIC  | 0.635  | BASIC          |

| Н   | .2284   | .2440 | 5.80   | 6.20           |

| К   | .0099   | .0196 | 0.25   | 0.50           |

| L   | .016    | .050  | 0.40   | 1.27           |

| v   | 0°      | 8°    | 0°     | 8°             |

#### NOTES:

- 1. DIMENSIONING & TOLERANCING PER ASME Y14.5M-1994.

- 2. CONTROLLING DIMENSION: MILLIMETER

- 3. DIMENSIONS ARE SHOWN IN MILLIMETERS (INCHES).

- 4. OUT LINE CONFORMS TO JEDEC OUT LINE MS-012AA.

- 5 DIMENSION DOES NOT INCLUDE MOLD PROTRUSIONS. MOLD PROTRUSIONS NOT TO EXCEED 0.15 (.006).

- DIMENSION DOES NOT INCLUDE MOLD PROTRUSIONS. MOLD PROTRUSIONS NOT TO EXCEED 0.25 (.010).

- DIMENSION IS THE LENGTH OF LEAD FOR SOLDERING TO A SUBSTRATE.

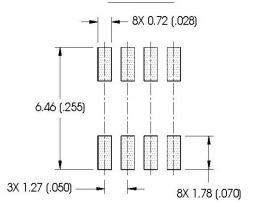

#### FOOTPRINT

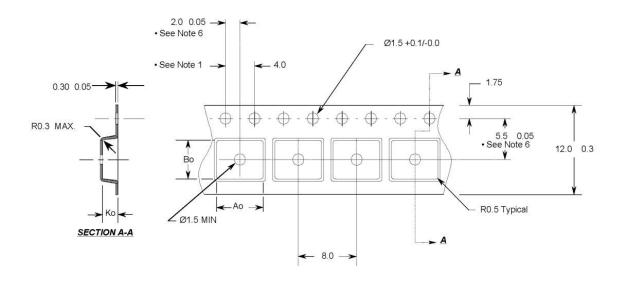

#### Tape & Reel **SO**8

#### Notes:

1. 10 sprocket hole pitch cumulative tolerance 0.2

2. Camber not to exceed 1mm in 100mm 3. Material: Black Conductive Advantek Polystyrene

- Ao = 6.4 mm Bo = 5.2 mm

- Ko = 2.1 mm

- All Dimensions in Millimeters -

- 4. Ao and Bo measured on a plane 0.3mm above the bottom of the pocket

- 5. Ko measured from a plane on the inside bottom of the

- pocket to the top surface of the carrier. 6. Pocket position relative to sprocket hole measured as

true position of pocket, not pocket hole.

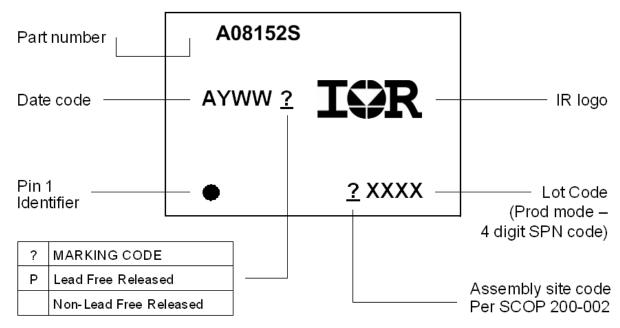

#### **Part Marking Information**

## **Qualification Information**<sup>†</sup>

| Qualification Level        |                  | Automotive<br>(per AEC-Q100)<br>Comments: This family of ICs has passed an<br>Automotive qualification. IR's Industrial and<br>Consumer qualification level is granted by extensio<br>of the higher Automotive level. |                                                       |  |

|----------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|--|

| Moisture Sensitivity Level |                  | SOIC8N                                                                                                                                                                                                                | MSL2 <sup>††</sup> 260°C<br>(per IPC/JEDEC J-STD-020) |  |

|                            | Machine Model    |                                                                                                                                                                                                                       | ss M2 (+/-200V)<br>AEC-Q100-003)                      |  |

| ESD                        | Human Body Model | Class H2 (+/-2500V)<br>(per AEC-Q100-002)                                                                                                                                                                             |                                                       |  |

| Charged Device Model       |                  | Class C4 (Pass +/-1000V)<br>(per AEC-Q100-011)                                                                                                                                                                        |                                                       |  |

| IC Latch-Up Test           |                  |                                                                                                                                                                                                                       | lass II, Level A<br>AEC-Q100-004)                     |  |

| RoHS                       | Compliant        | Yes                                                                                                                                                                                                                   |                                                       |  |

- + Qualification standards can be found at International Rectifier's web site http://www.irf.com/

- ++ Higher MSL ratings may be available for the specific package types listed here.Please contact your International Rectifier sales representative for further information.

Published by Infineon Technologies AG 81726 München, Germany © Infineon Technologies AG 2015 All Rights Reserved.

#### **IMPORTANT NOTICE**

The information given in this document shall in <u>no event</u> be regarded as a guarantee of conditions or characteristics ("Beschaffenheitsgarantie"). With respect to any examples, hints or any typical values stated herein and/or any information regarding the application of the product, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation warranties of non-infringement of intellectual property rights of any third party.

In addition, any information given in this document is subject to customer's compliance with its obligations stated in this document and any applicable legal requirements, norms and standards concerning customer's products and any use of the product of Infineon Technologies in customer's applications.

The data contained in this document is exclusively intended for technically trained staff. It is the responsibility of customer's technical departments to evaluate the suitability of the product for the intended application and the completeness of the product information given in this document with respect to such application.

For further information on the product, technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies office (<u>www.infineon.com</u>).

#### **WARNINGS**

Due to technical requirements products may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies office.

Except as otherwise explicitly approved by Infineon Technologies in a written document signed by authorized representatives of Infineon Technologies, Infineon Technologies' products may <u>not</u> be used in any applications where a failure of the product or any consequences of the use thereof can reasonably be expected to result in personal injury.

# **Revision History**

| Revision | Date                           | Notes/Changes                                       |

|----------|--------------------------------|-----------------------------------------------------|

| A1       | August 5 <sup>th</sup> , 2013  | Preliminary Datasheet AUIR08152S                    |

| A2       | August 23 <sup>rd</sup> 2013   | Advanced datasheet                                  |

| A3       | August 26 <sup>th</sup> 2013   | Advanced datasheet                                  |

| A4       | September 2 <sup>nd</sup> 2013 | Final datasheet, updated lout+ and lout- definition |

| A5       | Dec. 5 <sup>th</sup> , 2013    | Updated cosmetic for production                     |

| A6       | Aug. 27 <sup>th</sup> , 2014   | Updated note * on page 3, updated footprint         |

| A7       | Sept 25, 2015                  | Application section totally updated                 |

| A8       | Nov. 09 <sup>th</sup> , 2015   | Few minor mistyping errors corrected.               |

# **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

International Rectifier: