## 2Msps/3Msps, Low-Power, Serial 12-/10-/8-Bit ADCs

### **General Description**

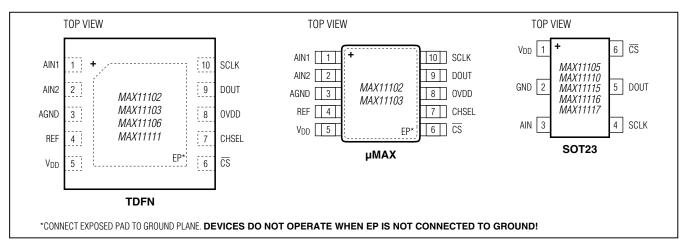

The MAX11102/MAX11103/MAX11105/MAX11106/

MAX11110/MAX11111/MAX11115/MAX11116/

MAX11117 are 12-/10-/8-bit, compact, high-speed, low-

power, successive approximation analog-to-digital con-

verters (ADCs). These high-performance ADCs include a high-dynamic range sample-and-hold and a high-speed

serial interface. These ADCs accept a full-scale input

from 0V to the power supply or to the reference voltage.

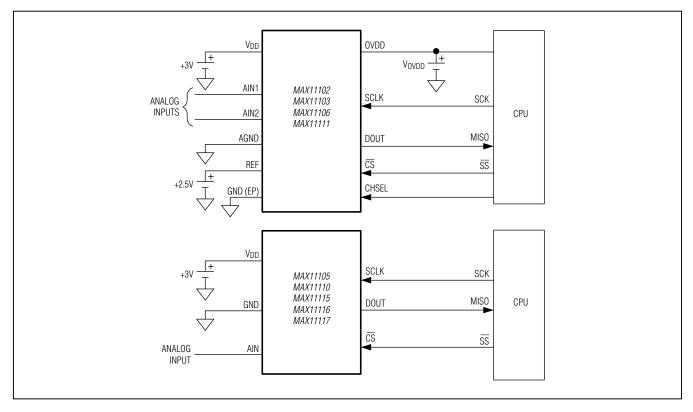

The MAX11102/MAX11103/MAX11106/MAX11111 fea-

ture dual, single-ended analog inputs connected to the

ADC core using a 2:1 MUX. The devices also include a

separate supply input for data interface and a dedicated

input for reference voltage. In contrast, the single-chan-

nel devices generate the reference voltage internally

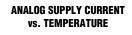

These ADCs operate from a 2.2V to 3.6V supply and consume only 5.2mW at 3Msps and 3.7mW at 2Msps.

The devices include full power-down mode and fast

wake-up for optimal power management and a high-

speed 3-wire serial interface. The 3-wire serial interface

directly connects to SPI, QSPI™, and MICROWIRE®

Excellent dynamic performance, low voltage, low power,

ease of use, and small package size make these con-

verters ideal for portable battery-powered data-acquisition applications, and for other applications that demand

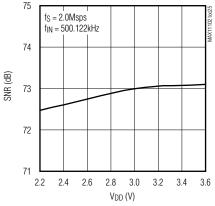

These ADCs are available in a 10-pin TDFN package,

10-pin  $\mu$ MAX® package, and a 6-pin SOT23 package. These devices operate over the -40°C to +125°C tem-

low-power consumption and minimal space.

from the power supply.

devices without external logic.

**Features**

- ♦ 2Msps/3Msps Conversion Rate, No Pipeline Delay

- ♦ 12-/10-/8-Bit Resolution

- ♦ 1-/2-Channel, Single-Ended Analog Inputs

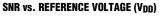

- Low-Noise 73dB SNR

- Variable I/O: 1.5V to 3.6V (Dual-Channel Only) Allows the Serial Interface to Connect Directly to 1.5V, 1.8V, 2.5V, or 3V Digital Systems

- ♦ 2.2V to 3.6V Supply Voltage

- Low Power

3.7mW at 2Msps

5.2mW at 3Msps

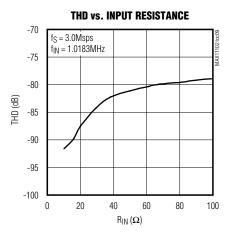

Very Low Power Consumption at 2.5µA/ksps

- External Reference Input (Dual-Channel Devices Only)

- ♦ 1.3µA Power-Down Current

- SPI-/QSPI-/MICROWIRE-Compatible Serial Interface

- ♦ 10-Pin, 3mm x 3mm TDFN Package

- ♦ 10-Pin, 3mm x 5mm µMAX Package

- ♦ 6-Pin, 2.8mm x 2.9mm SOT23 Package

- ♦ Wide -40°C to +125°C Operation

#### Applications

Data Acquisition Portable Data Logging Medical Instrumentation Battery-Operated Systems Communication Systems Automotive Systems

### **Ordering Information**

| PART           | PIN-PACKAGE | BITS | SPEED (Msps) | NO. OF CHANNELS | TOP MARK |

|----------------|-------------|------|--------------|-----------------|----------|

| MAX11102AUB+   | 10 µMAX-EP* | 12   | 2            | 2               | +ABBA    |

| MAX11102AUB/V+ | 10 µMAX-EP* | 12   | 2            | 2               | +ABBR    |

| MAX11102ATB+   | 10 TDFN-EP* | 12   | 2            | 2               | +AWI     |

| MAX11103AUB+   | 10 µMAX-EP* | 12   | 3            | 2               | +AAAU    |

| MAX11103ATB+   | 10 TDFN-EP* | 12   | 3            | 2               | +AWV     |

#### Ordering Information continued at end of data sheet.

**Note:** All devices are specified over the -40°C to +125°C operating temperature range. +Denotes a lead(Pb)-free/RoHS-compliant package.

\*EP = Exposed pad.

perature range.

QSPI is a trademark of Motorola, Inc. MICROWIRE is a registered trademark of National Semiconductor Corp. μMAX is a registered trademark of Maxim Integrated Products, Inc.

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim's website at www.maximintegrated.com.

## 2Msps/3Msps, Low-Power, Serial 12-/10-/8-Bit ADCs

#### **ABSOLUTE MAXIMUM RATINGS**

| VDD to GND0.3V to +4V                                 |

|-------------------------------------------------------|

| REF, OVDD, AIN1, AIN2, AIN to GND0.3V to the lower of |

| (V <sub>DD</sub> + 0.3V) and +4V                      |

| CS, SCLK, CHSEL, DOUT TO GND0.3V to the lower of      |

| (VOVDD + 0.3V) and +4V                                |

| AGND to GND0.3V to +0.3V                              |

| Input/Output Current (all pins)50mA                   |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |

| 6-Pin SOT23 (derate 8.7mW/°C above +70°C)696mW        |

| 10-Pin TDFN (derate 24.4mW/°C above +7 | 70°C)1951mW    |

|----------------------------------------|----------------|

| 10-Pin µMAX (derate 8.8mW/°C above +70 | 0°C)707.3mW    |

| Operating Temperature Range            | 40°C to +125°C |

| Junction Temperature                   | +150°C         |

| Storage Temperature Range              | 65°C to +150°C |

| Lead Temperature (soldering, 10s)      | +300°C         |

| Soldering Temperature (reflow)         | +260°C         |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### ELECTRICAL CHARACTERISTICS (MAX11102/MAX11103)

$(V_{DD} = 2.2V \text{ to } 3.6V, V_{REF} = V_{DD}, V_{OVDD} = V_{DD}. MAX11102: f_{SCLK} = 32MHz, 50\% duty cycle, 2Msps. MAX11103: f_{SCLK} = 48MHz, 50\% duty cycle, 3Msps. C_{DOUT} = 10pF, T_A = -40^{\circ}C \text{ to } +125^{\circ}C, unless otherwise noted. Typical values are at T_A = +25^{\circ}C.$

| PARAMETER                             | SYMBOL                   | CONDITIONS                                                                            | MIN  | ТҮР   | МАХ | UNITS |

|---------------------------------------|--------------------------|---------------------------------------------------------------------------------------|------|-------|-----|-------|

| DC ACCURACY                           |                          |                                                                                       |      |       |     |       |

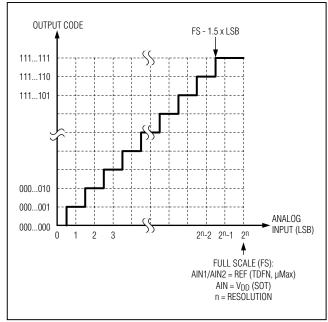

| Resolution                            |                          |                                                                                       | 12   |       |     | Bits  |

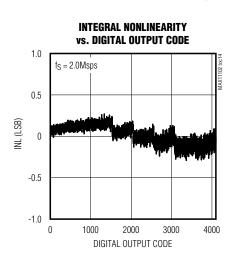

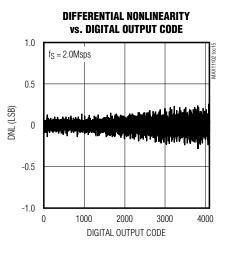

| Integral Nonlinearity                 | INL                      |                                                                                       |      |       | ±1  | LSB   |

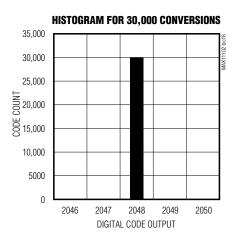

| Differential Nonlinearity             | DNL                      | No missing codes                                                                      |      |       | ±1  | LSB   |

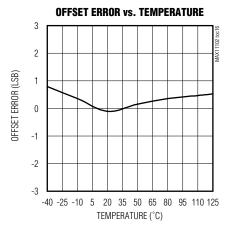

| Offset Error                          | OE                       |                                                                                       |      | ±0.3  | ±3  | LSB   |

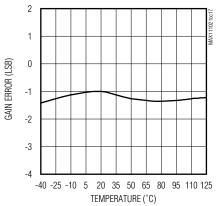

| Gain Error                            | GE                       | Excluding offset and reference errors                                                 |      | ±1    | ±3  | LSB   |

| Total Unadjusted Error                | TUE                      |                                                                                       |      | ±1.5  |     | LSB   |

| Channel-to-Channel Offset<br>Matching |                          |                                                                                       |      | ±0.4  |     | LSB   |

| Channel-to-Channel Gain<br>Matching   |                          |                                                                                       |      | ±0.05 |     | LSB   |

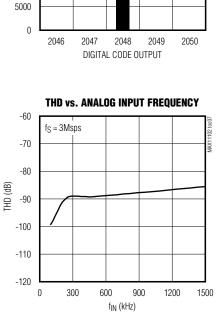

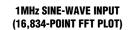

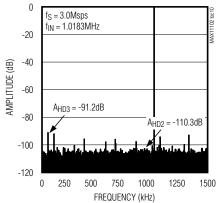

| DYNAMIC PERFORMANCE (MA               | X11103: f <sub>AIN</sub> | = 1MHz, MAX11102: f <sub>AIN</sub> = 0.5MHz)                                          |      |       |     |       |

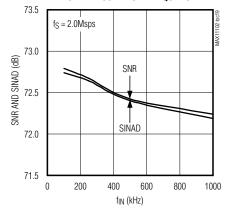

|                                       |                          | MAX11103                                                                              | 70   | 72    |     |       |

| Signal-to-Noise and Distortion        | SINAD                    | MAX11102                                                                              | 70   | 72.5  |     | dB    |

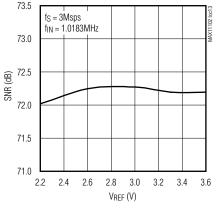

| Cignal to Naisa Datia                 | SNR                      | MAX11103                                                                              | 70.5 | 72    |     | dD    |

| Signal-to-Noise Ratio                 | SINK                     | MAX11102                                                                              | 70.5 | 73    |     | dB    |

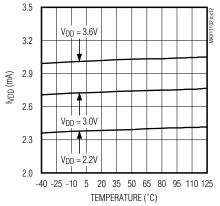

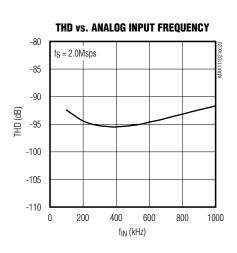

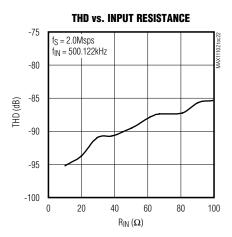

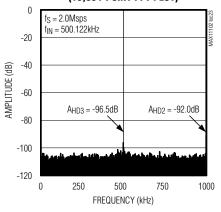

| Total Harmonic Distortion             | THD                      | MAX11103                                                                              |      | -85   | -75 | dB    |

| Total Harmonic Distortion             |                          | MAX11102                                                                              |      | -85   | -76 | uв    |

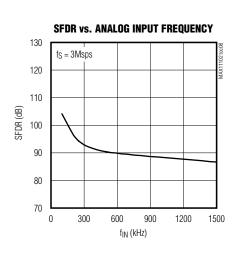

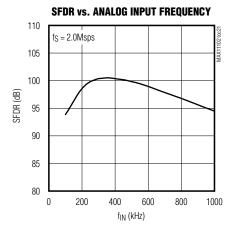

| Spurious Free Dynamic Donge           | SFDR                     | MAX11103                                                                              | 76   | 85    |     | dB    |

| Spurious-Free Dynamic Range           | SFDR                     | MAX11102                                                                              | 77   | 85    |     | uв    |

| Intermodulation Distortion            | IMD                      | MAX11103: f1 = 1.0003MHz, f2 = 0.99955MHz<br>MAX11102: f1 = 500.15kHz, f2 = 499.56kHz |      | -84   |     | dB    |

| Full-Power Bandwidth                  |                          | -3dB point                                                                            |      | 40    |     | MHz   |

| Full-Linear Bandwidth                 |                          | SINAD > 68dB                                                                          |      | 2.5   |     | MHz   |

| Small-Signal Bandwidth                |                          |                                                                                       |      | 45    |     | MHz   |

| Crosstalk                             |                          |                                                                                       |      | -90   |     | dB    |

## 2Msps/3Msps, Low-Power, Serial 12-/10-/8-Bit ADCs

#### ELECTRICAL CHARACTERISTICS (MAX11102/MAX11103) (continued)

$(V_{DD} = 2.2V \text{ to } 3.6V, V_{REF} = V_{DD}, V_{OVDD} = V_{DD}. MAX11102: f_{SCLK} = 32MHz, 50\% duty cycle, 2Msps. MAX11103: f_{SCLK} = 48MHz, 50\% duty cycle, 3Msps. C_{DOUT} = 10pF, T_A = -40^{\circ}C \text{ to } +125^{\circ}C, unless otherwise noted. Typical values are at T_A = +25^{\circ}C.$

| PARAMETER                            | SYMBOL           | CONDITIONS                       | MIN             | ТҮР             | МАХ                       | UNITS |

|--------------------------------------|------------------|----------------------------------|-----------------|-----------------|---------------------------|-------|

| CONVERSION RATE                      | -                |                                  |                 |                 |                           |       |

| <b>-</b>                             |                  | MAX11103                         | 0.03            |                 | 3                         |       |

| Throughput                           |                  | MAX11102                         | 0.02            |                 | 2                         | Msps  |

|                                      |                  | MAX11103                         | 260             |                 |                           |       |

| Conversion Time                      |                  | MAX11102                         | 391             |                 |                           | ns    |

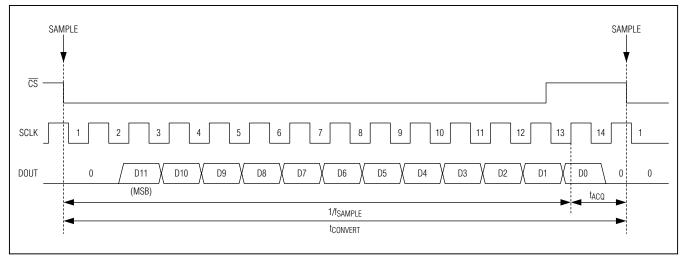

| Acquisition Time                     | tacq             |                                  | 52              |                 |                           | ns    |

| Aperture Delay                       |                  | From CS falling edge             |                 | 4               |                           | ns    |

| Aperture Jitter                      |                  |                                  |                 | 15              |                           | ps    |

| Serial-Clock Frequency               | four             | MAX11103                         | 0.48            |                 | 48                        | MHz   |

|                                      | fCLK             | MAX11102                         | 0.32            |                 | 32                        |       |

| ANALOG INPUT (AIN1, AIN2)            |                  |                                  |                 |                 |                           |       |

| Input Voltage Range                  | VAIN_            |                                  | 0               |                 | VREF                      | V     |

| Input Leakage Current                | lila             |                                  |                 | 0.002           | ±1                        | μA    |

| Input Capacitance                    | CAIN_            | Track                            |                 | 20              |                           | рF    |

|                                      | CAIN_            | Hold                             |                 | 4               |                           | pr    |

| EXTERNAL REFERENCE INPU              | T (REF)          |                                  |                 |                 |                           |       |

| Reference Input-Voltage Range        | VREF             |                                  | 1               |                 | V <sub>DD</sub> +<br>0.05 | V     |

| Reference Input Leakage<br>Current   | l <sub>ILR</sub> | Conversion stopped               |                 | 0.005           | ±1                        | μA    |

| Reference Input Capacitance          | CREF             |                                  |                 | 5               |                           | рF    |

| DIGITAL INPUTS (SCLK, CS, C          | HSEL)            |                                  | •               |                 |                           |       |

| Digital Input High Voltage           | VIH              |                                  | 0.75 x<br>Vovdd |                 |                           | V     |

| Digital Input Low Voltage            | VIL              |                                  |                 |                 | 0.25 x<br>Vovdd           | V     |

| Digital Input Hysteresis             | VHYST            |                                  |                 | 0.15 x<br>Vovdd |                           | V     |

| Digital Input Leakage Current        | Ι <sub>Ι</sub> Γ | Inputs at GND or V <sub>DD</sub> |                 | 0.001           | ±1                        | μA    |

| Digital Input Capacitance            | CIN              |                                  |                 | 2               |                           | pF    |

| DIGITAL OUTPUT (DOUT)                |                  |                                  |                 |                 |                           |       |

| Output High Voltage                  | VOH              | ISOURCE = 200µA                  | 0.85 x<br>Vovdd |                 |                           | V     |

| Output Low Voltage                   | V <sub>OL</sub>  | I <sub>SINK</sub> = 200µA        |                 |                 | 0.15 x<br>Vovdd           | V     |

| High-Impedance Leakage<br>Current    | I <sub>OL</sub>  |                                  |                 |                 | ±1.0                      | μA    |

| High-Impedance Output<br>Capacitance | Соит             |                                  |                 | 4               |                           | pF    |

## 2Msps/3Msps, Low-Power, Serial 12-/10-/8-Bit ADCs

### ELECTRICAL CHARACTERISTICS (MAX11102/MAX11103) (continued)

$(V_{DD} = 2.2V \text{ to } 3.6V, V_{REF} = V_{DD}, V_{OVDD} = V_{DD}. MAX11102: f_{SCLK} = 32MHz, 50\% duty cycle, 2Msps. MAX11103: f_{SCLK} = 48MHz, 50\% duty cycle, 3Msps. C_{DOUT} = 10pF, T_A = -40^{\circ}C \text{ to } +125^{\circ}C, unless otherwise noted. Typical values are at T_A = +25^{\circ}C.$

| PARAMETER                                         | SYMBOL         | CONDITIONS                                  | MIN | ТҮР  | МАХ                    | UNITS |

|---------------------------------------------------|----------------|---------------------------------------------|-----|------|------------------------|-------|

| POWER SUPPLY                                      |                |                                             |     |      |                        |       |

| Positive Supply Voltage                           | VDD            |                                             | 2.2 |      | 3.6                    | V     |

| Digital I/O Supply Voltage                        | Vovdd          |                                             | 1.5 |      | V <sub>DD</sub>        | V     |

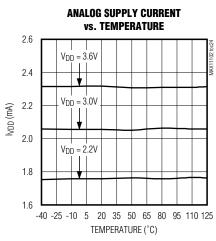

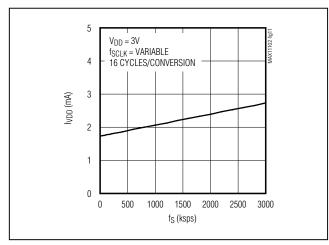

|                                                   | lu = =         | MAX11103, VAIN_ = VGND                      |     |      | 3.3                    |       |

| Positive Supply Current                           | IVDD           | MAX11102, VAIN_ = VGND                      |     |      | 2.6                    |       |

| (Full-Power Mode)                                 |                | MAX11103, VAIN_ = VGND                      |     |      | 0.33                   | mA    |

|                                                   | IOVDD          | MAX11102, VAIN_ = VGND                      |     |      | 0.22<br>8<br>8<br>3 10 |       |

| Positive Supply Current (Full-                    | lu = =         | MAX11103                                    |     | 1.98 |                        | mA    |

| Power Mode), No Clock                             | IVDD           | MAX11102                                    |     | 1.48 |                        |       |

| Power-Down Current                                | IPD            | Leakage only                                |     | 1.3  | 10                     | μA    |

| Line Rejection                                    |                | $V_{DD} = +2.2V$ to +3.6V, $V_{REF} = 2.2V$ |     | 0.7  |                        | LSB/V |

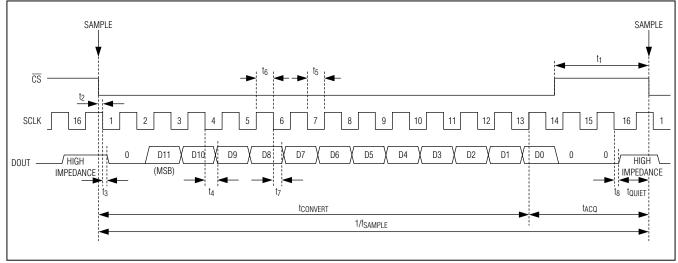

| TIMING CHARACTERISTICS (No                        | ote 1)         |                                             |     |      |                        |       |

| Quiet Time                                        | tQ             | (Note 2)                                    | 4   |      |                        | ns    |

| CS Pulse Width                                    | t1             | (Note 2)                                    | 10  |      |                        | ns    |

| CS Fall to SCLK Setup                             | t2             | (Note 2)                                    | 5   |      |                        | ns    |

| CS Falling Until DOUT High-<br>Impedance Disabled | t3             | (Note 2)                                    | 1   |      |                        | ns    |

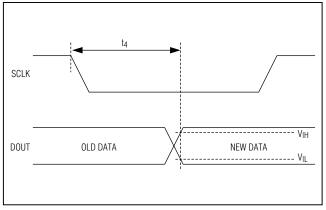

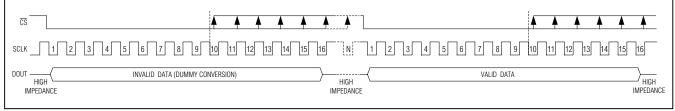

| Data Access Time After SCLK                       |                | Figure 2, V <sub>OVDD</sub> = 2.2V - 3.6V   |     |      | 15                     |       |

| Falling Edge                                      | t4             | Figure 2, V <sub>OVDD</sub> = 1.5V - 2.2V   |     |      | 16.5                   | ns    |

| SCLK Pulse Width Low                              | t5             | Percentage of clock period (Note 2)         | 40  |      | 60                     | %     |

| SCLK Pulse Width High                             | t <sub>6</sub> | Percentage of clock period (Note 2)         | 40  |      | 60                     | %     |

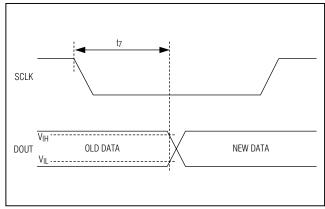

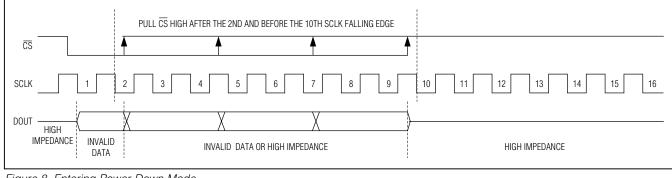

| Data Hold Time From SCLK<br>Falling Edge          | t7             | Figure 3                                    | 5   |      |                        | ns    |

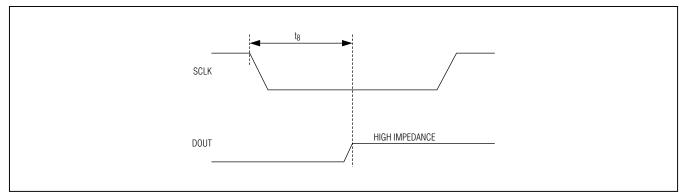

| SCLK Falling Until DOUT High-<br>Impedance        | t8             | Figure 4 (Note 2)                           | 2.5 |      | 14                     | ns    |

| Power-Up Time                                     |                | Conversion cycle (Note 2)                   |     |      | 1                      | Cycle |

#### **ELECTRICAL CHARACTERISTICS (MAX11105)**

(VDD = 2.2V to 3.6V, f<sub>SCLK</sub> = 32MHz, 50% duty cycle, 2Msps, C<sub>DOUT</sub> = 10pF, T<sub>A</sub> = -40°C to +125°C, unless otherwise noted. Typical values are at  $T_A$  = +25°C.)

| PARAMETER                      | SYMBOL | CONDITIONS                            | MIN  | ТҮР  | MAX | UNITS |

|--------------------------------|--------|---------------------------------------|------|------|-----|-------|

| DC ACCURACY                    |        |                                       |      |      |     |       |

| Resolution                     |        |                                       | 12   |      |     | Bits  |

| Integral Nonlinearity          | INL    |                                       |      |      | ±1  | LSB   |

| Differential Nonlinearity      | DNL    | No missing codes                      |      |      | ±1  | LSB   |

| Offset Error                   | OE     |                                       |      | ±0.3 | ±3  | LSB   |

| Gain Error                     | GE     | Excluding offset and reference errors |      | ±1   | ±3  | LSB   |

| Total Unadjusted Error         | TUE    |                                       |      | ±1.5 |     | LSB   |

| DYNAMIC PERFORMANCE            |        |                                       |      |      |     |       |

| Signal-to-Noise and Distortion | SINAD  | f <sub>AIN</sub> = 500kHz             | 70   | 72.5 |     | dB    |

| Signal-to-Noise Ratio          | SNR    | f <sub>AIN</sub> = 500kHz             | 70.5 | 73   |     | dB    |

## 2Msps/3Msps, Low-Power, Serial 12-/10-/8-Bit ADCs

### ELECTRICAL CHARACTERISTICS (MAX11105) (continued)

(VDD = 2.2V to 3.6V, f<sub>SCLK</sub> = 32MHz, 50% duty cycle, 2Msps, C<sub>DOUT</sub> = 10pF, T<sub>A</sub> = -40°C to +125°C, unless otherwise noted. Typical values are at  $T_A$  = +25°C.)

| PARAMETER                                    | SYMBOL          | CONDITIONS                                               | MIN            | TYP            | MAX            | UNITS |

|----------------------------------------------|-----------------|----------------------------------------------------------|----------------|----------------|----------------|-------|

| Total Harmonic Distortion                    | THD             | f <sub>AIN</sub> = 500kHz                                |                | -85            | -76            | dB    |

| Spurious-Free Dynamic Range                  | SFDR            | fain = 500kHz                                            | 77             | 85             |                | dB    |

| Intermodulation Distortion                   | IMD             | f <sub>1</sub> = 500.15 kHz, f <sub>2</sub> = 499.56 kHz |                | -84            |                | dB    |

| Full-Power Bandwidth                         |                 | -3dB point                                               |                | 40             |                | MHz   |

| Full-Linear Bandwidth                        |                 | SINAD > 68dB                                             |                | 2.5            |                | MHz   |

| Small-Signal Bandwidth                       |                 |                                                          |                | 45             |                | MHz   |

| CONVERSION RATE                              |                 |                                                          |                |                |                |       |

| Throughput                                   |                 |                                                          | 0.02           |                | 2              | Msps  |

| Conversion Time                              |                 |                                                          | 391            |                |                | ns    |

| Acquisition Time                             | tacq            |                                                          | 52             |                |                | ns    |

| Aperture Delay                               |                 | From CS falling edge                                     |                | 4              |                | ns    |

| Aperture Jitter                              |                 |                                                          |                | 15             |                | ps    |

| Serial Clock Frequency                       | fCLK            |                                                          | 0.32           |                | 32             | MHz   |

| ANALOG INPUT                                 |                 |                                                          |                |                |                |       |

| Input Voltage Range                          | VAIN            |                                                          | 0              |                | Vdd            | V     |

| Input Leakage Current                        | lila            |                                                          |                | 0.002          | ±1             | μA    |

| · E                                          |                 | Track                                                    |                | 20             |                | _     |

| Input Capacitance                            | CAIN            | Hold                                                     |                | 4              |                | pF    |

| DIGITAL INPUTS (SCLK, CS, C                  | HSEL)           | ,                                                        |                |                |                |       |

| Digital Input High Voltage                   | VIH             |                                                          | 0.75 x<br>Vvdd |                |                | V     |

| Digital Input Low Voltage                    | VIL             |                                                          |                |                | 0.25 x<br>Vvdd | V     |

| Digital Input Hysteresis                     | VHYST           |                                                          |                | 0.15 x<br>Vvdd |                | V     |

| Digital Input Leakage Current                | Ι <sub>Ι</sub>  | Inputs at GND or V <sub>DD</sub>                         |                | 0.001          | ±1             | μA    |

| Digital Input Capacitance                    | CIN             |                                                          |                | 2              |                | pF    |

| DIGITAL OUTPUT (DOUT)                        |                 |                                                          | ·              |                |                |       |

| Output High Voltage                          | V <sub>OH</sub> | ISOURCE = 200µA                                          | 0.85 x<br>Vvdd |                |                | V     |

| Output Low Voltage                           | V <sub>OL</sub> | I <sub>SINK</sub> = 200µA                                |                |                | 0.15 x<br>Vvdd | V     |

| High-Impedance Leakage<br>Current            | I <sub>OL</sub> |                                                          |                |                | ±1.0           | μA    |

| High-Impedance Output<br>Capacitance         | Cout            |                                                          |                | 4              |                | pF    |

| POWER SUPPLY                                 |                 |                                                          |                |                |                |       |

| Positive Supply Voltage                      | Vdd             |                                                          | 2.2            |                | 3.6            | V     |

| Positive Supply Current<br>(Full-Power Mode) | IVDD            | VAIN = VGND                                              |                |                | 2.6            | mA    |

## 2Msps/3Msps, Low-Power, Serial 12-/10-/8-Bit ADCs

### ELECTRICAL CHARACTERISTICS (MAX11105) (continued)

(VDD = 2.2V to 3.6V, fSCLK = 32MHz, 50% duty cycle, 2Msps, CDOUT = 10pF, TA = -40°C to +125°C, unless otherwise noted. Typical values are at TA = +25°C.)

| PARAMETER                                               | SYMBOL         | CONDITIONS                                 | MIN | ТҮР  | MAX | UNITS |

|---------------------------------------------------------|----------------|--------------------------------------------|-----|------|-----|-------|

| Positive Supply Current (Full-<br>Power Mode), No Clock | IVDD           |                                            |     | 1.48 |     | mA    |

| Power-Down Current                                      | IPD            | Leakage only                               |     | 1.3  | 10  | μA    |

| Line Rejection                                          |                | $V_{DD} = +2.2V \text{ to } +3.6V$         |     | 0.7  |     | LSB/V |

| TIMING CHARACTERISTICS (No                              | ote 1)         |                                            |     |      |     |       |

| Quiet Time                                              | tQ             | (Note 2)                                   | 4   |      |     | ns    |

| CS Pulse Width                                          | t <sub>1</sub> | (Note 2)                                   | 10  |      |     | ns    |

| CS Fall to SCLK Setup                                   | t2             | (Note 2)                                   | 5   |      |     | ns    |

| CS Falling Until DOUT High-<br>Impedance Disabled       | t3             | (Note 2)                                   | 1   |      |     | ns    |

| Data Access Time After SCLK<br>Falling Edge             | t4             | Figure 2, V <sub>DD</sub> = +2.2V to +3.6V |     |      | 15  | ns    |

| SCLK Pulse Width Low                                    | t5             | Percentage of clock period (Note 2)        | 40  |      | 60  | %     |

| SCLK Pulse Width High                                   | t6             | Percentage of clock period (Note 2)        | 40  |      | 60  | %     |

| Data Hold Time From SCLK<br>Falling Edge                | t7             | Figure 3                                   | 5   |      |     | ns    |

| SCLK Falling Until DOUT High-<br>Impedance              | t8             | Figure 4 (Note 2)                          | 2.5 |      | 14  | ns    |

| Power-Up Time                                           |                | Conversion cycle (Note 2)                  |     |      | 1   | Cycle |

#### **ELECTRICAL CHARACTERISTICS (MAX11106)**

$(V_{DD} = 2.2V \text{ to } 3.6V, V_{REF} = V_{DD}, V_{OVDD} = V_{DD}, f_{SCLK} = 48MHz, 50\% \text{ duty cycle}, 3Msps; C_{DOUT} = 10pF, T_A = -40^{\circ}C \text{ to } +125^{\circ}C,$  unless otherwise noted. Typical values are at T\_A = +25^{\circ}C.)

| PARAMETER                             | SYMBOL | CONDITIONS                            | MIN | ТҮР   | MAX  | UNITS |  |  |  |

|---------------------------------------|--------|---------------------------------------|-----|-------|------|-------|--|--|--|

| DC ACCURACY                           |        |                                       |     |       |      |       |  |  |  |

| Resolution                            |        |                                       | 10  |       |      | Bits  |  |  |  |

| Integral Nonlinearity                 | INL    |                                       |     |       | ±0.4 | LSB   |  |  |  |

| Differential Nonlinearity             | DNL    | No missing codes                      |     |       | ±0.4 | LSB   |  |  |  |

| Offset Error                          | OE     |                                       |     | ±0.5  | ±1   | LSB   |  |  |  |

| Gain Error                            | GE     | Excluding offset and reference errors |     | 0     | ±1   | LSB   |  |  |  |

| Total Unadjusted Error                | TUE    |                                       |     | ±0.5  |      | LSB   |  |  |  |

| Channel-to-Channel Offset<br>Matching |        |                                       |     | ±0.05 |      | LSB   |  |  |  |

| Channel-to-Channel Gain<br>Matching   |        |                                       |     | ±0.05 |      | LSB   |  |  |  |

| DYNAMIC PERFORMANCE                   |        |                                       |     |       |      |       |  |  |  |

| Signal-to-Noise and Distortion        | SINAD  | f <sub>AIN</sub> = 1MHz               | 61  | 61.8  |      | dB    |  |  |  |

| Signal-to-Noise Ratio                 | SNR    | fain_ = 1MHz                          | 61  | 61.8  |      | dB    |  |  |  |

| Total Harmonic Distortion             | THD    | $f_{AIN} = 1MHz$                      |     | -83   | -74  | dB    |  |  |  |

| Spurious-Free Dynamic Range           | SFDR   | fain_ = 1MHz                          | 75  |       |      | dB    |  |  |  |

## 2Msps/3Msps, Low-Power, Serial 12-/10-/8-Bit ADCs

### **ELECTRICAL CHARACTERISTICS (MAX11106) (continued)**

$(V_{DD} = 2.2V \text{ to } 3.6V, V_{REF} = V_{DD}, V_{OVDD} = V_{DD}, f_{SCLK} = 48MHz, 50\% \text{ duty cycle}, 3Msps; C_{DOUT} = 10pF, T_A = -40^{\circ}C \text{ to } +125^{\circ}C,$  unless otherwise noted. Typical values are at T\_A = +25^{\circ}C.)

| PARAMETER                            | SYMBOL | CONDITIONS                          | MIN             | TYP                         | MAX                       | UNITS |

|--------------------------------------|--------|-------------------------------------|-----------------|-----------------------------|---------------------------|-------|

| Intermodulation Distortion           | IMD    | $f_1 = 1.0003MHz, f_2 = 0.99955MHz$ |                 | -82                         |                           | dB    |

| Full-Power Bandwidth                 |        | -3dB point                          |                 | 40                          |                           | MHz   |

| Full-Linear Bandwidth                |        | SINAD > 60dB                        |                 | 2.5                         |                           | MHz   |

| Small-Signal Bandwidth               |        |                                     |                 | 45                          |                           | MHz   |

| Crosstalk                            |        |                                     |                 | -90                         |                           | dB    |

| CONVERSION RATE                      |        |                                     |                 |                             |                           | -     |

| Throughput                           |        |                                     | 0.03            |                             | 3                         | Msps  |

| Conversion Time                      |        |                                     | 260             |                             |                           | ns    |

| Acquisition Time                     | tacq   |                                     | 52              |                             |                           | ns    |

| Aperture Delay                       |        | From CS falling edge                |                 | 4                           |                           | ns    |

| Aperture Jitter                      |        |                                     |                 | 15                          |                           | ps    |

| Serial-Clock Frequency               | fCLK   |                                     | 0.48            |                             | 48                        | MHz   |

| ANALOG INPUT (AIN1, AIN2)            |        |                                     | •               |                             |                           |       |

| Input Voltage Range                  | Vain_  |                                     | 0               |                             | VREF                      | V     |

| Input Leakage Current                | lila   |                                     |                 | 0.002                       | ±1                        | μA    |

|                                      |        | Track                               |                 | 20                          |                           |       |

| Input Capacitance                    | Cain_  | Hold                                |                 | 4                           |                           | pF    |

| EXTERNAL REFERENCE INPUT             | (REF)  |                                     | I               |                             |                           |       |

| Reference Input-Voltage Range        | VREF   |                                     | 1               |                             | V <sub>DD</sub> +<br>0.05 | V     |

| Reference Input Leakage<br>Current   | lilr   | Conversion stopped                  |                 | 0.005                       | ±1                        | μA    |

| Reference Input Capacitance          | CREF   |                                     |                 | 5                           |                           | рF    |

| DIGITAL INPUTS (SCLK, CS, CH         |        |                                     |                 |                             |                           | · '   |

| Digital Input-High Voltage           | VIH    |                                     | 0.75 x<br>Vovdd |                             |                           | V     |

| Digital Input-Low Voltage            | VIL    |                                     |                 |                             | 0.25 x<br>Vovdd           | V     |

| Digital Input Hysteresis             | VHYST  |                                     |                 | 0.15 x<br>V <sub>OVDD</sub> |                           | V     |

| Digital Input Leakage Current        | ΙL     | Inputs at GND or V <sub>DD</sub>    |                 | 0.001                       | ±1                        | μA    |

| Digital Input Capacitance            | CIN    |                                     |                 | 2                           |                           | рF    |

| DIGITAL OUTPUT (DOUT)                |        |                                     |                 |                             |                           |       |

| Output-High Voltage                  | Voн    | ISOURCE = 200µA                     | 0.85 x<br>Vovdd |                             |                           | V     |

| Output-Low Voltage                   | VOL    | I <sub>SINK</sub> = 200µA           |                 |                             | 0.15 x<br>Vovdd           | V     |

| High-Impedance Leakage<br>Current    | IOL    |                                     |                 |                             | ±1.0                      | μA    |

| High-Impedance Output<br>Capacitance | Соит   |                                     |                 | 4                           |                           | pF    |

# 2Msps/3Msps, Low-Power, Serial 12-/10-/8-Bit ADCs

### **ELECTRICAL CHARACTERISTICS (MAX11106) (continued)**

$(V_{DD} = 2.2V \text{ to } 3.6V, V_{REF} = V_{DD}, V_{OVDD} = V_{DD}, f_{SCLK} = 48MHz, 50\% \text{ duty cycle, 3Msps; } C_{DOUT} = 10pF, T_{A} = -40^{\circ}C \text{ to } +125^{\circ}C, \text{ unless otherwise noted. Typical values are at } T_{A} = +25^{\circ}C.)$

| PARAMETER                                               | SYMBOL | CONDITIONS                                  | MIN | ТҮР  | MAX             | UNITS |

|---------------------------------------------------------|--------|---------------------------------------------|-----|------|-----------------|-------|

| POWER SUPPLY                                            |        | ·                                           |     |      |                 |       |

| Positive Supply Voltage                                 | Vdd    |                                             | 2.2 |      | 3.6             | V     |

| Digital I/O Supply Voltage                              | Vovdd  |                                             | 1.5 |      | V <sub>DD</sub> | V     |

| Positive Supply Current (Full-                          | Ivdd   | VAIN_ = VGND                                |     |      | 3.3             | mA    |

| Power Mode)                                             | Iovdd  | VAIN_ = VGND                                |     |      | 0.33            |       |

| Positive Supply Current (Full-<br>Power Mode), No Clock | IVDD   |                                             |     | 1.98 |                 | mA    |

| Power-Down Current                                      | IPD    | Leakage only                                |     | 1.3  | 10              | μA    |

| Line Rejection                                          |        | $V_{DD}$ = +2.2V to +3.6V, $V_{REF}$ = 2.2V |     | 0.17 |                 | LSB/V |

| TIMING CHARACTERISTICS (N                               | ote 1) |                                             |     |      |                 |       |

| Quiet Time                                              | tQ     | (Note 2)                                    | 4   |      |                 | ns    |

| CS Pulse Width                                          | t1     | (Note 2)                                    | 10  |      |                 | ns    |

| CS Fall to SCLK Setup                                   | t2     | (Note 2)                                    | 5   |      |                 | ns    |

| CS Falling Until DOUT High-<br>Impedance Disabled       | t3     | (Note 2)                                    | 1   |      |                 | ns    |

| Data Access Time After SCLK                             |        | $V_{OVDD} = 2.2V - 3.6V$                    |     |      | 15              |       |

| Falling Edge (Figure 2)                                 | t4     | VOVDD = 1.5V - 2.2V                         |     |      | 16.5            | ns    |

| SCLK Pulse Width Low                                    | t5     | Percentage of clock period (Note 2)         | 40  |      | 60              | %     |

| SCLK Pulse Width High                                   | t6     | Percentage of clock period (Note 2)         | 40  |      | 60              | %     |

| Data Hold Time From SCLK<br>Falling Edge                | t7     | Figure 3                                    | 5   |      |                 | ns    |

| SCLK Falling Until DOUT High-<br>Impedance              | t8     | Figure 4 (Note 2)                           | 2.5 |      | 14              | ns    |

| Power-Up Time                                           |        | Conversion cycle (Note 2)                   |     |      | 1               | Cycle |

### **ELECTRICAL CHARACTERISTICS (MAX11110/MAX11117)**

$(V_{DD} = 2.2V \text{ to } 3.6V. \text{ MAX11110: } f_{SCLK} = 32MHz$ , 50% duty cycle, 2Msps. MAX11117:  $f_{SCLK} = 48MHz$ , 50% duty cycle, 3Msps. C<sub>DOUT</sub> = 10pF, T<sub>A</sub> = -40°C to +125°C, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.)

| PARAMETER                 | SYMBOL | CONDITIONS                                         | MIN | ТҮР   | МАХ   | UNITS |

|---------------------------|--------|----------------------------------------------------|-----|-------|-------|-------|

| DC ACCURACY               |        |                                                    |     |       |       |       |

| Resolution                |        |                                                    | 10  |       |       | Bits  |

| Integral Nonlinearity     | INL    |                                                    |     |       | ±1    | LSB   |

| Differential Nonlinearity | DNL    | No missing codes                                   |     |       | ±1    | LSB   |

| 0                         |        | MAX11117                                           |     | ±0.5  | ±1.65 |       |

| Offset Error              | OE     | MAX11110                                           |     | ±0.3  | ±1.2  | LSB   |

| Gain Error                |        | Excluding offset and reference errors,<br>MAX11117 |     | ±0.7  | ±1.4  |       |

| Gain Error                | GE     | Excluding offset and reference errors, MAX11110    |     | ±0.15 | ±1    | LSB   |

| Total Unadjusted Error    | TUE    |                                                    |     | ±1    |       | LSB   |

## 2Msps/3Msps, Low-Power, Serial 12-/10-/8-Bit ADCs

#### ELECTRICAL CHARACTERISTICS (MAX11110/MAX11117) (continued)

(VDD = 2.2V to 3.6V. MAX11110:  $f_{SCLK}$  = 32MHz, 50% duty cycle, 2Msps. MAX11117:  $f_{SCLK}$  = 48MHz, 50% duty cycle, 3Msps. CDOUT = 10pF, T<sub>A</sub> = -40°C to +125°C, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.)

| PARAMETER                      | SYMBOL       | CONDITIONS                                                                                                                                                                                                         | MIN           | ТҮР           | МАХ             | UNITS |

|--------------------------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|---------------|-----------------|-------|

| DYNAMIC PERFORMANCE (MA        | X11117: fain | = 1MHz, MAX11110: f <sub>AIN</sub> = 0.5MHz)                                                                                                                                                                       | •             |               |                 |       |

|                                |              | MAX11117                                                                                                                                                                                                           | 59            | 61.5          |                 |       |

| Signal-to-Noise and Distortion | SINAD        | MAX11110                                                                                                                                                                                                           | 60.5          | 61.5          |                 | dB    |

|                                | 0115         | MAX11117                                                                                                                                                                                                           | 59            | 61.5          |                 | 15    |

| Signal-to-Noise Ratio          | SNR          | MAX11110                                                                                                                                                                                                           | 60.5          | 61.5          |                 | dB    |

| T                              | TUD          | MAX11117                                                                                                                                                                                                           |               | -85           | -74             |       |

| Total Harmonic Distortion      | THD          | MAX11110                                                                                                                                                                                                           |               | -85           | -73             | dB    |

|                                | 0500         | MAX11117                                                                                                                                                                                                           | 75            |               |                 | 15    |

| Spurious-Free Dynamic Range    | SFDR         | MAX11110                                                                                                                                                                                                           | 75            |               |                 | dB    |

| Intermodulation Distortion     | IMD          | $\begin{array}{l} \mbox{MAXX11117:} \ \mbox{f}_1 = 1.0003\mbox{MHz}, \ \mbox{f}_2 = 0.99955\mbox{MHz} \\ \mbox{MAX11110:} \ \mbox{f}_1 = 500.15\mbox{Hz}, \ \mbox{f}_2 = 499.56\mbox{Hz} \\ \mbox{Hz} \end{array}$ |               | -82           |                 | dB    |

| Full-Power Bandwidth           |              | -3dB point                                                                                                                                                                                                         |               | 40            |                 | MHz   |

| Full-Linear Bandwidth          |              | SINAD > 60dB                                                                                                                                                                                                       |               | 2.5           |                 | MHz   |

| Small-Signal Bandwidth         |              |                                                                                                                                                                                                                    |               | 45            |                 | MHz   |

| CONVERSION RATE                |              |                                                                                                                                                                                                                    |               |               |                 |       |

| <b>-</b>                       |              | MAX11117                                                                                                                                                                                                           | 0.03          |               | 3               |       |

| Throughput                     |              | MAX11110                                                                                                                                                                                                           | 0.02          |               | 2               | Msps  |

|                                |              | MAX11117                                                                                                                                                                                                           | 260           |               |                 |       |

| Conversion Time                |              | MAX11110                                                                                                                                                                                                           | 391           |               |                 | ns    |

| Acquisition Time               | tacq         |                                                                                                                                                                                                                    | 52            |               |                 | ns    |

| Aperture Delay                 |              | From CS falling edge                                                                                                                                                                                               |               | 4             |                 | ns    |

| Aperture Jitter                |              |                                                                                                                                                                                                                    |               | 15            |                 | ps    |

|                                |              | MAX11117                                                                                                                                                                                                           | 0.48          |               | 48              |       |

| Serial Clock Frequency         | fCLK         | MAX11110                                                                                                                                                                                                           | 0.32          |               | 32              | MHz   |

| ANALOG INPUT (AIN)             |              |                                                                                                                                                                                                                    |               |               |                 |       |

| Input Voltage Range            | VAIN         |                                                                                                                                                                                                                    | 0             |               | V <sub>DD</sub> | V     |

| Input Leakage Current          | lila         |                                                                                                                                                                                                                    |               | 0.002         | ±1              | μA    |

|                                | 0            | Track                                                                                                                                                                                                              |               | 20            |                 |       |

| Input Capacitance              | CAIN         | Hold                                                                                                                                                                                                               |               | 4             |                 | pF    |

| DIGITAL INPUTS (SCLK, CS, C    | HSEL)        |                                                                                                                                                                                                                    |               |               |                 |       |

| Digital Input-High Voltage     | VIH          |                                                                                                                                                                                                                    | 0.75 x<br>VDD |               |                 | V     |

| Digital Input-Low Voltage      | VIL          |                                                                                                                                                                                                                    |               |               | 0.25 x<br>VDD   | V     |

| Digital Input Hysteresis       | VHYST        |                                                                                                                                                                                                                    |               | 0.15 x<br>Vdd |                 | V     |

| Digital Input Leakage Current  | IIL          | Inputs at GND or V <sub>DD</sub>                                                                                                                                                                                   |               | 0.001         | ±1              | μA    |

| Digital Input Capacitance      | CIN          |                                                                                                                                                                                                                    |               | 2             |                 | pF    |

## 2Msps/3Msps, Low-Power, Serial 12-/10-/8-Bit ADCs

### ELECTRICAL CHARACTERISTICS (MAX11110/MAX11117) (continued)

$(V_{DD} = 2.2V \text{ to } 3.6V. \text{ MAX11110: } f_{SCLK} = 32MHz$ , 50% duty cycle, 2Msps. MAX11117:  $f_{SCLK} = 48MHz$ , 50% duty cycle, 3Msps. CDOUT = 10pF, TA = -40°C to +125°C, unless otherwise noted. Typical values are at TA = +25°C.)

| PARAMETER                                              | SYMBOL          | CONDITIONS                                                                         | MIN                       | ТҮР          | МАХ                       | UNITS |

|--------------------------------------------------------|-----------------|------------------------------------------------------------------------------------|---------------------------|--------------|---------------------------|-------|

| DIGITAL OUTPUT (DOUT)                                  |                 |                                                                                    |                           |              |                           |       |

| Output-High Voltage                                    | Vон             | ISOURCE = 200µA                                                                    | 0.85 x<br>V <sub>DD</sub> |              |                           | V     |

| Output-Low Voltage                                     | Vol             | ISINK = 200µA                                                                      |                           |              | 0.15 x<br>V <sub>DD</sub> | V     |

| High-Impedance Leakage<br>Current                      | IOL             |                                                                                    |                           |              | ±1.0                      | μA    |

| High-Impedance Output<br>Capacitance                   | Соит            |                                                                                    |                           | 4            |                           | pF    |

| POWER SUPPLY                                           | ·               |                                                                                    |                           |              |                           |       |

| Positive Supply Voltage                                | V <sub>DD</sub> |                                                                                    | 2.2                       |              | 3.6                       | V     |

| Positive Supply Current<br>(Full-Power Mode)           | IVDD            | MAX11117, VAIN = V <sub>GND</sub><br>MAX11110, V <sub>AIN</sub> = V <sub>GND</sub> |                           |              | 3.55<br>2.6               | mA    |

| Positive Supply Current<br>(Full-Power Mode), No Clock | IVDD            | MAX11117<br>MAX11110                                                               |                           | 1.98<br>1.48 |                           | mA    |

| Power-Down Current                                     | IPD             | Leakage only                                                                       |                           | 1.3          | 10                        | μA    |

| Line Rejection                                         |                 | $V_{DD} = +2.2V$ to $+3.6V$                                                        |                           | 0.17         |                           | LSB/V |

| TIMING CHARACTERISTICS (No                             | ote 1)          |                                                                                    |                           |              |                           |       |

| Quiet Time                                             | tQ              | (Note 2)                                                                           | 4                         |              |                           | ns    |

| CS Pulse Width                                         | t <sub>1</sub>  | (Note 2)                                                                           | 10                        |              |                           | ns    |

| CS Fall to SCLK Setup                                  | t2              | (Note 2)                                                                           | 5                         |              |                           | ns    |

| CS Falling Until DOUT High-<br>Impedance Disabled      | t3              | (Note 2)                                                                           | 1                         |              |                           | ns    |

| Data Access Time After SCLK<br>Falling Edge            | t4              | Figure 2, $V_{DD}$ = +2.2V to +3.6V                                                |                           |              | 15                        | ns    |

| SCLK Pulse Width Low                                   | t5              | Percentage of clock period (Note 2)                                                | 40                        |              | 60                        | %     |

| SCLK Pulse Width High                                  | t6              | Percentage of clock period (Note 2)                                                | 40                        |              | 60                        | %     |

| Data Hold Time From SCLK<br>Falling Edge               | t7              | Figure 3                                                                           | 5                         |              |                           | ns    |

| SCLK Falling Until DOUT High-<br>Impedance             | t8              | Figure 4 (Note 2)                                                                  | 2.5                       |              | 14                        | ns    |

| Power-Up Time                                          |                 | Conversion cycle (Note 2)                                                          |                           |              | 1                         | Cycle |

## 2Msps/3Msps, Low-Power, Serial 12-/10-/8-Bit ADCs

### **ELECTRICAL CHARACTERISTICS (MAX11111)**

$(V_{DD} = 2.2V \text{ to } 3.6V, V_{REF} = V_{DD}, V_{OVDD} = V_{DD}, f_{SCLK} = 48MHz, 50\% \text{ duty cycle}, 3Msps, C_{DOUT} = 10pF, T_A = -40^{\circ}C \text{ to } +125^{\circ}C,$  unless otherwise noted. Typical values are at T\_A = +25^{\circ}C.)

| PARAMETER                             | SYMBOL           | CONDITIONS                                              | MIN  | ТҮР   | MAX                       | UNITS |

|---------------------------------------|------------------|---------------------------------------------------------|------|-------|---------------------------|-------|

| DC ACCURACY                           |                  |                                                         |      |       |                           |       |

| Resolution                            |                  |                                                         | 8    |       |                           | Bits  |

| Integral Nonlinearity                 | INL              |                                                         |      |       | ±0.15                     | LSB   |

| Differential Nonlinearity             | DNL              | No missing codes                                        |      |       | ±0.15                     | LSB   |

| Offset Error                          | OE               |                                                         |      | 0.45  | ±0.7                      | LSB   |

| Gain Error                            | GE               | Excluding offset and reference errors                   |      | 0     | ±0.2                      | LSB   |

| Total Unadjusted Error                | TUE              |                                                         |      | 0.5   |                           | LSB   |

| Channel-to-Channel Offset<br>Matching |                  |                                                         |      | 0.01  |                           | LSB   |

| Channel-to-Channel Gain<br>Matching   |                  |                                                         |      | 0.01  |                           | LSB   |

| DYNAMIC PERFORMANCE                   | 1                |                                                         | 1    |       |                           | 1     |

| Signal-to-Noise and Distortion        | SINAD            | fain_ = 1MHz                                            | 49   | 49.8  |                           | dB    |

| Signal-to-Noise Ratio                 | SNR              | $f_{AIN} = 1MHz$                                        | 49   | 49.8  |                           | dB    |

| Total Harmonic Distortion             | THD              | $f_{AIN} = 1MHz$                                        |      | -75   | -67                       | dB    |

| Spurious-Free Dynamic Range           | SFDR             | $f_{AIN} = 1MHz$                                        | 63   | 67    |                           | dB    |

| Intermodulation Distortion            | IMD              | f <sub>1</sub> = 1.0003MHz, f <sub>2</sub> = 0.99955MHz |      | -65   |                           | dB    |

| Full-Power Bandwidth                  |                  | -3dB point                                              |      | 40    |                           | MHz   |

| Full-Linear Bandwidth                 |                  | SINAD > 49dB                                            |      | 2.5   |                           | MHz   |

| Small-Signal Bandwidth                |                  |                                                         |      | 45    |                           | MHz   |

| Crosstalk                             |                  |                                                         |      | -90   |                           | dB    |

| CONVERSION RATE                       |                  |                                                         |      |       |                           |       |

| Throughput                            |                  |                                                         | 0.03 |       | 3                         | Msps  |

| Conversion Time                       |                  |                                                         | 260  |       |                           | ns    |

| Acquisition Time                      | tacq             |                                                         | 52   |       |                           | ns    |

| Aperture Delay                        |                  | From CS falling edge                                    |      | 4     |                           | ns    |

| Aperture Jitter                       |                  |                                                         |      | 15    |                           | ps    |

| Serial-Clock Frequency                | fCLK             |                                                         | 0.48 |       | 48                        | MHz   |

| ANALOG INPUT (AIN1, AIN2)             |                  |                                                         |      |       |                           |       |

| Input Voltage Range                   | Vain_            |                                                         | 0    |       | VREF                      | V     |

| Input Leakage Current                 | lila             |                                                         |      | 0.002 | ±1                        | μA    |

| Input Capacitance                     | Com              | Track                                                   |      | 20    |                           | рF    |

|                                       | CAIN_            | Hold                                                    |      | 4     | -                         | рг    |

| EXTERNAL REFERENCE INPUT              | (REF)            | 1                                                       |      |       | -                         |       |

| Reference Input Voltage Range         | VREF             |                                                         | 1    |       | V <sub>DD</sub> +<br>0.05 | V     |

| Reference Input Leakage Current       | l <sub>ILR</sub> | Conversion stopped                                      |      | 0.005 | ±1                        | μA    |

| Reference Input Capacitance           | CREF             |                                                         |      | 5     |                           | рF    |

# 2Msps/3Msps, Low-Power, Serial 12-/10-/8-Bit ADCs

### **ELECTRICAL CHARACTERISTICS (MAX11111) (continued)**

$(V_{DD} = 2.2V \text{ to } 3.6V, V_{REF} = V_{DD}, V_{OVDD} = V_{DD}, f_{SCLK} = 48MHz, 50\% \text{ duty cycle}, 3Msps, C_{DOUT} = 10pF, T_A = -40^{\circ}C \text{ to } +125^{\circ}C,$  unless otherwise noted. Typical values are at T\_A = +25^{\circ}C.)

| PARAMETER                                              | SYMBOL | CONDITIONS                                                | MIN             | ТҮР             | MAX             | UNITS |

|--------------------------------------------------------|--------|-----------------------------------------------------------|-----------------|-----------------|-----------------|-------|

| DIGITAL INPUTS (SCLK, CS)                              |        |                                                           |                 |                 |                 |       |

| Digital Input High Voltage                             | VIH    |                                                           | 0.75 x<br>Vovdd |                 |                 | V     |

| Digital Input Low Voltage                              | VIL    |                                                           |                 |                 | 0.25 x<br>Vovdd | V     |

| Digital Input Hysteresis                               | VHYST  |                                                           |                 | 0.15 x<br>Vovdd |                 | V     |

| Digital Input Leakage Current                          | IIL    | Inputs at GND or V <sub>DD</sub>                          |                 | 0.001           | ±1              | μA    |

| Digital Input Capacitance                              | CIN    |                                                           |                 | 2               |                 | рF    |

| DIGITAL OUTPUT (DOUT)                                  |        |                                                           |                 |                 |                 |       |

| Output High Voltage                                    | Vон    | ISOURCE = 200µA (Note 2)                                  | 0.85 x<br>Vovdd |                 |                 | V     |

| Output Low Voltage                                     | Vol    | I <sub>SINK</sub> = 200µA (Note 2)                        |                 |                 | 0.15 x<br>Vovdd | V     |

| High-Impedance Leakage<br>Current                      | IOL    |                                                           |                 |                 | ±1.0            | μA    |

| High-Impedance Output<br>Capacitance                   | Cout   |                                                           |                 | 4               |                 | pF    |

| POWER SUPPLY                                           |        |                                                           |                 |                 |                 |       |

| Positive Supply Voltage                                | VDD    |                                                           | 2.2             |                 | 3.6             | V     |

| Digital I/O Supply Voltage                             | Vovdd  |                                                           | 1.5             |                 | VDD             | V     |

| Positive Supply Current                                | IVDD   | VAIN_= VGND                                               |                 |                 | 3.3             | mA    |

| (Full-Power Mode)                                      | Iovdd  | VAIN_ = VGND                                              |                 |                 | 0.33            | MA    |

| Positive Supply Current<br>(Full-Power Mode), No Clock | IVDD   |                                                           |                 | 1.98            |                 | mA    |

| Power-Down Current                                     | IPD    | Leakage only                                              |                 | 1.3             | 10              | μA    |

| Line Rejection                                         |        | V <sub>DD</sub> = +2.2V to +3.6V, V <sub>REF</sub> = 2.2V |                 | 0.17            |                 | LSB/V |

| TIMING CHARACTERISTICS (No                             | ote 1) |                                                           |                 |                 |                 |       |

| Quiet Time                                             | tQ     | (Note 2)                                                  | 4               |                 |                 | ns    |

| CS Pulse Width                                         | t1     | (Note 2)                                                  | 10              |                 |                 | ns    |

| CS Fall to SCLK Setup                                  | t2     | (Note 2)                                                  | 5               |                 |                 | ns    |

| CS Falling Until DOUT High-<br>Impedance Disabled      | t3     | (Note 2)                                                  | 1               |                 |                 | ns    |

| Data Access Time After SCLK                            |        | VOVDD = 2.2V - 3.6V                                       |                 |                 | 15              |       |

| Falling Edge (Figure 2)                                | t4     | $V_{OVDD} = 1.5V - 2.2V$                                  |                 |                 | 16.5            | ns    |

| SCLK Pulse Width Low                                   | t5     | Percentage of clock period (Note 2)                       | 40              |                 | 60              | %     |

| SCLK Pulse Width High                                  | t6     | Percentage of clock period (Note 2)                       | 40              |                 | 60              | %     |

| Data Hold Time From SCLK<br>Falling Edge               | t7     | Figure 3                                                  | 5               |                 |                 | ns    |

| SCLK Falling Until DOUT High-<br>Impedance             | t8     | Figure 4 (Note 2)                                         | 2.5             |                 | 14              | ns    |

| Power-Up Time                                          |        | Conversion cycle (Note 2)                                 |                 |                 | 1               | Cycle |

## 2Msps/3Msps, Low-Power, Serial 12-/10-/8-Bit ADCs

#### **ELECTRICAL CHARACTERISTICS (MAX11115/MAX11116)**

$(V_{DD} = 2.2V \text{ to } 3.6V. \text{ MAX11115: } f_{SCLK} = 32MHz, 50\% \text{ duty cycle, 2Msps. MAX11116: } f_{SCLK} = 48MHz, 50\% \text{ duty cycle, 3Msps.}$  $C_{DOUT} = 10pF, T_A = -40^{\circ}C \text{ to } +125^{\circ}C, \text{ unless otherwise noted. Typical values are at T_A = +25^{\circ}C.)$