## Stand-Alone ModelGauge m5 Fuel Gauge with SHA-256 Authentication

### **General Description**

The MAX1720x/MAX1721x are ultra-low power stand-alone fuel gauge ICs that implement the Maxim ModelGauge<sup>™</sup> m5 algorithm without requiring host interaction for configuration. This feature makes the MAX1720x/MAX1721x excellent pack-side fuel gauges. The MAX17201/MAX17211 monitor a single cell pack. The MAX17205/MAX17215 monitor and balance a 2S or 3S pack or monitor a multiple-series cell pack.

To prevent battery pack cloning, the ICs integrate SHA-256 authentication with a 160-bit secret key. Each IC incorporates a unique 64-bit ID.

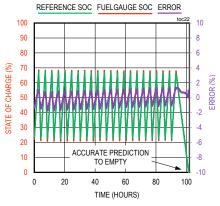

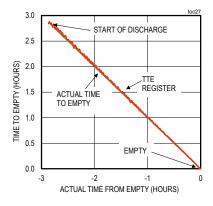

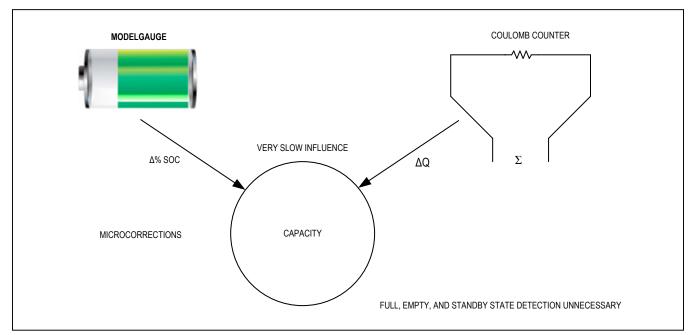

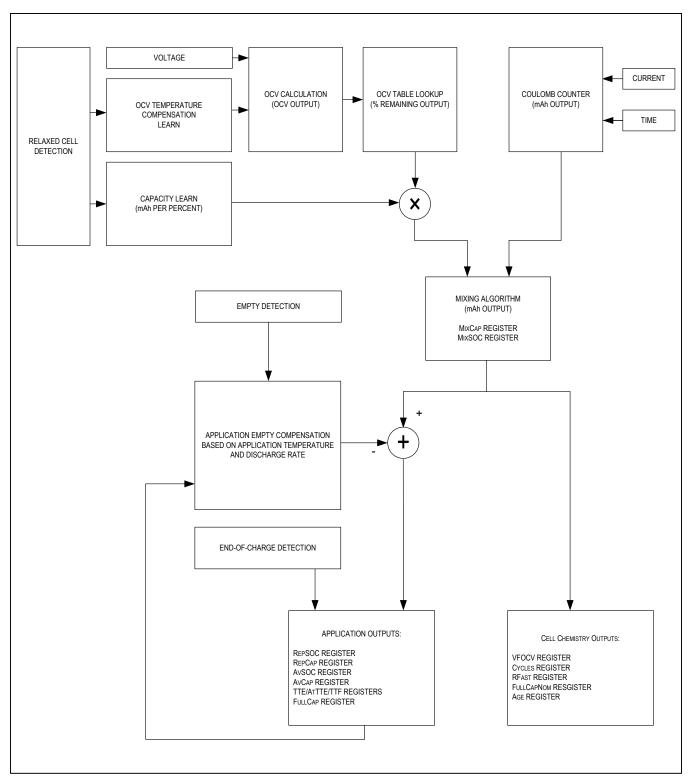

The ModelGauge<sup>™</sup> m5 algorithm combines the short-term accuracy and linearity of a coulomb counter with the long-term stability of a voltage-based fuel gauge, along with temperature compensation to provide industry-leading fuel gauge accuracy. The IC automatically compensates for cell aging, temperature, and discharge rate, and provides accurate state of charge (SOC) in milliampere-hours (mAh) or percentage (%) over a wide range of operating conditions. As the battery approaches the critical region near empty, the ModelGauge m5 algorithm invokes a special error correction mechanism that eliminates any error. The ICs provide accurate estimation of time-to-empty and time-to-full, Cycle+<sup>™</sup> age forecast, and three methods for reporting the age of the battery: reduction in capacity, increase in battery resistance, and cycle odometer.

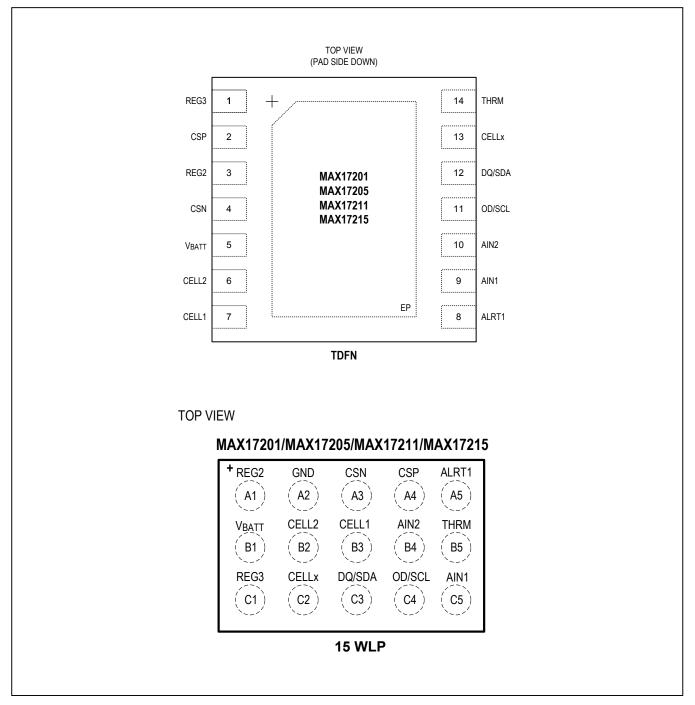

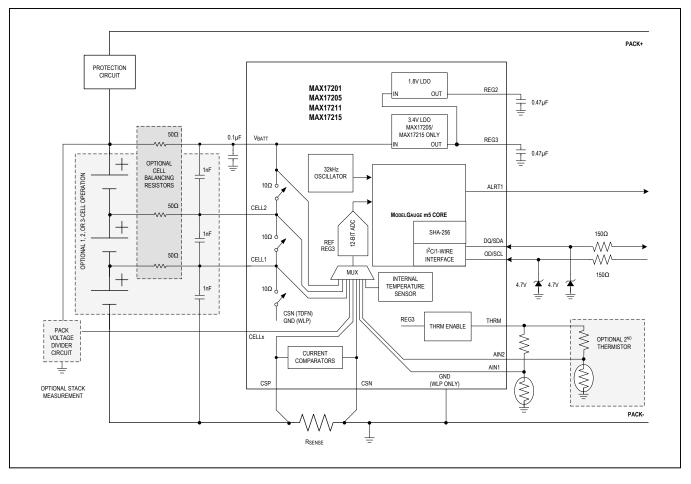

The ICs provide precision measurements of current, voltage, and temperature. Temperature of the battery pack is measured using an internal temperature measurement and up to two external thermistors supported by ratiometric measurements on auxiliary inputs. A Maxim 1-Wire<sup>®</sup> (MAX17211/MAX17215) or 2-wire I<sup>2</sup>C (MAX17201/MAX17205) interface provides access to data and control registers. The ICs are available in lead-free, 3mm x 3mm, 14-pin TDFN and 1.6mm x 2.4mm 15-bump WLP packages.

### **Applications**

- Smartphones and Tablets

- Portable Game Players

- e-Readers

- Digital Still and Video Cameras

- Handheld Computers and Terminals

- Portable Medical Equipment

- Handheld Radios

### **Benefits and Features**

- ModelGauge m5 Algorithm

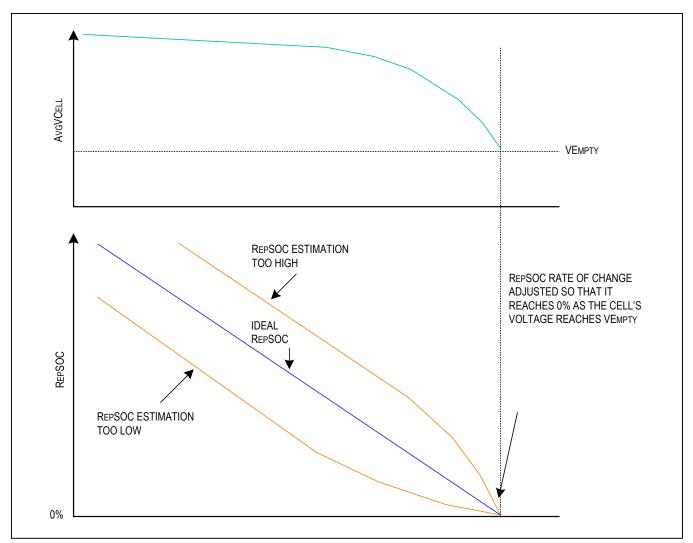

- · Eliminates Error when Approaching Empty Voltage

- · Eliminates Coulomb-Counter Drift

- Current, Temperature, and Age Compensated

- · Does Not Require Empty, Full, or Idle States

- No Characterization Required for EZ Performance (See the ModelGauge m5 EZ Performance Section)

- Cycle+ Age Forecasting Observes Lifespan

- Nonvolatile Memory for Stand-Alone Operation

- · Learned Parameters and History Logging

- Up to 75 Words Available for User Data

- Precision Measurement System

- No Calibration Required

- Time-to-Empty and Time-to-Full Estimation

- Temperature Measurement

- Die Temperature

- Up to Two External Thermistors

- Multiple Series Cell Pack Operation

- Low Quiescent Current

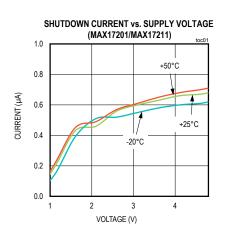

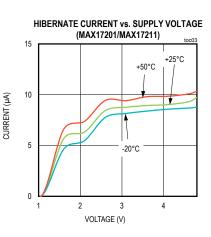

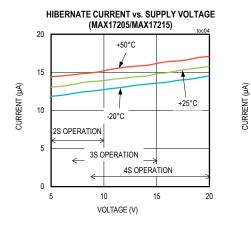

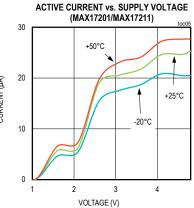

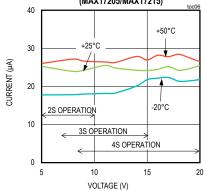

- MAX172x1: 18µA Active, 9µA Hibernate

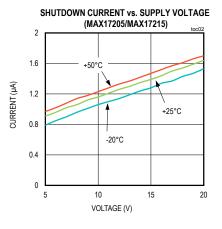

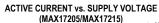

- MAX172x5: 25µA Active, 12µA Hibernate

- Alert Indicator for Voltage, SOC, Temperature, Current, and 1% SOC Change

- High-Speed Overcurrent Comparators

- Predicts Remaining Capacity Under Theoretical Load

- SHA-256 Authentication

- Maxim 1-Wire or 2-Wire (I<sup>2</sup>C) Interface

- SBS 1.1 Compatible Register Set

Ordering Information appears at end of data sheet.

ModelGauge and Cycle+ are trademarks and 1-Wire is a registered trademark of Maxim Integrated Products, Inc.

# Stand-Alone ModelGauge m5 Fuel Gauge with SHA-256 Authentication

### Simplified Block Diagram

# Stand-Alone ModelGauge m5 Fuel Gauge with SHA-256 Authentication

| General Description                                                | 1  |

|--------------------------------------------------------------------|----|

| Simplified Block Diagram.                                          | 2  |

| Absolute Maximum Ratings (TDFN)                                    |    |

| Absolute Maximum Ratings (WLP)                                     |    |

| Package Information                                                | 13 |

| Electrical Characteristics                                         |    |

| Typical Operating Characteristics                                  |    |

| Pin Configurations                                                 |    |

| Pin/Bump Description.                                              |    |

| Functional Diagram                                                 |    |

| Detailed Description.                                              |    |

| Register Description Conventions.                                  |    |

| Standard Register Formats                                          |    |

| Device Reset                                                       |    |

| Nonvolatile Backup and Initial Value                               |    |

| Register Naming Conventions                                        |    |

| Alternate Initial and Factory Default Values                       |    |

| Typical Operating Circuits                                         |    |

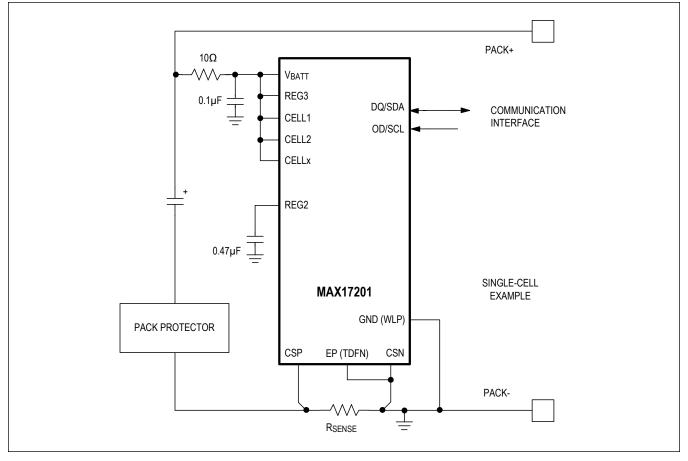

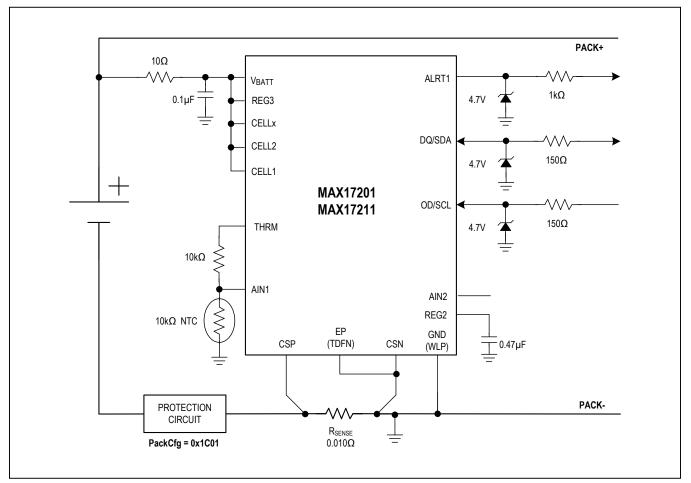

| Single-Cell Typical Operating Circuit (MAX17201/MAX17211 Only)     |    |

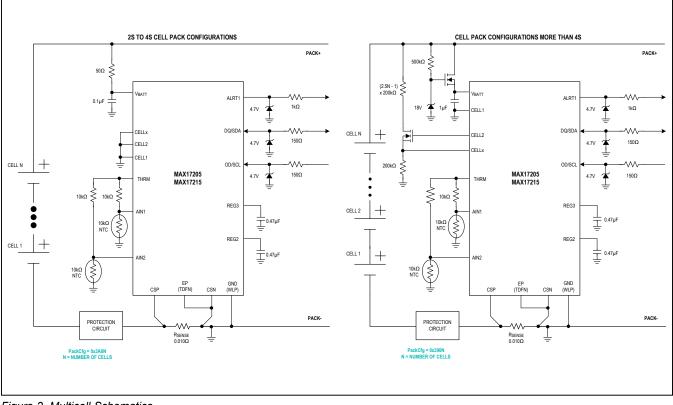

| Multicell Typical Operating Circuits (MAX17205/MAX17215 Only)      |    |

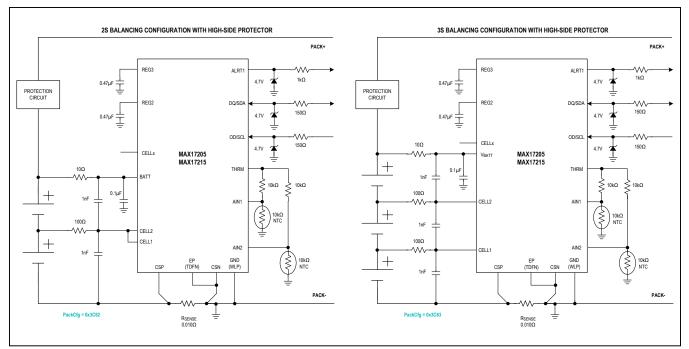

| Cell Balancing Typical Operating Circuits (MAX17205/MAX17215 Only) |    |

| ModelGauge m5 Algorithm                                            |    |

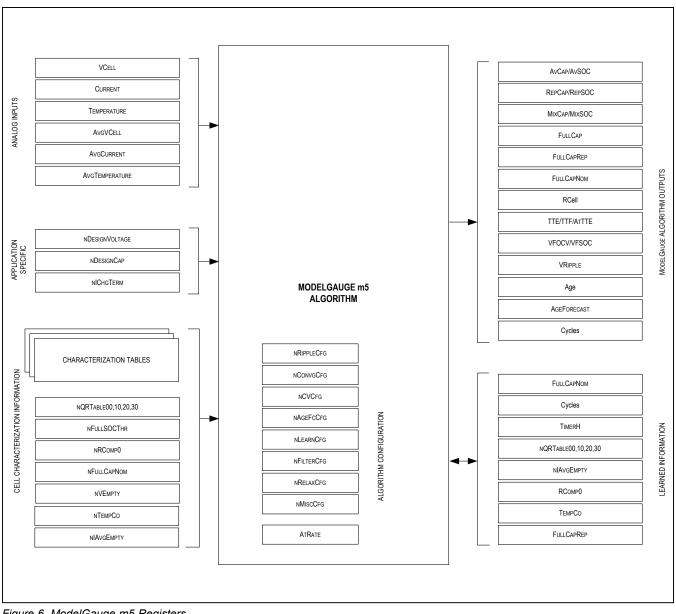

| ModelGauge m5 Registers                                            |    |

| ModelGauge m5 Algorithm Output Registers                           |    |

| RepCap Register (005h)                                             |    |

| RepSOC Register (006h)                                             |    |

| FullCapRep Register (035h)                                         |    |

| TTE Register (011h)                                                |    |

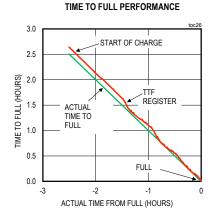

| TTF Register (020h)                                                |    |

| Age Register (007h)                                                |    |

| Cycles Register (017h)                                             |    |

| TimerH Register (0BEh)                                             |    |

| FullCap Register (010h)                                            |    |

| nFullCapNom Register (1A5h)                                        |    |

| RCell Register (014h)                                              |    |

| VRipple Register (0BCh)                                            |    |

| nSOC Register (1AEh)                                               |    |

| nVoltTemp Register (1AAh)                                          |    |

### **TABLE OF CONTENTS**

| TABLE OF CONTENTS (CONTINUED)                              |

|------------------------------------------------------------|

| ModelGauge m5 EZ Performance                               |

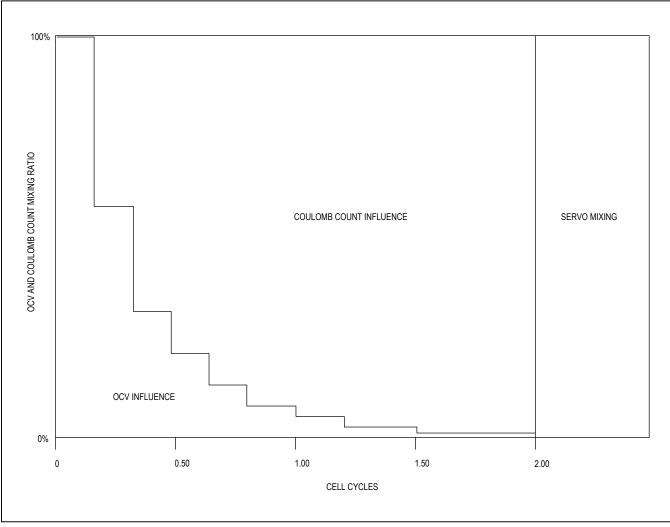

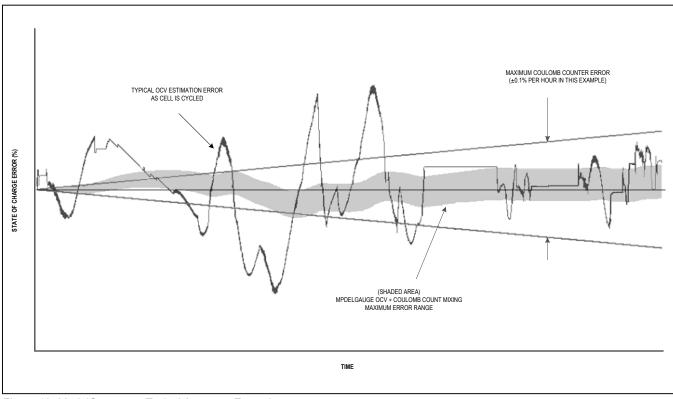

| OCV Estimation and Coulomb Count Mixing                    |

| Empty Compensation                                         |

| End-of-Charge Detection                                    |

| Fuel Gauge Learning                                        |

| Converge-to-Empty                                          |

| Determining Fuel Gauge Accuracy                            |

| Initial Accuracy                                           |

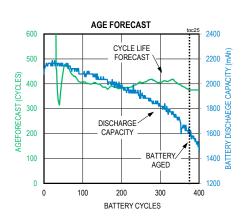

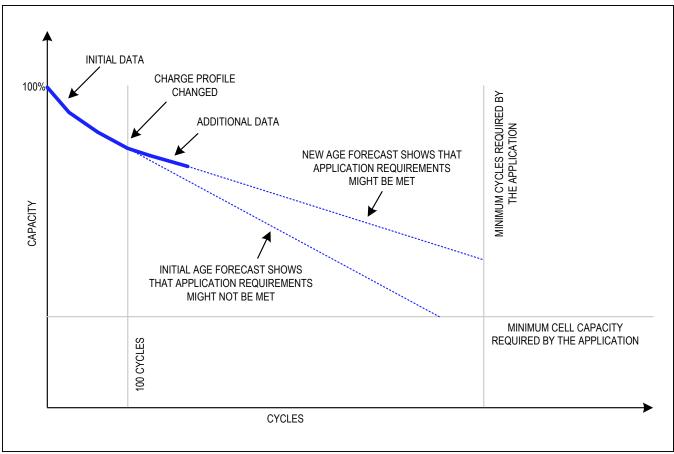

| Cycle+ Age Forecasting                                     |

| nAgeFcCfg Register (1D2h)43                                |

| AgeForecast Register (0B9h)43                              |

| Age Forecasting Requirements                               |

| Enabling Age Forecasting                                   |

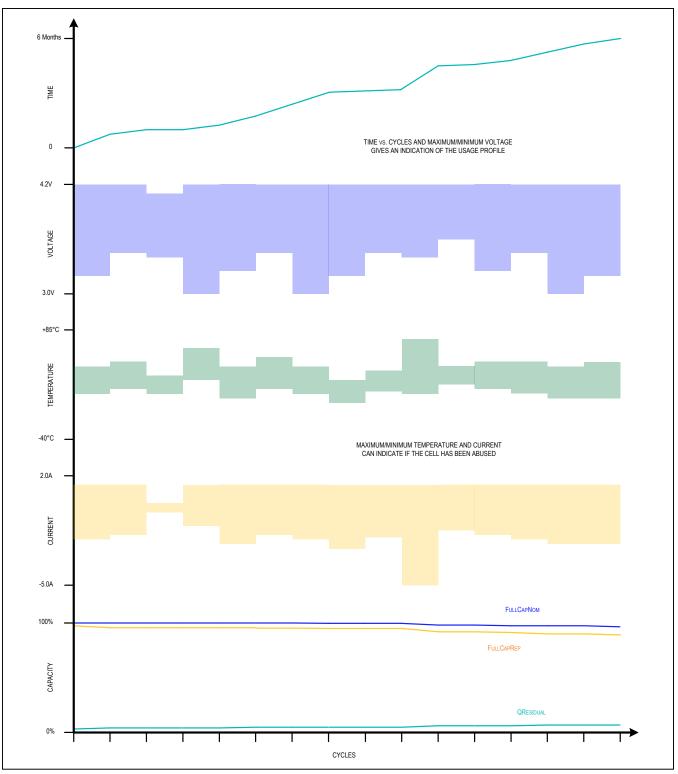

| Battery Life Logging                                       |

| Life-Logging Data Example                                  |

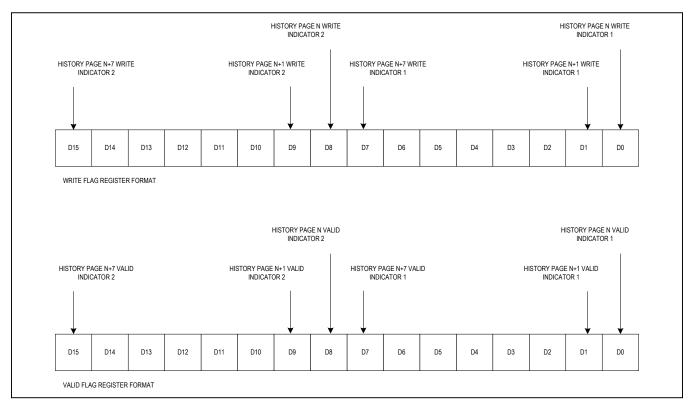

| Determining Number of Valid Logging Entries                |

| Reading History Data                                       |

| History Data Reading Example                               |

| ModelGauge m5 Algorithm Model Registers                    |

| nXTable0 (180h) to nXTable11 (18Bh) Registers              |

| nOCVTable0 (190h) to nOCVTable11 (19Bh) Registers          |

| nQRTable00 (1A0h) to nQRTable30 (1A3h) Registers           |

| nFullSOCThr Register (1C6h)                                |

| nVEmpty Register (19Eh)                                    |

| nDesignCap Register(1B3h)                                  |

| nRFastVShdn Register (1D5h)                                |

| nlChgTerm Register (19Ch)                                  |

| nRComp0 Register (1A6h)                                    |

| nTempCo Register (1A7h)                                    |

| nIAvgEmpty Register (1A8h)                                 |

| ModelGauge m5 Algorithm Configuration Registers         52 |

| nFilterCfg Register (19Dh)                                 |

| nRelaxCfg Register (1B6h)                                  |

| nLearnCfg Register (19Fh)                                  |

| nMiscCfg Register (1B2h)                                   |

| nTTFCfg Register (1C7h)                                    |

| nConvgCfg Register (1B7h)                                  |

| nRippleCfg Register (1B1h)                                 |

| TABLE OF CONTENTS (CONTINUED)                                         |            |

|-----------------------------------------------------------------------|------------|

| ModelGauge m5 Algorithm Additional Registers                          | 55         |

| Timer Register (03Eh)                                                 | 55         |

| dQAcc Register (045h)5                                                | 55         |

| dPAcc Register (046h)5                                                | 55         |

| QResidual Register (00Ch)                                             | 55         |

| VFSOC Register (0FFh)                                                 | 55         |

| VFOCV Register (0FBh)                                                 | 55         |

| QH Register (4Dh)                                                     | 55         |

| AvCap Register (01Fh)5                                                | 55         |

| AvSOC Register (00Eh)                                                 | 55         |

| MixSOC Register (00Dh)                                                | 55         |

| MixCap Register (00Fh)                                                | 56         |

| VFRemCap Register (04Ah)                                              | 56         |

| FStat Register (03Dh)                                                 | 56         |

| Modes of Operation                                                    | 57         |

| Status and Configuration Registers                                    | 58         |

| DevName Register (021h)                                               | 58         |

| nROMID0 (1BCh)/nROMID1 (1BDh)/nROMID2 (1BEh)/nROMID3 (1BFh) Registers | 58         |

| nRSense Register (1CFh)                                               | 59         |

| nPackCfg Register (1B5h)                                              | 59         |

| nNVCfg0 Register (1B8h).                                              | 30         |

| nNVCfg1 Register (1B9h)                                               | 31         |

| nNVCfg2 Register (1BAh)                                               | 32         |

| ShdnTimer Register (03Fh)                                             | 33         |

| nConfig Register (1B0h).                                              | 33         |

| Status Register (000h)                                                | 35         |

| Status2 Register (0B0h)                                               | 6          |

| nHibCfg Register (1B4h)                                               | 6          |

| CommStat Register (061h).                                             | 37         |

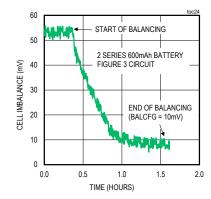

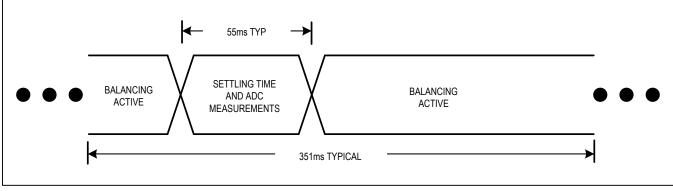

| Cell Balancing (MAX17205/MAX17215 Only)6                              | 37         |

| Cell Balancing Window of Operation                                    | 37         |

| Cell Balancing Order and Thresholds6                                  | 38         |

| Cell Balancing Current                                                | 39         |

| Cell Balancing Duty Cycle                                             | 39         |

| Analog Measurements                                                   | 39         |

| Voltage Measurement                                                   | 39         |

| Voltage Measurement Timing                                            | <i>'</i> 0 |

| VCell Register (009h)                                                 | <i>'</i> 0 |

| TABLE OF CONTENTS (CONTINUED)                                             |  |

|---------------------------------------------------------------------------|--|

| AvgVCell Register (019h)                                                  |  |

| MaxMinVolt Register (01Bh)                                                |  |

| Cell1 (0D8h)/Cell2 (0D7h)/Cell3 (0D6)/Cell4 (0D5h) Registers              |  |

| AvgCell1 (0D4h)/AvgCell2 (0D3h)/AvgCell3 (0D2h)/AvgCell4 (0D1h) Registers |  |

| CellX Register (0D9h)                                                     |  |

| Batt Register (0DAh)                                                      |  |

| Current Measurement                                                       |  |

| Current Measurement Timing                                                |  |

| MaxMinCurr Register (01Ch)                                                |  |

| nCGain Register (1C8h)                                                    |  |

| CGTempCo Register (16Dh)73                                                |  |

| Copper Trace Current Sensing                                              |  |

| Temperature Measurement                                                   |  |

| Temperature Measurement Timing                                            |  |

| AvgTA Register (016h)                                                     |  |

| MaxMinTemp Register (01Ah)                                                |  |

| nTCurve Register (1C9h)                                                   |  |

| nTGain (1CAh) Register/nTOff (1CBh) Register                              |  |

| Temp1 (134h)/Temp2 (13Bh)/IntTemp (135h) Registers                        |  |

| AvgTemp1 (137h)/AvgTemp2 (139h)/AvgIntTemp (138h) Registers               |  |

| AIN0 Register (027h)                                                      |  |

| At-Rate Functionality                                                     |  |

| AtRate Register (004h)                                                    |  |

| AtQResidual Register (0DCh)                                               |  |

| AtTTE Register (0DDh)                                                     |  |

| AtAvSOC Register (0CEh)                                                   |  |

| AtAvCap Register (0DFh)                                                   |  |

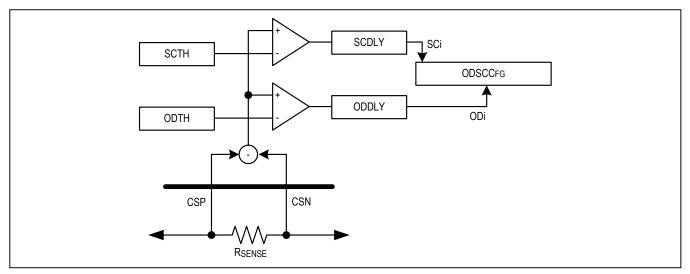

| Overcurrent Comparators                                                   |  |

| nODSCTh Register (18Eh)                                                   |  |

| nODSCCfg Register (18Fh)                                                  |  |

| Alert Function                                                            |  |

| nVAlrtTh Register (1C0h)                                                  |  |

| nTAIrtTh Register (1C1h)                                                  |  |

| nSAIrtTh Register (1C2h)                                                  |  |

| nIAIrtTh Register (1C3h)                                                  |  |

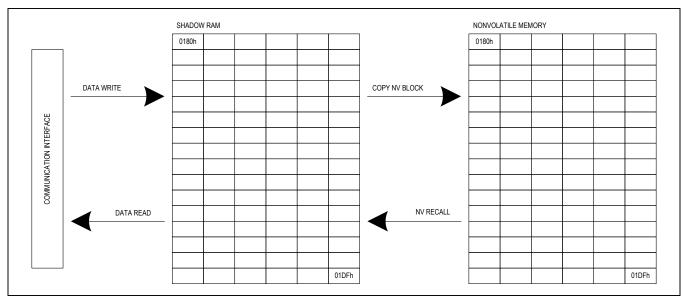

| Memory                                                                    |  |

| ModelGauge m5 Memory Space                                                |  |

| Nonvolatile Memory                                                        |  |

| TABLE OF CONTENTS (CONTINUED)                                                 |  |

|-------------------------------------------------------------------------------|--|

| Shadow RAM                                                                    |  |

| Nonvolatile Memory Commands                                                   |  |

| COPY NV BLOCK [E904h]                                                         |  |

| NV RECALL [E001h]                                                             |  |

| HISTORY RECALL [E2XXh]                                                        |  |

| Nonvolatile Block Programming                                                 |  |

| Determining the Number of Remaining Updates85                                 |  |

| General-Purpose Memory                                                        |  |

| Memory Locks                                                                  |  |

| NV LOCK [6AXXh]                                                               |  |

| Locking Memory Blocks                                                         |  |

| Reading Lock State                                                            |  |

| Smart Battery Compliant Operation                                             |  |

| SBS Compliant Memory Space (MAX1720x Only)91                                  |  |

| sFirstUsed Register (136h)                                                    |  |

| sCell1 (13Fh)/sCell2 (13Eh)/sCell3 (13Dh)/sCell4 (13Ch) Registers             |  |

| sAvgCell1 (14Fh)/sAvgCell2 (14Eh)/sAvgCell3 (14Dh)/sAvgCell4 (14Ch) Registers |  |

| sAvCap Register (167h)                                                        |  |

| sMixCap Register (168h)                                                       |  |

| sManfctInfo Register (170h)                                                   |  |

| Nonvolatile SBS Register Back-Up92                                            |  |

| nSBSCfg Register (1BBh)92                                                     |  |

| nDesignVoltage Register (1D3h)92                                              |  |

| nCGain and Sense Resistor Relationship93                                      |  |

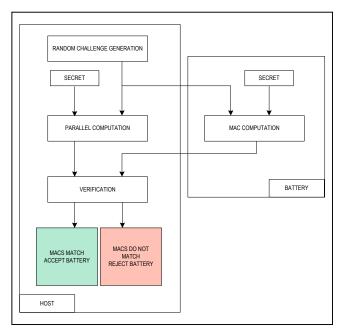

| SHA-256 Authentication                                                        |  |

| Authentication Procedure                                                      |  |

| Alternate Authentication Procedure                                            |  |

| Secret Management                                                             |  |

| Single Step Secret Generation                                                 |  |

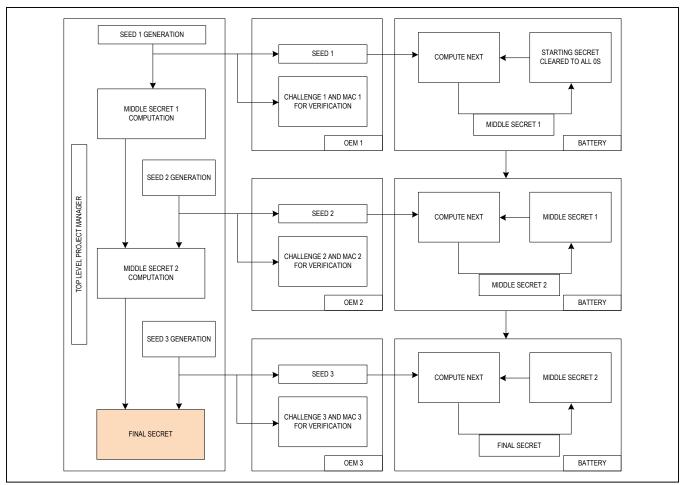

| Multistep Secret Generation Procedure         96                              |  |

| All OEMs                                                                      |  |

| Determining the Number of Remaining Updates97                                 |  |

| Authentication Commands                                                       |  |

| Compute MAC Without ROM ID [3600h]                                            |  |

| Compute MAC with ROM ID [3500h]97                                             |  |

| Compute Next Secret Without ROM ID [3000h]97                                  |  |

| Compute Next SECRET WITH ROM ID [3300h]98                                     |  |

| TABLE OF CONTENTS (CONTINUED)               |     |

|---------------------------------------------|-----|

| CLEAR SECRET [5A00h]                        | 98  |

| LOCK SECRET [6000h]                         | 98  |

| Device Reset                                | 98  |

| Reset Commands                              | 98  |

| Hardware Reset [000Fh to Address 060h]      | 98  |

| Fuel Gauge Reset [0001h to Address 0BBh]    | 98  |

| Communication                               | 98  |

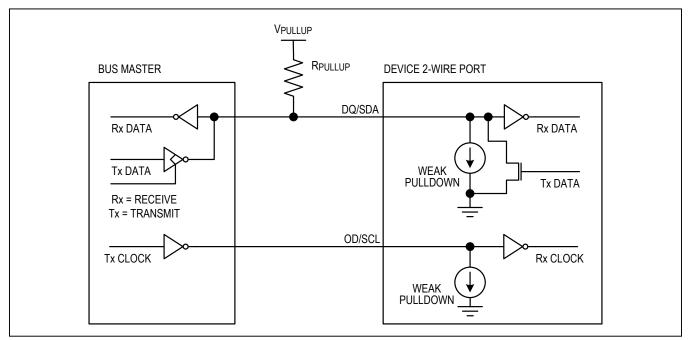

| 2-Wire Bus System (MAX17201/MAX17205 Only)  | 98  |

| Hardware Configuration                      | 99  |

| I/O Signaling                               | 99  |

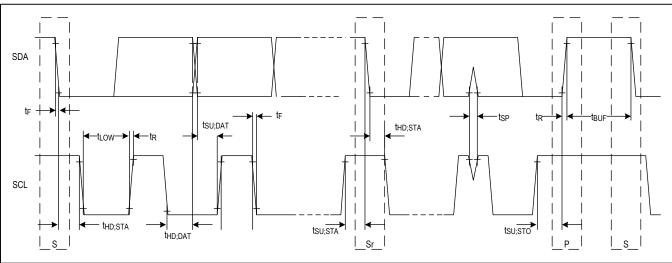

| Bit Transfer                                | 99  |

| Bus Idle                                    | 99  |

| START and STOP Conditions                   | 99  |

| Acknowledge Bits.                           | 99  |

| Data Order                                  | 100 |

| Slave Address                               | 100 |

| Read/Write Bit                              | 100 |

| Bus Timing                                  | 100 |

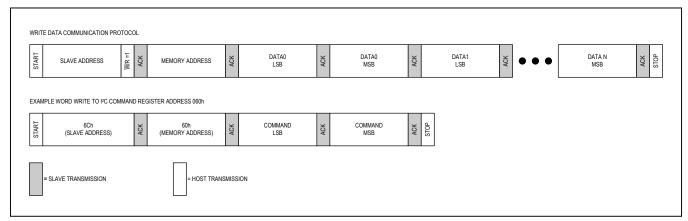

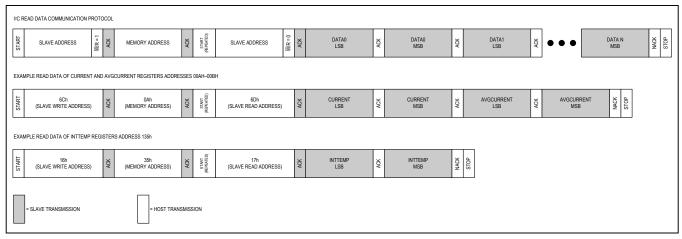

| I <sup>2</sup> C Protocols                  | 101 |

| I <sup>2</sup> C Write Data Protocol        | 101 |

| I <sup>2</sup> C Read Data Protocol         | 101 |

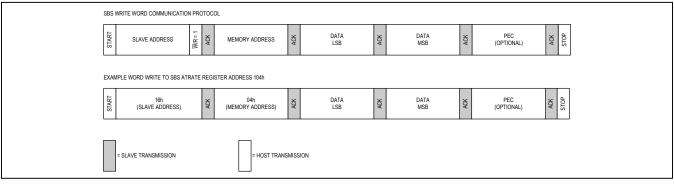

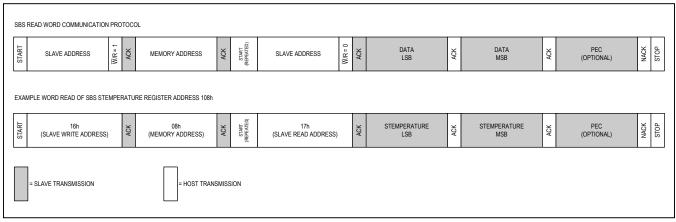

| SBS Protocols                               |     |

| SBS Write Word Protocol.                    | 102 |

| SBS Read Word Protocol                      | 103 |

| SBS Write Block Protocol                    | 103 |

| SBS Read Block Protocol                     |     |

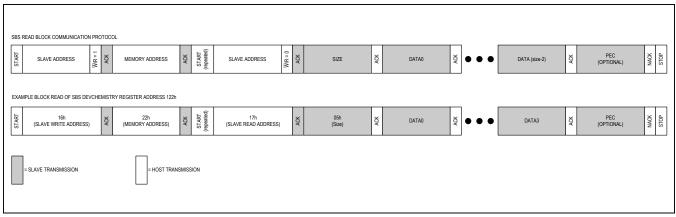

| Packet Error Checking                       |     |

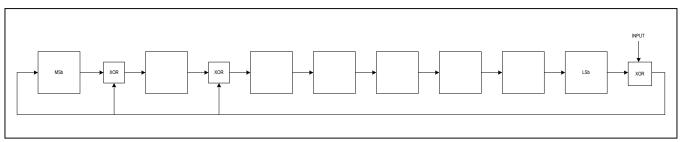

| 1-Wire Bus System (MAX17211/MAX17215 Only). | 104 |

| Hardware Configuration                      | 105 |

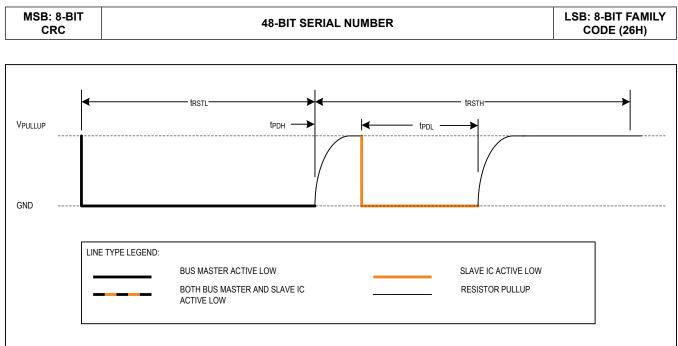

| 64-Bit Net Address (ROM ID)                 | 106 |

| I/O Signaling.                              | 106 |

| Reset Time Slot                             |     |

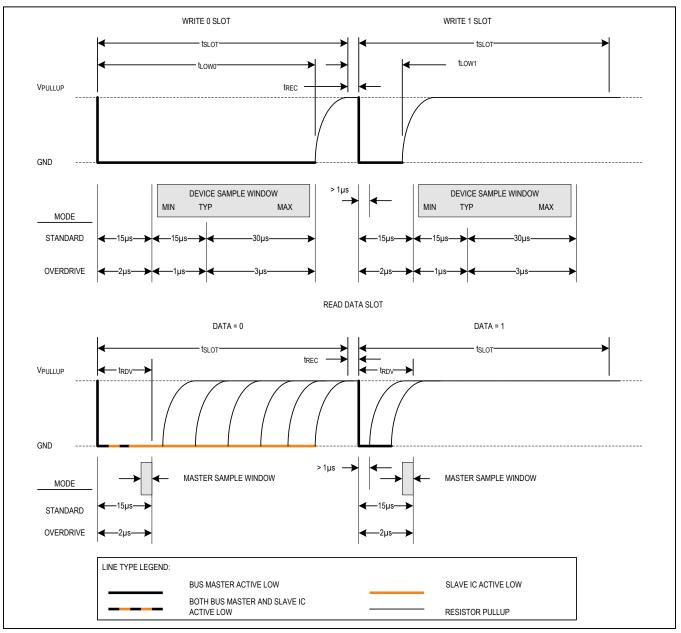

| Write Time Slots.                           | 106 |

| Read Time Slots                             |     |

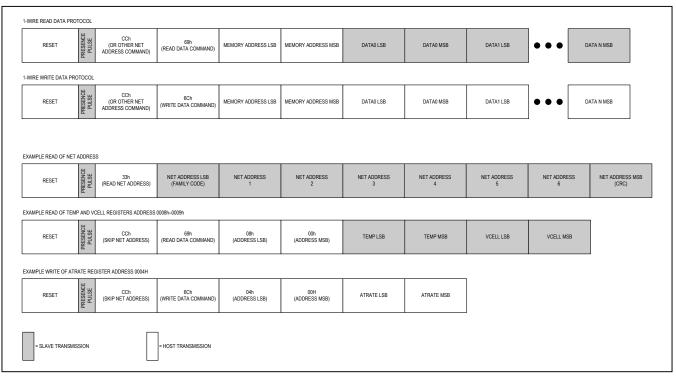

| Transaction Sequence                        |     |

| Net Address Commands                        |     |

| Read Net Address [33h]                      | 108 |

| Match Net Address [55h]                     | 108 |

# Stand-Alone ModelGauge m5 Fuel Gauge with SHA-256 Authentication

| TABLE OF CONTENTS (CONTINUED)                        |  |

|------------------------------------------------------|--|

| Skip Net Address [CCh]                               |  |

| Search Net Address [F0h]                             |  |

| 1-Wire Functions                                     |  |

| Read Data [69h, LL, HH]                              |  |

| Write Data [6Ch, LL, HH]                             |  |

| Summary of Commands                                  |  |

| Appendix A: Reading History Data Psuedo-Code Example |  |

| Ordering Information                                 |  |

| Revision History                                     |  |

### LIST OF FIGURES

| Figure 1. Single-Cell Schematic.                                 | 27 |

|------------------------------------------------------------------|----|

| Figure 2. Multicell Schematics                                   | 28 |

| Figure 3. Cell-Balancing Circuit Schematics                      | 29 |

| Figure 4. Merger of Coulomb Counter and Voltage-Based Fuel Gauge | 30 |

| Figure 5. ModelGauge m5 Block Diagram                            | 31 |

| Figure 6. ModelGauge m5 Registers                                | 32 |

| Figure 7. nSOC (1AEh) Format When nNVCfg2.enSOC = 1              | 34 |

| Figure 8. nVoltTemp (1AAh) Format When nNVCfg2.enVT = 1          | 34 |

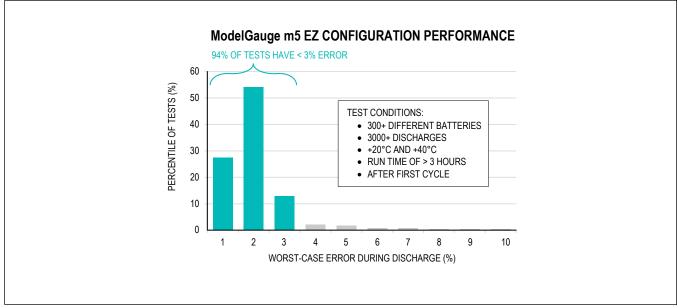

| Figure 9. EZ Configuration Performance Histogram                 | 35 |

| Figure 10. EZ Configuration Performance vs. Test Conditions      | 35 |

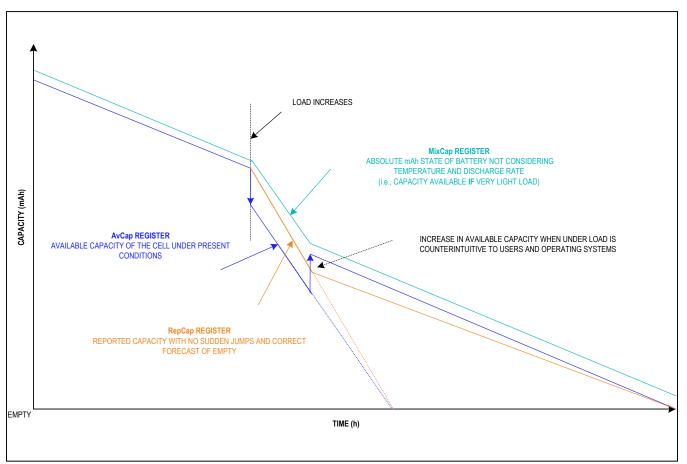

| Figure 11. Voltage and Coulomb Count Mixing                      | 36 |

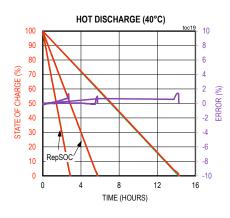

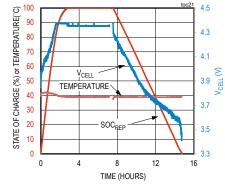

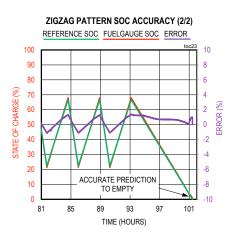

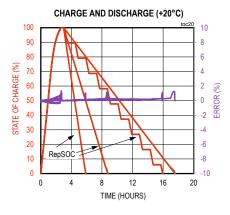

| Figure 12. ModelGauge m5 Typical Accuracy Example                | 37 |

| Figure 13. Handling Changes in Empty Calculation                 | 38 |

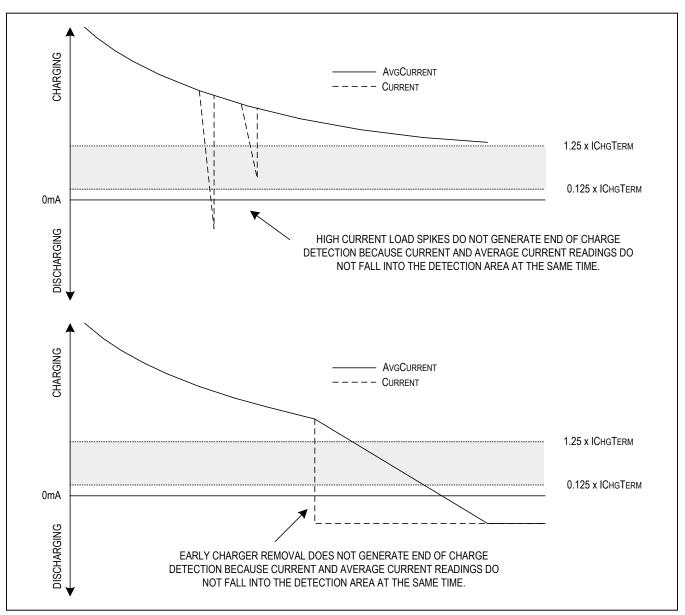

| Figure 14. Blocking False End of Charge Events                   | 39 |

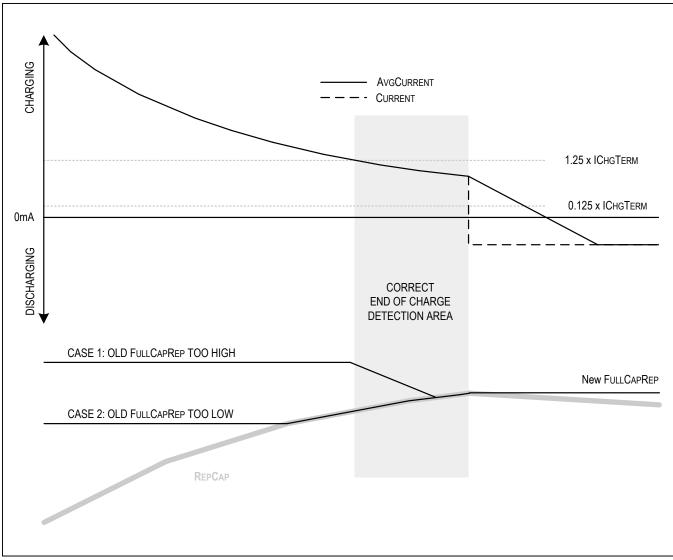

| Figure 15. FullCapRep Learning at End of Charge                  | 40 |

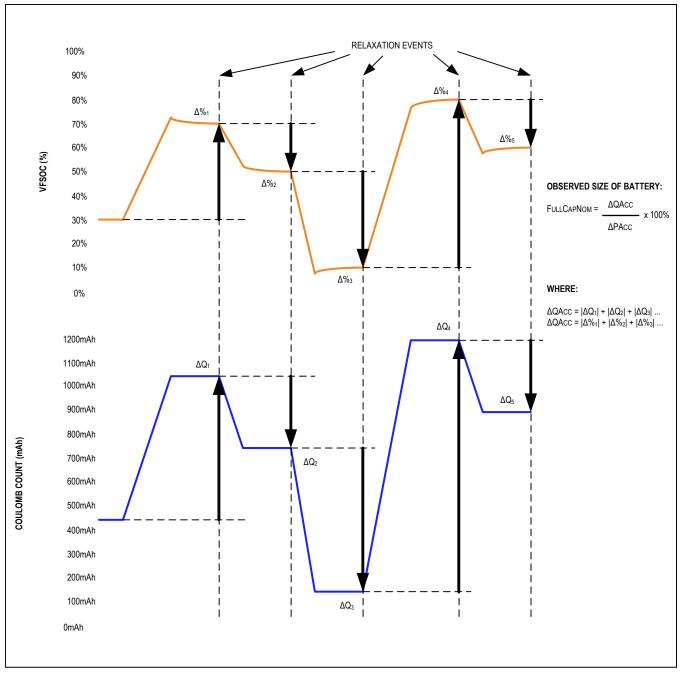

| Figure 16. FullCapNom Learning                                   | 41 |

| Figure 17. Converge to Empty                                     | 42 |

| Figure 18. nAgeFcCfg Register (1D2h) Format                      | 43 |

| Figure 19. Benefits of Age Forecasting                           | 44 |

| Figure 20. Sample Life-Logging Data                              | 46 |

| Figure 21. Write Flag Register and Valid Flag Register Formats   | 47 |

| Figure 22. nFullSOCThr (1C6h)/FullSOCThr (013h) Format           | 50 |

| Figure 23. VEmpty (03Ah)/nVEmpty (19Eh) Format                   | 50 |

| LIST OF FIGURES (CONTINUED)                                             |   |  |

|-------------------------------------------------------------------------|---|--|

| Figure 24. nRFastVshdn (1D5h) Format                                    | 1 |  |

| Figure 25. FilterCfg (029h)/nFilterCfg (19Dh) Format                    | 2 |  |

| Figure 26. RelaxCfg (02Ah)/nRelaxCfg (1B6h) Format                      | 2 |  |

| Figure 27. LearnCfg (028h)/nLearnCfg (19Fh) Format                      | 3 |  |

| Figure 28. MiscCfg (02Bh)/nMiscCfg (1B2h) Format                        | 3 |  |

| Figure 29. nTTFCfg (1C7h) Format                                        | 4 |  |

| Figure 30. nConvgCfg (1B7h) Format                                      | 4 |  |

| Figure 31. nRippleCfg (1B1h) Format                                     | 4 |  |

| Figure 32. FStat (03Dh) Format                                          | ô |  |

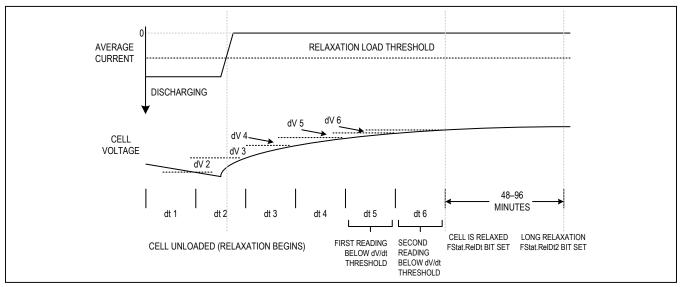

| Figure 33. Cell Relaxation Detection                                    | 6 |  |

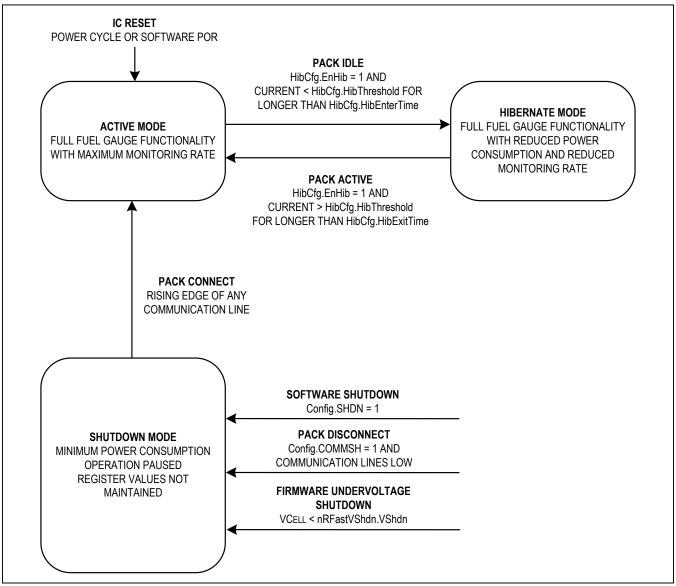

| Figure 34. Flowchart of Operating Modes                                 | 7 |  |

| Figure 35. DevName (021h) Format                                        | 8 |  |

| Figure 36. nROMID (1BCh to 1BFh) Format 58                              | 8 |  |

| Figure 37. PackCfg (0BDh)/nPackCfg (1B5h) Format                        | 9 |  |

| Figure 38. nNVCfg0 (1B8h) Format                                        | 0 |  |

| Figure 39. nNVCfg1 (1B9h) Format                                        | 1 |  |

| Figure 40. nNVCfg2 (1BAh) Format                                        | 2 |  |

| Figure 41. ShdnTimer (03Fh) Format                                      | 3 |  |

| Figure 42. nConfig (1B0h) Format                                        | 3 |  |

| Figure 43. Config (01Dh) Format                                         | 3 |  |

| Figure 44. Config2 (0BBh) Format                                        | 3 |  |

| Figure 45. Status (000h) Format                                         | 5 |  |

| Figure 46. Status2 (0B0h) Format                                        | 6 |  |

| Figure 47. HibCfg (0BAh)/nHibCfg (1B4h) Format                          | 6 |  |

| Figure 48. CommStat (061h) Format                                       | 7 |  |

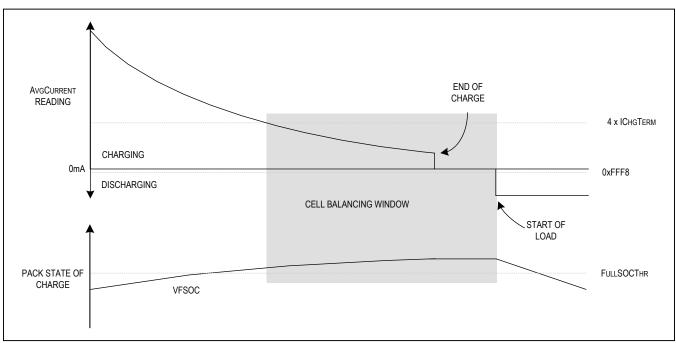

| Figure 49. Cell Balancing Window of Operation                           | 7 |  |

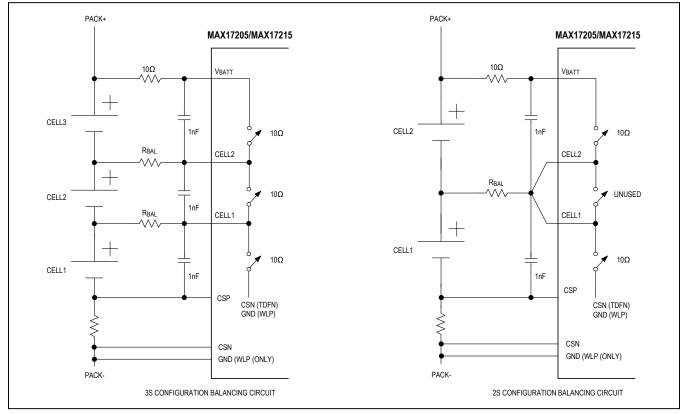

| Figure 50. 2S and 3S Balancing Circuits                                 | 8 |  |

| Figure 51. Cell Balancing Duty Cycle                                    | 9 |  |

| Figure 52. MaxMinVolt (01Bh)/nMaxMinVolt (1ACh) Format                  | 1 |  |

| Figure 53. MaxMinCurr (01Ch)/nMaxMinCurr (1ABh) Format                  | 3 |  |

| Figure 54. nCGain Register (1C8h) Format                                | 3 |  |

| Figure 55. MaxMinTemp (01Ah)/nMaxMinTemp (1ADh) Format                  | ô |  |

| Figure 56. Overcurrent Comparator Diagram                               | 8 |  |

| Figure 57. ODSCTh Register (0F2h) and nODSCTh Register (18Eh) Formats   | 8 |  |

| Figure 58. ODSCCfg Register (0F3h) and nODSCCfg Register (18Fh) Formats | 9 |  |

| Figure 59. VAIrtTh (001h)/nVAIrtTh (1C0h) Format                        | D |  |

| Figure 60. TAIrtTh (002h)/nTAIrtTh (1C1h) Format                        | D |  |

| Figure 61. SAIrtTh (003h)/nSAIrtTh (1C2h) Format                        | 0 |  |

# Stand-Alone ModelGauge m5 Fuel Gauge with SHA-256 Authentication

| LIST OF FIGURES (CONTINUED)                                           |     |

|-----------------------------------------------------------------------|-----|

| Figure 62. IAlrtTh (0B4h)/nIAlrtTh (1C3h) Format                      | 81  |

| Figure 63. Shadow RAM and Nonvolatile Memory Relationship             | 84  |

| Figure 64. Format of LOCK Command                                     | 90  |

| Figure 65. Format of Lock Register (07Fh)                             | 90  |

| Figure 66. nSBSCfg (1BBh) Format.                                     |     |

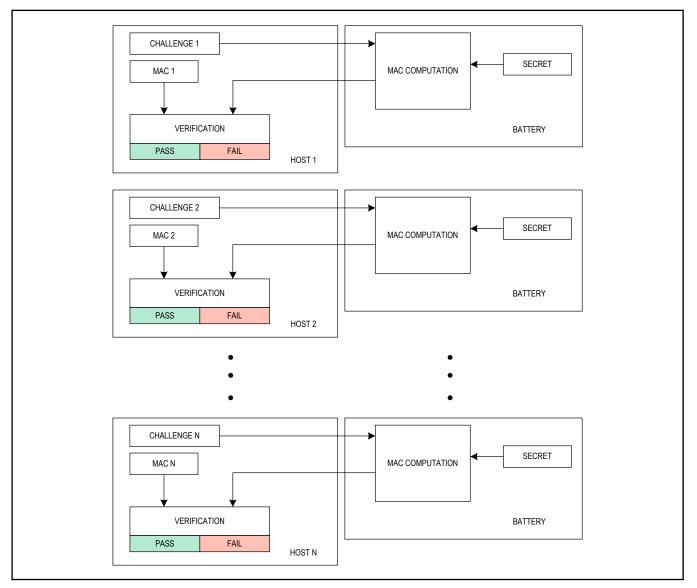

| Figure 67. Procedure to Verify a Battery                              | 93  |

| Figure 68. Battery Authentication Without a Host-Side Secret          |     |

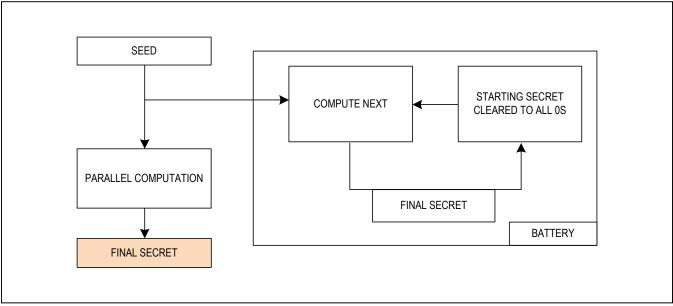

| Figure 69. Single Step Secret Generation Example                      |     |

| Figure 70. Multistep Secret Generation Example                        |     |

| Figure 71. 2-Wire Bus Interface Circuitry                             |     |

| Figure 72. 2-Wire Bus Timing Diagram                                  | 100 |

| Figure 73. Example I <sup>2</sup> C Write Data Communication Sequence | 101 |

| Figure 74. Example I <sup>2</sup> C Read Data Communication Sequence  | 102 |

| Figure 75. Example SBS Write Word Communication Sequence              | 102 |

| Figure 76. Example SBS Read Word Communication Sequence               | 103 |

| Figure 77. Example SBS Read Block Communication Sequence.             | 104 |

| Figure 78. PEC CRC Generation Block Diagram                           | 104 |

| Figure 79. 1-Wire Bus Interface Circuitry                             | 105 |

| Figure 80. 1-Wire Initialization Sequence                             | 106 |

| Figure 81. 1-Wire Write and Read Time Slots                           | 107 |

| Figure 82. Example 1-Wire Communication Sequences.                    | 109 |

|                                                                       |     |

### LIST OF TABLES

| Table 1. ModelGauge Register Standard Resolutions.         Image: Control of the standard Resolutions in the standard Resolutions in the standard Resolutions in the standard Resolution is a standard Resolution in the standard Resolution in the standard Resolution in the standard Resolution is a standard Resolution in the standard Resolutin in the standard Resolution in the standard Resolution i | 26 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Table 2. Minimum and Maximum Cell Sizes for Age Forecasting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 44 |

| Table 3. Life Logging Register Summary.         Image: Comparison of the second seco                                                                                                                                                                                                                                             | 45 |

| Table 4. Decoding History Page Flags         Image: Control of the second sec                                                                                                                                                                                                                                             | 48 |

| Table 5. Reading History Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 48 |

| Table 6. Reading History Page Flags                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 49 |

| Table 7. Recommended nRSense Register Values for Common-Sense Resistors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 59 |

| Table 8. Fuel Gauge Temperature Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 60 |

| Table 9. Cell Balancing Thresholds                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 68 |

| Table 10. Voltage Measurement Timing.         Image: Control of the second sec                                                                                                                                                                                                                                            | 70 |

| Table 11. Current Measurement Timing.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 72 |

| Table 12. Current Measurement Range and Resolution vs. Sense Resistor Value                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 72 |

# Stand-Alone ModelGauge m5 Fuel Gauge with SHA-256 Authentication

## LIST OF TABLES (CONTINUED)

| Table 13. Copper Trace Sensing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 14. Temperature Measurement Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |

| Table 15. Register Settings for Common Thermistor Types                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

| Table 16. Top-Level Memory Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 81  |

| Table 17. Individual Registers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 82  |

| Table 18. ModelGauge m5 Register Memory Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 82  |

| Table 19. Nonvolatile Register Memory Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 83  |

| Table 20. History Recall Command Functions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 84  |

| Table 21. Number of Remaining Config Memory Updates         Image: Config Memory U | 85  |

| Table 22. Nonvolatile Memory Configuration Options    Image: Configuration Options                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 86  |

| Table 23. SBS Register Space Memory Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 91  |

| Table 24. SBS to Nonvolatile Memory Mapping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

| Table 25. nCGain Register Settings to Meet SBS Compliance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

| Table 26. Number of Remaining Secret Updates                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

| Table 27. 2-Wire Slave Addresses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 100 |

| Table 28. Valid SBS Read Block Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 103 |

| Table 29. 1-Wire Net Address Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 106 |