### Wellness Measurement Microcontroller

#### **General Description**

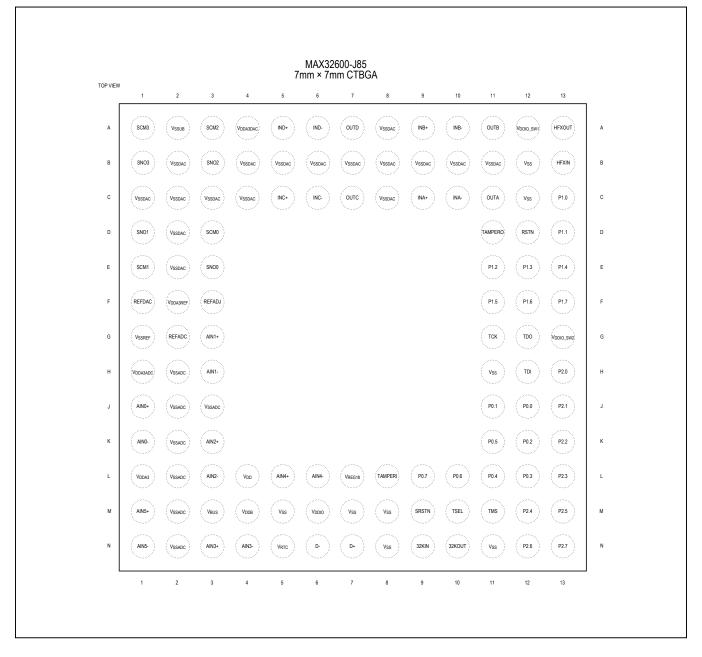

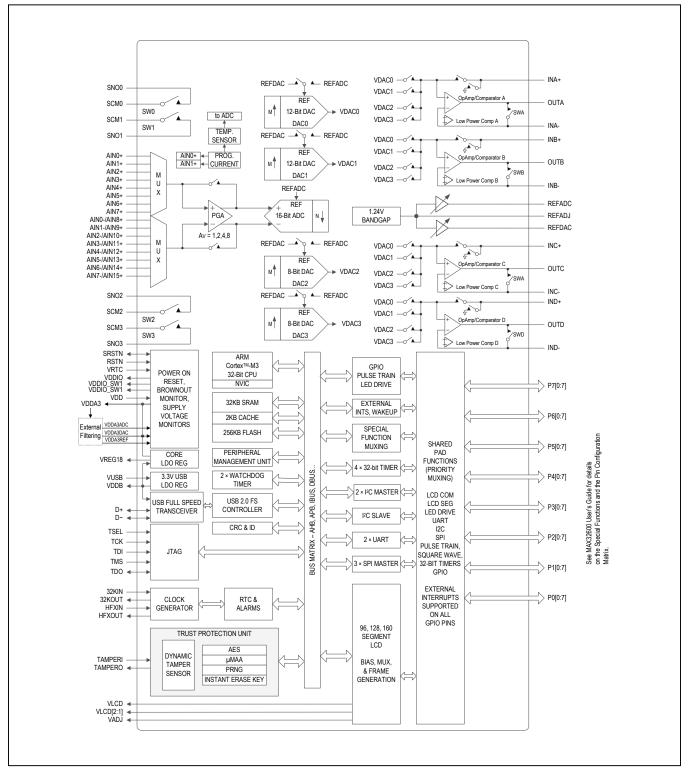

The MAX32600 microcontroller is based on the industry-standard ARM<sup>®</sup> Cortex<sup>®</sup>-M3 32-bit RISC CPU operating at up to 24MHz. It includes 256KB of flash memory, 32KB of SRAM, a 2KB instruction cache, and integrated high-performance analog peripherals. The MAX32600 is available in the following package options: 192-ball, 12mm x 12mm CTBGA; 120-ball, 7mm x 7mm CTBGA; and 108-ball, 5.4mm x 4.3mm WLP.

#### **Applications**

- Wearable Medical Devices

- Pulse Oximetry Measurement

- Galvanic Skin Response Measurement

- Blood Glucose Metering

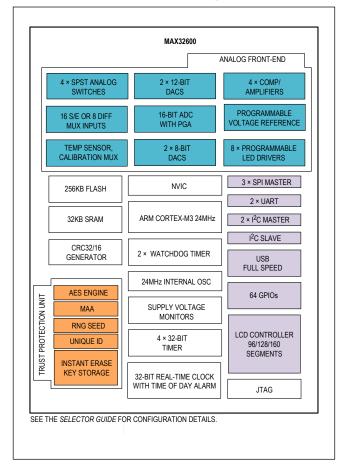

#### Simplified Functional Diagram

#### **Benefits and Features**

- Integrated AFE Enables Precision Wellness

Measurements with Minimal Discretes

- 16-Bit ADC with Input Mux and PGA

- Up to 500ksps Conversion Rate

- PGA with Gain of 1, 2, 4, and 8 and Bypass Mode

- Differential 8:1 or Single-Ended 16:1 Input Mux

- Internal Mux Inputs for Measuring V<sub>DDA3</sub>

- Internal or External Voltage Reference

- Programmable Buffers for ADC and DACs

- Two 12-Bit DACs and Two 8-Bit DACs

- Four Operational Amplifiers

- Four Low-Power Comparators

- · Four Uncommitted SPST Analog Switches

- Four Ground Switches

- Up to Eight 100mA LED Driver Pairs (Sink)

- Internal Temperature Sensor

- Secure Valuable IP and Data with Robust On-Board Trust Protection Unit

- Trust Protection Unit for End-to-End Security

- AES Hardware Engine

- µMAA for ECDSA and RSA

- Hardware PRNG

- Fast-Erase SRAM for Secure Key Storage

- Industry's Lowest Overall System Power Increases Battery Life

- 175µA/MHz Active Power Executing Code from Cache

- 1.25µA Current Consumption with Real-Time Clock Enable in LP0

- 1.8µA Current Consumption with Data Retention and Fast 15µs Wakeup in LP1

- Peripheral Clock Control

- 6-Channel DMA Engine Enables Intelligent Peripheral Operation While Micro is in Sleep Mode

- Flexible Package Options

- 120-Ball CTBGA, 0.5mm Pitch, 7mm x 7mm

- 192-Ball CTBGA, 0.65mm Pitch, 12mm x 12mm

- 108-Bump WLP, 0.4mm Pitch, 5.4mm x 4.3mm

Additional Benefits and Features and Ordering Information appear at end of data sheet.

ARM and Cortex are registered trademarks of ARM Ltd.

### Wellness Measurement Microcontroller

#### **Absolute Maximum Ratings**

| Voltage Range on V <sub>DD</sub> and V <sub>DDA3</sub> with      |                                   |

|------------------------------------------------------------------|-----------------------------------|

| Respect to GND                                                   | 0.3V to +3.6V                     |

| Voltage Range on V <sub>BUS</sub>                                | 0.3V to 5.5V                      |

| Voltage Range on Any Lead with                                   |                                   |

| Respect to GND (excluding V <sub>BUS</sub> )                     | -0.3V to (V <sub>DD</sub> + 0.5V) |

| Voltage Range on Analog Pins with                                |                                   |

| Respect to GND                                                   | 0.3V to V <sub>DDA3</sub>         |

| Total Current into V <sub>DD</sub> /V <sub>DDA3</sub> Power Line |                                   |

| Total Current Source V <sub>DD</sub> Power Lines (S              | Sink)100mA                        |

| Output Current (Sink) by Any I/O Pin          | 25mA            |

|-----------------------------------------------|-----------------|

| Output Current (Source) by Any I/O Pin        | 25mA            |

| Output Current (Source) by V <sub>DDIO</sub>  | 100mA           |

| Output Current (Sink) by LED Pins             | 135mA           |

| Output Current (Source) by V <sub>REG18</sub> | 50mA            |

| Operating Temperature Range                   | 40°C to +85°C   |

| Storage Temperature Range                     | -65°C to +150°C |

| Soldering Temperature (reflow)                | +260°C          |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

192 CTBGA

### Package Thermal Characteristics (Note 1)

| 108 WLP                                                          |    |

|------------------------------------------------------------------|----|

| Junction-to-Ambient Thermal Resistance (0 <sub>JA</sub> )32.99°C | /W |

| 120 CTBGA                                                        |    |

Junction-to-Ambient Thermal Resistance  $(\theta_{JA})$  .....29.50°C/W Junction-to-Case Thermal Resistance  $(\theta_{JC})$  ......9.40°C/W

Note 1: Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to www.maximintegrated.com/thermal-tutorial.

#### **Recommended DC Operating Conditions**

$(V_{DD} = V_{RST} \text{ to } 3.6V, T_A = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}, \text{ unless otherwise noted.})$  (Note 2)

| PARAMETER                             | SYMBOL             | CONDITIONS                                                                  | MIN | TYP   | MAX | UNITS |  |

|---------------------------------------|--------------------|-----------------------------------------------------------------------------|-----|-------|-----|-------|--|

| Digital Domain Voltage                | V <sub>DD</sub>    | (Note 3)                                                                    | 1.8 |       | 3.6 | V     |  |

| Analog Domain Voltage                 | V <sub>DDA3</sub>  |                                                                             | 2.3 |       | 3.6 | V     |  |

| 1.8V Internal Regulator               | V <sub>REG18</sub> |                                                                             |     | 1.8   |     | V     |  |

| Power-Fail Warning Voltage for Supply | V <sub>PFW</sub>   | Monitors V <sub>DD</sub> , PFWVSBIT = 0x0016                                |     | 2.525 |     | V     |  |

| Power-Fail Reset Voltage              | V <sub>RST</sub>   | Monitors V <sub>DD</sub>                                                    |     | 1.765 |     | V     |  |

| Power-On-Reset Release<br>Voltage     | V <sub>SPOR</sub>  | Monitors V <sub>DD</sub> or V <sub>DDB</sub>                                |     |       | 1.8 | V     |  |

| RAM Data Retention Voltage            | V <sub>DRV</sub>   |                                                                             |     | 1.0   |     | V     |  |

| LP3 Active Current                    | IDDLP3             | Cache disabled, f <sub>CK</sub> = 24MHz                                     |     | 5     |     |       |  |

| (Note 4)                              |                    | Cache enabled, execution from cache, 100% hit rate, f <sub>CK</sub> = 24MHz |     | 6.10  |     | mA    |  |

| LP2 Current                           |                    | One PMU channel enabled                                                     |     | 1.25  |     | mA    |  |

| LP2 Current                           | IDDLP2             | Each additional PMU channel                                                 |     | 200   |     | μA    |  |

| L D4 Oursest                          |                    | RTC enabled, V <sub>DD</sub> supply current                                 |     | 1.8   |     |       |  |

| LP1 Current                           | IDDLP1             | RTC disabled, V <sub>DD</sub> supply current                                |     | 1.4   |     | - μΑ  |  |

| LDO Current                           |                    | RTC enabled, V <sub>DD</sub> supply current                                 |     | 1250  |     | ~^    |  |

| LP0 Current                           | IDDLP0             | RTC disabled, V <sub>DD</sub> supply current                                |     | 850   |     | – nA  |  |

| LP2 Mode Resume Time                  | t <sub>ONLP2</sub> | One PMU channel active                                                      |     | 0     |     | μs    |  |

# Wellness Measurement Microcontroller

### **Recommended DC Operating Conditions (continued)**

(V<sub>DD</sub> = V<sub>RST</sub> to 3.6V, T<sub>A</sub> = -40°C to +85°C, unless otherwise noted.) (Note 2)

| PARAMETER                                              | SYMBOL               | CONDITIONS                                                                                          | MIN                        | ТҮР                       | MAX                        | UNITS    |

|--------------------------------------------------------|----------------------|-----------------------------------------------------------------------------------------------------|----------------------------|---------------------------|----------------------------|----------|

| LP1 Mode Resume Time                                   | t <sub>ONLP1</sub>   |                                                                                                     |                            | 15                        |                            | μs       |

| LP0 Mode Resume Time                                   | t <sub>ONLP0</sub>   |                                                                                                     |                            | 26                        |                            | μs       |

| Input Low Voltage for SRSTN and All Port Pins          | V <sub>IL</sub>      |                                                                                                     |                            |                           | 0.3 ×<br>V <sub>DDIO</sub> | V        |

| Input High Voltage for SRSTN and All Port Pins         | V <sub>IH</sub>      |                                                                                                     | 0.7×<br>V <sub>DDIO</sub>  |                           |                            | V        |

| Input Hysteresis (Schmitt)                             | VIHYS                |                                                                                                     |                            | 300                       |                            | mV       |

| Output Low Voltage for All Port<br>Pins                | V <sub>OL</sub>      | $V_{DD}$ = 3.6V, I <sub>OL</sub> = 11mA<br>$V_{DD}$ = 2.3V, I <sub>OL</sub> = 8mA                   |                            | 0.4                       | 0.5<br>0.5                 | - V      |

| Output High Voltage for All<br>Port Pins               | V <sub>OH</sub>      | I <sub>OH</sub> = -2mA                                                                              | V <sub>DDIO</sub><br>- 0.5 |                           |                            | V        |

| Input/Output Pin Capacitance<br>for All GPIO Port Pins | C <sub>IO</sub>      |                                                                                                     |                            | 5                         |                            | pF       |

| Pullup Resistance for All GPIO                         | R <sub>PU25K</sub>   | Normal drive mode                                                                                   |                            | 25                        |                            | kΩ       |

| Port Pins                                              | R <sub>PU1M</sub>    | Weak pullup enabled                                                                                 |                            | 1                         |                            | MΩ       |

| Input Leakage Current Low                              | ١ <sub>IL</sub>      | V <sub>IN</sub> = 0V, internal pullup disabled                                                      | -100                       |                           | +100                       | nA       |

| Input Leakage Current High                             | Ін                   | V <sub>IN</sub> < V <sub>DD</sub> + 0.6V or 3.6V or whichever<br>is lower, internal pullup disabled | -100                       |                           | +100                       | nA       |

| FLASH MEMORY                                           |                      |                                                                                                     |                            |                           |                            |          |

| Flash Erase Time                                       | t <sub>ME</sub>      | Mass erase                                                                                          |                            | 30                        |                            | me       |

|                                                        | t <sub>ERASE</sub>   | Page erase                                                                                          |                            | 30                        |                            | - ms     |

| Flash Programming Time per Word                        | t <sub>PROG</sub>    |                                                                                                     |                            | 60                        |                            | μs       |

| Flash Endurance                                        |                      | (Note 5)                                                                                            | 20                         |                           |                            | K cycles |

| Data Retention                                         | t <sub>RET</sub>     | T <sub>A</sub> = +25°C (Note 5)                                                                     | 100                        |                           |                            | Years    |

| LCD                                                    |                      |                                                                                                     |                            |                           |                            |          |

| LCD Reference Voltage                                  | V <sub>LCD</sub>     | V <sub>LCD</sub> output boost voltage;<br>V <sub>DD</sub> = 2.0V to 3.6V                            |                            | 3.3                       |                            | V        |

|                                                        |                      | 2/3 level                                                                                           | V <sub>ADJ</sub> +         | 2/3 (V <sub>LCD</sub>     | - V <sub>ADJ</sub> )       |          |

| LCD Segment/Common Bias<br>Voltage                     | V <sub>LCDBIAS</sub> | 1/2 level                                                                                           | V <sub>ADJ</sub> +         | 1/2 (V <sub>LCD</sub>     | - V <sub>ADJ</sub> )       | V        |

| vollage                                                |                      | 1/3 level                                                                                           | V <sub>ADJ</sub> +         | 1/3 (V <sub>LCD</sub>     | - V <sub>ADJ</sub> )       |          |

|                                                        |                      | LCD_LCRA[3:0] = 0                                                                                   |                            | 0                         |                            |          |

| LCD Adjustment Voltage                                 | V <sub>ADJ</sub>     | LCD_LCRA[3:0] = 15                                                                                  |                            | 0.4 ×<br>V <sub>LCD</sub> |                            | V        |

| LCD Dies Desister                                      |                      | Static and 1/3 bias                                                                                 |                            | 108                       |                            | 1:0      |

| LCD Bias Resistor                                      | R <sub>LCD</sub>     | 1/2 bias                                                                                            |                            | 72                        |                            | - kΩ     |

| LCD Adjustment Resistor                                | R <sub>LADJ</sub>    | LCD_LCRA[3:0] = 15                                                                                  |                            | 72                        |                            | kΩ       |

# Wellness Measurement Microcontroller

### **Recommended DC Operating Conditions (continued)**

(V<sub>DD</sub> = V<sub>RST</sub> to 3.6V, T<sub>A</sub> = -40°C to +85°C, unless otherwise noted.) (Note 2)

| PARAMETER                                                 | SYMBOL             | CONDITIONS                                                                    | MIN | ТҮР    | MAX | UNITS |

|-----------------------------------------------------------|--------------------|-------------------------------------------------------------------------------|-----|--------|-----|-------|

| REAL-TIME CLOCK (RTC)                                     |                    |                                                                               |     |        |     |       |

| RTC Input Frequency                                       | f <sub>32KIN</sub> | 32kHz watch crystal                                                           | 3   | 32.768 |     | kHz   |

|                                                           | IRTC               | Micro in LP2 or LP3                                                           |     | 0.7    |     | μA    |

| RTC Operating Current                                     | IRTC_LP0           | Micro in LP0 or LP1                                                           |     | 0.4    |     | μA    |

| RTC Initial Power-Up Time                                 | tRTC_PUP           | (Note 6)                                                                      |     | 250    |     | ms    |

| RTC Power Mode Transition<br>Time from LP0/LP1 to LP2/LP3 |                    | RTC transition from low to high power drive, not required in all applications |     | 256    |     | ms    |

#### **USB Electrical Characteristics**

(V<sub>DD</sub> = V<sub>RST</sub> to 3.6V,  $T_A$  = -40°C to +85°C, unless otherwise noted.) (Note 5)

| PARAMETER                                              | SYMBOL           | CONDITIONS                                                                                                     | MIN | TYP                      | MAX | UNITS |

|--------------------------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------|-----|--------------------------|-----|-------|

| USB Supply Voltage                                     | V <sub>BUS</sub> |                                                                                                                | 4.5 |                          | 5.5 | V     |

| USB PHY Supply Voltage                                 | V <sub>DDB</sub> | V <sub>BUS</sub> ≥4.0V                                                                                         |     | 3.3                      |     | V     |

| V <sub>BUS</sub> Supply Current in LP2/3               |                  | Transmitting on D+ and D- at 12Mbps,<br>C <sub>L</sub> = 50 pF on D+ and D- to V <sub>SS</sub> ,<br>FRCVDD = 0 |     | 3 + I <sub>DD</sub>      |     | mA    |

| While Transmitting USB Data<br>(Note 3)                | IVBUS_TX         | Transmitting on D+ and D- at 12Mbps,<br>C <sub>L</sub> = 50 pF on D+ and D- to GND,<br>FRCVDD = 1              |     | 3                        |     | mA    |

| V <sub>BUS</sub> Supply Current in LP2/3 with USB Idle | IVBUS_IDLE       | D+ = hi, D- = lo, FRCVDD = 18                                                                                  |     | 0.4 +<br>I <sub>DD</sub> |     | mA    |

| Single-Ended Input High Voltage D+, D-                 | V <sub>IHD</sub> |                                                                                                                | 2.0 |                          |     | V     |

| Single-Ended Input Low Voltage D+, D-                  | V <sub>ILD</sub> |                                                                                                                |     |                          | 0.8 | V     |

| Output Low Voltage D+, D-                              | V <sub>OLD</sub> | $R_L = 1.5k\Omega$ from D+ to 3.6V                                                                             |     |                          | 0.3 | V     |

| Output High Voltage D+, D-                             | V <sub>OHD</sub> | $R_L$ = 15k $\Omega$ from D+ and D- to V <sub>SS</sub>                                                         | 2.8 |                          |     | V     |

| Differential Input Sensitivity D+, D-                  | V <sub>DI</sub>  | D+ to D-                                                                                                       | 0.2 |                          |     | V     |

| Common-Mode Voltage Range                              | V <sub>CM</sub>  | Includes V <sub>DI</sub> range                                                                                 | 0.8 |                          | 2.5 | V     |

| Single-Ended Receiver<br>Threshold                     | V <sub>SE</sub>  |                                                                                                                | 0.8 |                          | 2.0 | V     |

| Single-Ended Receiver<br>Hysteresis                    | V <sub>SEH</sub> |                                                                                                                |     | 200                      |     | mV    |

| Differential Output Signal<br>Cross-Point Voltage      | V <sub>CRS</sub> | C <sub>L</sub> = 50pF                                                                                          |     | 1.65                     |     | V     |

| D+, D- Off-State Input<br>Impedance                    | R <sub>LZ</sub>  |                                                                                                                | 300 |                          |     | kΩ    |

# Wellness Measurement Microcontroller

#### **USB Electrical Characteristics**

| PARAMETER                             | SYMBOL                          | CONDITIONS            | MIN   | ТҮР | MAX   | UNITS |

|---------------------------------------|---------------------------------|-----------------------|-------|-----|-------|-------|

| Driver Output Impedance               | R <sub>DRV</sub>                | Steady-state drive    | 28    |     | 44    | Ω     |

| D+ Pullup Resistor                    | <b>D</b>                        | Idle                  | 0.9   |     | 1.575 | kO    |

|                                       | R <sub>PU</sub>                 | Receiving             | 1.425 |     | 3.090 | kΩ    |

| USB TIMING                            |                                 |                       |       |     |       |       |

| D+, D- Rise Time (Transmit)           | t <sub>R</sub>                  | C <sub>L</sub> = 50pF |       | 12  |       | ns    |

| D+, D- Fall Time (Transmit)           | t <sub>F</sub>                  | C <sub>L</sub> = 50pF |       | 12  |       | ns    |

| Rise/Fall Time Matching<br>(Transmit) | t <sub>R</sub> , t <sub>F</sub> | C <sub>L</sub> = 50pF |       | 100 |       | %     |

#### **Clock Electrical Characteristics**

(V<sub>DD</sub> = V<sub>RST</sub> to 3.6V,  $T_A$  = -40°C to +85°C, unless otherwise noted.) (Note 2)

| PARAMETER                                     | SYMBOL                 | CONDITIONS | MIN | TYP               | MAX  | UNITS |

|-----------------------------------------------|------------------------|------------|-----|-------------------|------|-------|

| External Crystal/Clock Input<br>Frequency     | fHFXIN                 |            | 1   |                   | 24   | MHz   |

| External Crystal Duty Cycle                   | tHFX_DUTY              |            |     | 50                |      | %     |

| External Clock Input Duty<br>Cycle            | <sup>t</sup> XCLK_DUTY |            |     | 50                |      | %     |

| System Clock Frequency                        | f <sub>CK</sub>        |            |     |                   | 24.2 | MHz   |

| System Clock Period                           | t <sub>CK</sub>        |            |     | 1/f <sub>CK</sub> |      | ns    |

| Internal Relaxation Oscillator<br>Frequency   | fosc                   |            |     | 24                |      | MHz   |

| Internal Relaxation Oscillator<br>Variability | <sup>f</sup> osc_var   |            |     |                   | ±1%  | MHz   |

### **Phase-Locked Loop (PLL) Electrical Characteristics**

(V<sub>DD</sub> = V<sub>RST</sub> to 3.6V, T<sub>A</sub> = -40°C to +85°C, unless otherwise noted.) (Note 2)

| PARAMETER        | SYMBOL           | CONDITIONS                                             | MIN | TYP | MAX | UNITS |

|------------------|------------------|--------------------------------------------------------|-----|-----|-----|-------|

| Frequency        | f <sub>PLL</sub> | 8MHz, 12MHz, 24MHz with corresponding clock multiplier |     | 48  |     | MHz   |

| Frequency Jitter |                  | Peak-to-peak                                           |     | 1   |     | ns    |

# Wellness Measurement Microcontroller

#### **ADC/PGA Electrical Characteristics**

(V<sub>DD</sub> = V<sub>RST</sub> to 3.6V, V<sub>DDA3</sub> = 2.3V to 3.6V,  $T_A$  = -40°C to +85°C, unless otherwise noted.) (Note 2)

| PARAMETER                 | SYMBOL              | CONDITIONS                                                                                                                                          | MIN                                  | TYP               | MAX                                  | UNITS |

|---------------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|-------------------|--------------------------------------|-------|

| ADC ANALOG INPUT          |                     | ·                                                                                                                                                   | ·                                    |                   |                                      |       |

|                           |                     | Unipolar, AIN+ – AIN-<br>PGA gain = 1, 2, 4, 8                                                                                                      | 0                                    |                   | +V <sub>REFADC</sub> /<br>Gain       | V     |

|                           |                     | Bipolar, AIN+ – AIN- PGA gain = 1,<br>2, 4, 8 range = 0                                                                                             | -V <sub>REFADC</sub> /<br>(2 × Gain) |                   | +V <sub>REFADC</sub> /<br>(2 × Gain) | V     |

| Input Voltage Range       | V <sub>IN</sub>     | Bipolar, AIN+ – AIN- PGA gain = 1,<br>2, 4, 8 range = 1                                                                                             | -V <sub>REFADC/</sub><br>Gain        |                   | +V <sub>REFADC</sub> /<br>Gain       | V     |

| (Note 5)                  |                     | Unipolar, AIN+ – AIN-, PGA bypass                                                                                                                   | 0                                    |                   | +V <sub>REFADC</sub>                 | V     |

|                           |                     | Bipolar, AIN+ - AIN-, PGA bypass,<br>range = 0                                                                                                      | -V <sub>REFADC</sub><br>/2           |                   | +V <sub>REFADC</sub> /<br>2          | v     |

|                           |                     | Bipolar, AIN+ – AIN-, PGA bypass,<br>range = 1                                                                                                      | -V <sub>REFADC</sub>                 |                   | +V <sub>REFADC</sub>                 | V     |

| Common-Mode Input Voltage | V <sub>CM_MIN</sub> | AIN+, AIN-                                                                                                                                          |                                      | 0                 |                                      | v     |

| Range                     | V <sub>CM_MAX</sub> | AIN+, AIN-                                                                                                                                          |                                      | V <sub>DDA3</sub> |                                      |       |

|                           |                     | $T_A = +25^{\circ}C,$<br>AIN0±, AIN[2:7] ± V <sub>IN</sub> = 0V < 2.0V                                                                              |                                      | 1                 |                                      |       |

|                           |                     | $T_A = +50^{\circ}C,$<br>AIN0±, AIN[2:7] ± V <sub>IN</sub> = 0V < 2.0V                                                                              |                                      | 4                 |                                      |       |

|                           |                     | T <sub>A</sub> = +25°C,<br>AIN0±, AIN[2:7] ± V <sub>IN</sub> = 2.0V to 3.6V                                                                         |                                      | 3                 |                                      |       |

|                           |                     | $T_A = +50^{\circ}C$ ,<br>AIN0±, AIN[2:7] ± V <sub>IN</sub> = 2.0V to 3.6V                                                                          |                                      | 8                 |                                      |       |

|                           |                     | $T_A = +25^{\circ}C,$<br>AIN1+, AIN1- ± V <sub>IN</sub> = 0V < 2.0V                                                                                 |                                      | 2                 |                                      |       |

| ADC/PGA Input Leakage     |                     | T <sub>A</sub> = +50°C<br>AIN1+, AIN1- ± V <sub>IN</sub> = 0V < 2.0V                                                                                |                                      | 6                 |                                      |       |

| Current (Note 5)          | Ι <sub>ΙL</sub>     | $T_A = +25^{\circ}C$ ,<br>AIN1+, AIN1- ± V <sub>IN</sub> = 2.0V to 3.6V                                                                             |                                      | 4                 |                                      | pA    |

|                           |                     | $T_A = +50^{\circ}C$ ,<br>AIN1+, AIN1- ± V <sub>IN</sub> = 2.0V to 3.6V                                                                             |                                      | 13                |                                      |       |

|                           |                     | $\label{eq:TA} \begin{array}{l} T_A = -40^\circ \mathrm{C} \text{ to } +85^\circ \mathrm{C},\\ AIN0\pm,  AIN[2:7] \pm V_IN = 0V < 2.0V \end{array}$ |                                      | 1                 | ±200                                 |       |

|                           |                     | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C,$<br>AIN0±, AIN[2:7] ± V <sub>IN</sub> = 2.0V to 3.6V                                                  |                                      | 3                 | ±350                                 |       |

|                           |                     | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C,$<br>AIN1+, AIN1- ± V <sub>IN</sub> = 0V < 2.0V                                                        |                                      | 2                 | ±300                                 |       |

|                           |                     | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C,$<br>AIN1+, AIN1- ± V <sub>IN</sub> = 2.0V to 3.6V                                                     |                                      | 5                 | ±525                                 |       |

# Wellness Measurement Microcontroller

#### **ADC/PGA Electrical Characteristics (continued)**

(V<sub>DD</sub> = V<sub>RST</sub> to 3.6V,  $T_A$  = -40°C to +85°C, unless otherwise noted.) (Note 2)

| PARAMETER                               | SYMBOL            | CONDITIONS                                                              | MIN    | TYP  | MAX                | UNITS      |

|-----------------------------------------|-------------------|-------------------------------------------------------------------------|--------|------|--------------------|------------|

|                                         |                   | PGA bypass, range = 0                                                   |        | 7    |                    |            |

|                                         |                   | PGA bypass, range = 1                                                   |        | 4    |                    |            |

|                                         | 0                 | PGA gain = 1                                                            |        | 7    |                    | ]<br>      |

| Input Capacitance                       | Cl                | PGA gain = 2                                                            |        | 13   |                    | - pF       |

|                                         |                   | PGA gain = 4                                                            |        | 25   |                    |            |

|                                         |                   | PGA gain = 8                                                            |        | 49   |                    | ]          |

| DC CHARACTERISTICS                      |                   |                                                                         |        |      |                    |            |

| Resolution                              | N                 |                                                                         | 16     |      |                    | Bits       |

| No Missing Codes (Note 5)               |                   |                                                                         | -1     |      |                    | LSB        |

| Differential Nonlinearity               | DNL               | 16-bit resolution                                                       |        | ±0.5 |                    | LSB        |

| Integral Nonlinearity (Note 5)          | INL               | V <sub>REFADC</sub> ≥ 1.5V                                              |        | ±1.5 | ±4                 | LSB        |

| Transition Noise                        |                   | PGA bypass                                                              |        | 3.7  |                    | 1.05       |

| Transition Noise                        |                   | PGA gain = 8                                                            |        | 8.1  |                    | - LSB      |

| Gain Error without Firmware             |                   | PGA bypass                                                              |        |      | ±200               |            |

| Compensation                            |                   | PGA active                                                              |        |      | ±225               | - LSB      |

| Gain Error Temperature<br>Coefficient   |                   | $V_{REF} \ge 1.5V$ , does not include reference drift                   |        |      | ±0.4               | LSB/<br>°C |

| Offset Error without Firmware           | 05                | PGA bypass                                                              |        | 0    | ±55                | 1.05       |

| Compensation                            | OE                | PGA active                                                              |        | 0    | 80                 | - LSB      |

| Offset Error Temperature<br>Coefficient |                   | $V_{REF} \ge 1.5V$ , does not include reference drift                   |        | 0.1  |                    | LSB/<br>°C |

| Channel-to-Channel Offset<br>Matching   |                   |                                                                         |        | ±0.1 |                    | LSB        |

| Channel-to-Channel Gain<br>Matching     |                   |                                                                         |        | ±0.1 |                    | LSB        |

| Input Common-Mode<br>Rejection          | CMR               | $V_{CM} = 0V$ to $V_{DDA3}$                                             |        | ±1   |                    | LSB        |

| CONVERSION RATE                         |                   |                                                                         | ·      |      |                    | •          |

|                                         |                   | PGA bypass                                                              |        |      | 500/N <sub>d</sub> |            |

|                                         |                   | PGA gain = 1                                                            |        |      | 470/N <sub>d</sub> | 1          |

| Throughput Rate                         | F <sub>S</sub>    | PGA gain = 2                                                            |        |      | 470/N <sub>d</sub> | ksps       |

|                                         |                   | PGA gain = 4                                                            |        |      | 444/N <sub>d</sub> | ]          |

|                                         |                   | PGA gain = 8                                                            |        |      | 421/N <sub>d</sub> |            |

| Decimation Rate                         | Nd                | Powers of 2 (Note 5)                                                    | 1      |      | 128                | Sp         |

| ADC Conversion Time                     | t <sub>CONV</sub> | 15.5 ADC <sub>FCLK</sub> cycles;<br>ADC <sub>FCLK</sub> = 8MHz (Note 7) | 1.9375 |      |                    | μs         |

# Wellness Measurement Microcontroller

#### **ADC/PGA Electrical Characteristics (continued)**

(V<sub>DD</sub> = V<sub>RST</sub> to 3.6V, T<sub>A</sub> = -40°C to +85°C, unless otherwise noted.) (Note 2)

|                                                                                 | SYMBOL               | CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                            | MIN                                                                   | TYP                                                              | MAX | UNITS        |

|---------------------------------------------------------------------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|------------------------------------------------------------------|-----|--------------|

|                                                                                 |                      | PGA bypass                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 187.5                                                                 |                                                                  |     |              |

|                                                                                 |                      | PGA gain = 1                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 250                                                                   |                                                                  |     |              |

| ADC Acquisition Time                                                            | t <sub>ACQ_ADC</sub> | PGA gain = 2                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 250                                                                   |                                                                  |     | ns           |

|                                                                                 |                      | PGA gain = 4                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 375                                                                   |                                                                  |     |              |

|                                                                                 |                      | PGA gain = 8                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 375                                                                   |                                                                  |     |              |

|                                                                                 |                      | Single sample or initial sample                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0.63                                                                  |                                                                  |     |              |

|                                                                                 |                      | PGA gain = 1, continuous sample                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1.5                                                                   |                                                                  |     |              |

| PGA Acquisition Time                                                            | t <sub>ACQ_PGA</sub> | PGA gain = 2, continuous sample                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1.5                                                                   |                                                                  |     | μs           |

|                                                                                 |                      | PGA gain = 4, continuous sample                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1.5                                                                   |                                                                  |     |              |

|                                                                                 |                      | PGA gain = 8, continuous sample                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1.5                                                                   |                                                                  |     |              |

| Anorturo littor                                                                 |                      | External crystal or clock source                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                       | 500                                                              |     |              |

| Aperture Jitter                                                                 | t <sub>AJ</sub>      | Internal relaxation oscillator                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                       | 500                                                              |     | ps           |

| ADC Clock Frequency                                                             |                      | (Note 5)                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                       |                                                                  | 8   | MHz          |

| Transient Response                                                              |                      | Full-scale step                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                       |                                                                  | 1   | CLK<br>cycle |

|                                                                                 | 1                    | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1                                                                     |                                                                  |     |              |

|                                                                                 |                      | Rypass mode                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                       |                                                                  |     |              |

| Signal-to-Noise Ratio                                                           |                      | Bypass mode,<br>decimation filter $N_d = 1$<br>Decimation filter $N_d = 1$ ,                                                                                                                                                                                                                                                                                                                                                                                          | 72.4                                                                  | 74.8                                                             |     | _            |

| Signal-to-Noise Ratio<br>(Note 9)                                               | SNR                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 72.4                                                                  | 74.8<br>73.6                                                     |     |              |

| -                                                                               | SNR                  | decimation filter $N_d = 1$<br>Decimation filter $N_d = 1$ ,                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                       | -                                                                |     |              |

| -                                                                               | SNR                  | decimation filter $N_d = 1$<br>Decimation filter $N_d = 1$ ,<br>PGA enabled                                                                                                                                                                                                                                                                                                                                                                                           | 70.8                                                                  | 73.6                                                             |     | dB           |

| -                                                                               | SNR                  | decimation filter $N_d = 1$<br>Decimation filter $N_d = 1$ ,<br>PGA enabled<br>Decimation filter $N_d = 16$                                                                                                                                                                                                                                                                                                                                                           | 70.8                                                                  | 73.6<br>85.4                                                     |     |              |

| -                                                                               | SNR                  | decimation filter $N_d = 1$ Decimation filter $N_d = 1$ ,<br>PGA enabledDecimation filter $N_d = 16$ Decimation filter $N_d = 64$ Bypass mode,                                                                                                                                                                                                                                                                                                                        | 70.8<br>80.3<br>84.6                                                  | 73.6<br>85.4<br>89.9                                             |     | dB           |

| (Note 9)<br>Signal-to-Noise and                                                 |                      | $\begin{array}{l} \mbox{decimation filter } N_{d} = 1 \\ \mbox{Decimation filter } N_{d} = 1, \\ \mbox{PGA enabled} \\ \mbox{Decimation filter } N_{d} = 16 \\ \mbox{Decimation filter } N_{d} = 64 \\ \mbox{Bypass mode,} \\ \mbox{decimation filter } N_{d} = 1 \\ \mbox{Decimation filter } N_{d} = 1, \end{array}$                                                                                                                                                | 70.8<br>80.3<br>84.6<br>72.2                                          | 73.6<br>85.4<br>89.9<br>74.7                                     |     | dB           |

| (Note 9)<br>Signal-to-Noise and                                                 |                      | $\begin{array}{l} \mbox{decimation filter } N_d = 1 \\ \mbox{Decimation filter } N_d = 1, \\ \mbox{PGA enabled} \\ \mbox{Decimation filter } N_d = 16 \\ \mbox{Decimation filter } N_d = 64 \\ \mbox{Bypass mode,} \\ \mbox{decimation filter } N_d = 1 \\ \mbox{Decimation filter } N_d = 1, \\ \mbox{PGA enabled} \end{array}$                                                                                                                                      | 70.8       80.3       84.6       72.2       70.7                      | 73.6<br>85.4<br>89.9<br>74.7<br>73.5                             |     | dB           |

| (Note 9)<br>Signal-to-Noise and<br>Distortion                                   | SINAD                | decimation filter $N_d = 1$ Decimation filter $N_d = 1$ ,<br>PGA enabledDecimation filter $N_d = 16$ Decimation filter $N_d = 64$ Bypass mode,<br>decimation filter $N_d = 1$ Decimation filter $N_d = 1$ ,<br>PGA enabledDecimation filter $N_d = 1$ ,<br>PGA enabledDecimation filter $N_d = 16$                                                                                                                                                                    | 70.8         80.3         84.6         72.2         70.7         78.6 | 73.6<br>85.4<br>89.9<br>74.7<br>73.5<br>84.5                     |     | _            |

| (Note 9)<br>Signal-to-Noise and<br>Distortion<br>Spurious-Free Dynamic          |                      | $decimation filter N_d = 1$ $Decimation filter N_d = 1,$ $PGA enabled$ $Decimation filter N_d = 16$ $Decimation filter N_d = 64$ $Bypass mode,$ $decimation filter N_d = 1$ $Decimation filter N_d = 1,$ $PGA enabled$ $Decimation filter N_d = 16$ $Decimation filter N_d = 64$                                                                                                                                                                                      | 70.8         80.3         84.6         72.2         70.7         78.6 | 73.6<br>85.4<br>89.9<br>74.7<br>73.5<br>84.5<br>87.9             |     | dB           |

| (Note 9)<br>Signal-to-Noise and<br>Distortion<br>Spurious-Free Dynamic<br>Range | SINAD                | $\label{eq:second} \begin{array}{l} \mbox{decimation filter } N_d = 1 \\ \mbox{Decimation filter } N_d = 1, \\ \mbox{PGA enabled} \\ \mbox{Decimation filter } N_d = 16 \\ \mbox{Decimation filter } N_d = 64 \\ \mbox{Bypass mode,} \\ \mbox{decimation filter } N_d = 1, \\ \mbox{PGA enabled} \\ \mbox{Decimation filter } N_d = 16 \\ \mbox{Decimation filter } N_d = 64 \\ \mbox{PGA bypass} \end{array}$                                                        | 70.8         80.3         84.6         72.2         70.7         78.6 | 73.6<br>85.4<br>89.9<br>74.7<br>73.5<br>84.5<br>87.9<br>91       |     |              |

| (Note 9)<br>Signal-to-Noise and                                                 | SINAD                | $\label{eq:second} \begin{array}{l} \mbox{decimation filter $N_d$ = 1$} \\ \mbox{Decimation filter $N_d$ = 1$,} \\ \mbox{PGA enabled} \\ \mbox{Decimation filter $N_d$ = 16$} \\ \mbox{Decimation filter $N_d$ = 1$} \\ \mbox{Decimation filter $N_d$ = 1$,} \\ \mbox{PGA enabled} \\ \mbox{Decimation filter $N_d$ = 16$} \\ \mbox{Decimation filter $N_d$ = 16$} \\ \mbox{Decimation filter $N_d$ = 64$} \\ \mbox{PGA bypass} \\ \mbox{PGA enabled} \\ \end{array}$ | 70.8         80.3         84.6         72.2         70.7         78.6 | 73.6<br>85.4<br>89.9<br>74.7<br>73.5<br>84.5<br>87.9<br>91<br>85 |     | _            |

# Wellness Measurement Microcontroller

#### **ADC/PGA Electrical Characteristics (continued)**

(V<sub>DD</sub> = V<sub>RST</sub> to 3.6V,  $T_A$  = -40°C to +85°C, unless otherwise noted.) (Note 2)

| PARAMETER          | SYMBOL | CONDITIONS                                              | MIN  | ТҮР  | MAX      | UNITS |  |  |  |

|--------------------|--------|---------------------------------------------------------|------|------|----------|-------|--|--|--|

| POWER SUPPLIES     |        |                                                         |      |      |          |       |  |  |  |

| ADC Supply Current |        | F <sub>S</sub> > 333.3ksps, PGA bypass, post trimmed    |      | 9.6  |          |       |  |  |  |

|                    |        | F <sub>S</sub> > 333.3ksps, PGA enabled, post trimmed   |      | 11.6 |          | - mA  |  |  |  |

|                    |        | F <sub>S</sub> ≤ 333.3ksps, PGA bypass,<br>post trimmed |      | 32.9 |          |       |  |  |  |

|                    |        | $F_S \le 333.3$ ksps, PGA enabled, 40.9 post trimmed    | 40.9 |      | — nA/sps |       |  |  |  |

| Line Rejection     | LR     | V <sub>DDA3</sub> = 2.3 to 3.6V (Note 5)                |      |      | ±10      | LSB   |  |  |  |

**DAC0/DAC1 Electrical Characteristics** ( $V_{DDA3}$  = 2.3V to 3.6V,  $V_{DD}$  =  $V_{RST}$  to 3.6V,  $R_L$  = 10k $\Omega$  and  $C_L$  = 100pF,  $T_A$  = -40°C to +85°C,  $V_{REFDAC}$  = 1.5V, unless otherwise noted.) (Note 2)

| PARAMETER                              | SYMBOL           | CONDITIONS                                                                                                                                                         | MIN                                    | TYP  | MAX                                         | UNITS |  |

|----------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|------|---------------------------------------------|-------|--|

| Resolution                             | DACR             | Guaranteed monotonic                                                                                                                                               | 12                                     |      |                                             | Bits  |  |

| Differential Nonlinearity              | DNL              | Power mode = 2 or 3, noise filter<br>enabled, $T_A = -0^{\circ}C$ to +85°C, code<br>000h to FFFh (Note 5)                                                          | -2                                     |      | +2                                          | LSB   |  |

| Integral Nonlinearity                  | INL              | Power mode = 2 or 3, noise filter<br>enabled, code 073h to F8Dh<br>(Note 5)                                                                                        | -4                                     |      | +4                                          | LSB   |  |

| Offset Error                           | EO               | Using uncommitted op amp (Note 5)                                                                                                                                  |                                        | ±0.5 | ±4                                          | mV    |  |

| Gain Error                             | E <sub>G</sub>   | $V_{REFDAC}$ = 1.5V, power mode = 2<br>to 3, $V_{DDA3}$ = 3.0V, trimmed, using<br>firmware compensation                                                            | -8                                     | ±1   | +8                                          | LSB   |  |

|                                        |                  | $V_{\text{REFDAC}}$ = 1.5V, $V_{\text{DDA3}}$ = 3.0V,<br>without firmware compensation                                                                             | -90                                    |      | +90                                         |       |  |

| Gain Error Temperature<br>Compensation |                  | Temperature coefficient<br>compensation disabled, using<br>internal uncommitted op amp,<br>V <sub>REFDAC</sub> = 1.5V, power mode = 3,<br>V <sub>DDA3</sub> = 3.0V |                                        | -60  |                                             | ppm/° |  |

|                                        | E <sub>GTC</sub> | Temperature coefficient<br>compensation enabled, using<br>internal uncommitted op amp,<br>$V_{REFDAC} = 1.5V$ , power mode = 3,<br>$V_{DDA3} = 3.0V$               |                                        | -20  |                                             | C C   |  |

| Output Voltage Range                   | Vo               | Min code to max code (Note 5)                                                                                                                                      | V <sub>SSDAC</sub> +<br>E <sub>O</sub> |      | V <sub>DDA3</sub> -<br>0.5 + E <sub>G</sub> | V     |  |

# Wellness Measurement Microcontroller

#### **DAC0/DAC1 Electrical Characteristics (continued)**

$(V_{DDA3} = 2.3V \text{ to } 3.6V, V_{DD} = V_{RST} \text{ to } 3.6V, R_L = 10k\Omega \text{ and } C_L = 100pF, T_A = -40^{\circ}C \text{ to } +85^{\circ}C, V_{REFDAC} = 1.5V, \text{ unless otherwise noted.})$  (Note 2)

| PARAMETER                    | SYMBOL             | CONDITIONS                                                                    | MIN | TYP   | MAX  | UNITS  |  |

|------------------------------|--------------------|-------------------------------------------------------------------------------|-----|-------|------|--------|--|

|                              |                    | Power mode = 3                                                                |     | 6.1   |      | kΩ     |  |

| Output Impodence             |                    | Power mode = 2                                                                |     | 8.9   |      | kΩ     |  |

| Output Impedance             |                    | Power mode = 1                                                                |     | 16.3  |      | kΩ     |  |

|                              |                    | Power mode = 0                                                                |     | 97.7  |      | kΩ     |  |

| Voltage Output Settling Time | +                  | Noise filter enabled, code 400h to C00h, rising or falling, to $\pm 0.5$ LSB  |     |       | 4    |        |  |

| Voltage Output Setting Time  | tsfs               | Noise filter disabled, code 400h to C00h, rising or falling, to $\pm 0.5$ LSB |     |       | 0.03 | — ms   |  |

|                              |                    | Power mode = 0, 1, or 2                                                       |     | 12    |      |        |  |

| Glitch Energy                |                    | Power mode = 3,                                                               |     | 12    |      | V x ns |  |

| Bias Supply Current Shared   |                    | code 000h to A5Hh<br>Static<br>V <sub>REF</sub> = 2.5V                        |     | 110   |      |        |  |

|                              | IDACx_ON           | Static<br>V <sub>REF</sub> = 1.5V                                             |     | 82    |      | — μΑ   |  |

|                              | I <sub>DAC12</sub> | Static<br>V <sub>REF</sub> = 2.5V<br>Power mode = 3                           |     | 438.7 |      | μΑ     |  |

| Active Current               |                    | Static<br>V <sub>REF</sub> = 2.5V<br>Power mode = 2                           |     | 301.6 |      |        |  |

| Active Current               |                    | Static<br>V <sub>REF</sub> = 2.5V<br>Power mode = 1                           |     | 164.5 |      |        |  |

|                              |                    | Static<br>V <sub>REF</sub> = 2.5V<br>Power mode = 0                           |     | 27.4  |      |        |  |

|                              |                    | Static<br>V <sub>REF</sub> = 1.5V<br>Power mode = 3                           |     | 263.2 |      |        |  |

| Active Current               |                    | Static<br>V <sub>REF</sub> = 1.5V<br>Power mode = 2                           |     | 181   |      | μA     |  |

| Active Current               | IDAC12             | Static<br>V <sub>REF</sub> = 1.5V<br>Power mode = 1                           |     | 98.7  |      |        |  |

|                              |                    | Static<br>V <sub>REF</sub> = 1.5V<br>Power mode = 0                           |     | 16.5  |      |        |  |

# Wellness Measurement Microcontroller

#### **DAC0/DAC1 Electrical Characteristics (continued)**

$(V_{DDA3} = 2.3V \text{ to } 3.6V, V_{DD} = V_{RST} \text{ to } 3.6V, R_L = 10k\Omega \text{ and } C_L = 100pF, T_A = -40^{\circ}C \text{ to } +85^{\circ}C, V_{REFDAC} = 1.5V, \text{ unless otherwise noted.})$  (Note 2)

| PARAMETER      | SYMBOL | CONDITIONS                                            | MIN TYP | MAX | UNITS |  |

|----------------|--------|-------------------------------------------------------|---------|-----|-------|--|

| Active Current |        | Static<br>V <sub>REF</sub> = 2.048V<br>Power mode = 3 | 359.3   |     |       |  |

|                |        | Static<br>V <sub>REF</sub> = 2.048V<br>Power mode = 2 | 247.1   |     |       |  |

|                | IDAC12 | Static<br>V <sub>REF</sub> = 2.048V<br>Power mode = 1 | 124.8   |     | — μΑ  |  |

|                |        | Static<br>V <sub>REF</sub> = 2.048V<br>Power mode = 0 | 22.5    |     |       |  |

|                |        | Static<br>V <sub>REF</sub> = 1.024V<br>Power mode = 3 | 179.7   |     |       |  |

| Astive Current |        | Static<br>V <sub>REF</sub> = 1.024V<br>Power mode = 2 | 123.5   |     |       |  |

| Active Current | IDAC12 | Static<br>V <sub>REF</sub> = 1.024V<br>Power mode = 1 | 67.3    |     | Αμ —  |  |

|                |        | Static<br>V <sub>REF</sub> = 1.024V<br>Power mode = 0 | 11.2    |     |       |  |

| Power-On Time  |        | Excluding reference                                   | 10      |     | μs    |  |

# Wellness Measurement Microcontroller

#### **DAC2/DAC3 Electrical Characteristics**

$(V_{DDA3} = 2.3V \text{ to } 3.6V, V_{DD} = V_{RST} \text{ to } 3.6V, R_{L} = 10k\Omega \text{ and } C_{L} = 100pF, T_{A} = -40^{\circ}C \text{ to } +85^{\circ}C, V_{REFDAC} = 1.5V$ , unless otherwise noted.) (Note 2)

| PARAMETER                             | SYMBOL | CONDITIONS                                                             | MIN                | ТҮР   | MAX                        | UNITS            |

|---------------------------------------|--------|------------------------------------------------------------------------|--------------------|-------|----------------------------|------------------|

| Resolution                            | DACR   | Guaranteed monotonic                                                   | 8                  |       |                            | Bits             |

| Differential Nonlinearity             | DNL    | Code 07h to F9h                                                        |                    | ±0.25 | ±1                         | LSB              |

| Integral Nonlinearity                 | INL    | Code 07h to F9h                                                        |                    | ±0.25 | ±1                         | LSB              |

| Offset Error                          | EO     | Internal uncommitted op amp<br>(Note 5)                                |                    | ±0.5  | ±4                         | mV               |

| Gain Error                            | EG     | Internal reference                                                     |                    | ±2    |                            | LSB              |

| Gain-Error Temperature<br>Coefficient |        | Excludes offset and reference drift, using internal uncommitted op amp |                    | ±5    |                            | ppm of<br>FSR/°C |

| Output Voltage Range                  | Vo     | Min code to max code (Note 5)                                          | V <sub>SSDAC</sub> |       | V <sub>DDA3</sub> -<br>0.5 | V                |

| Output Impedance                      |        |                                                                        |                    | 49    |                            | kΩ               |

| Voltage Output Settling Time          | tSFS   | 40h to C0h code swing rising or falling to $\pm 0.5$ LSB               |                    | 3     |                            | μs               |

| DAC Glitch Impulse                    |        | Major carry transitions                                                |                    | 12    |                            | nV-s             |

| Supply Current per DAC                | IDAC   | Static                                                                 |                    | 62.4  |                            | μA               |

| Power-On Time                         |        | Excluding Reference                                                    |                    | 10    |                            | μs               |

#### **Operational Amplifier Electrical Characteristics**

(V<sub>DDA3</sub> = 2.3V to 3.6V,  $T_A$  = -40°C to +85°C, unless otherwise noted.) (Note 2)

| PARAMETER                      | SYMBOL                              | CONDITIONS                                                   | MIN                         | TYP  | MAX                         | UNITS |

|--------------------------------|-------------------------------------|--------------------------------------------------------------|-----------------------------|------|-----------------------------|-------|

| DC CHARACTERISTICS             |                                     |                                                              |                             |      |                             |       |

| Common-Mode Rejection<br>Ratio | CMRR                                | 16-bit resolution                                            |                             | 75   |                             | dB    |

| Input Offset Voltage           | V <sub>OS</sub>                     |                                                              |                             | ±0.5 | ±8                          | mV    |

| Input Offset Voltage Drift     | VOSDRIFT                            |                                                              |                             | 5    |                             | µV/°C |

| Input Bias Current (Note 5)    |                                     | T <sub>A</sub> = +25°C, V <sub>IN</sub> = 0V                 |                             | 15   | 200                         |       |

|                                | I <sub>BIAS</sub>                   | $T_{A} = 0^{\circ}C \text{ to } +50^{\circ}C, V_{IN} = 0V$   |                             |      | 300                         | рА    |

|                                |                                     | $T_{A} = -40^{\circ}C \text{ to } +85^{\circ}C, V_{IN} = 0V$ |                             |      | 650                         |       |

|                                | I <sub>OS</sub>                     | T <sub>A</sub> = +25°C                                       |                             | 15   | 200                         | рА    |

| Input Offset Current (Note 5)  |                                     | $T_A = 0^{\circ}C$ to +50°C                                  |                             |      | 300                         |       |

|                                |                                     | T <sub>A</sub> = -40°C to +85°C                              |                             |      | 650                         |       |