#

## **16-Channel, Linear, High-Voltage** Analog Switches

### **General Description**

### **Features**

The MAX4968/MAX4968A are 16-channel, high-linearity, high-voltage, bidirectional SPST analog switches with  $18\Omega$  (typ) on-resistance. The devices are ideal for use in applications requiring high-voltage switching controlled by a low-voltage control signal, such as ultrasound imaging and printers. The MAX4968A provides integrated  $40k\Omega$  (typ) bleed resistors on each switch terminal to discharge capacitive loads. Using HVCMOS technology, these switches combine high-voltage bilateral MOS switches and low-power CMOS logic to provide efficient control of high-voltage analog signals.

The MAX4968 is pin-to-pin compatible with the MAX14802 and Supertex HV2601. The MAX4968A is pin-to-pin compatible with the MAX14803 and Supertex HV2701. The only difference is the VPP positive supply voltage level. The MAX4968/MAX4968A require a low +10V (typ) voltage (VPP), whereas the MAX14802/MAX14803 and HV2601/HV2701 require a high +100V supply voltage.

In a typical ultrasound application, these devices do not require a dedicated high-voltage supply that implies a significant simplification of system requirement. The negative voltage supply can be shared with the transmitter, and the positive voltage supply is typically +10V.

The devices are available in the 48-pin LQFP package and are specified over the -40°C to +85°C extended temperature range.

### **Applications**

Medical Ultrasound Imaging Nondestructive Testing (NDT)/Industrial Ultrasound Imaging Printers

- Latch Free SOI HVCMOS Process Technology for High Performance and Robustness

- No Dedicated High-Voltage Supplies Required

- ♦ RON Flatness Guaranteed in Entire Input Range

- Low-Power Dissipation

- Low-Charge Injection and Voltage Spike

- ♦ 25MHz Serial Interface (+2.5V to +5V)

- 2nd Harmonic Distortion < -45dB at 2MHz ± 90V Pulse

- Low Parasitic Capacitance Guarantees High Bandwidth

- DC to 30MHz Small-Signal Analog Bandwidth (CLOAD = 200pF)

- 500kHz to 20MHz High-Signal Analog Bandwidth (CLOAD = 200pF)

- Extended Input Range Up to 210VP-P

- -80dB (typ) Off-Isolation at 5MHz (50Ω)

- Shunt (Bleed) Resistors on Outputs (MAX4968A Only)

- Daisy-Chainable Serial Interface

### **Ordering Information/Selector Guide**

| PART         | TEMP RANGE     | SWITCH CHANNELS | BLEED RESISTOR | PIN-PACKAGE |

|--------------|----------------|-----------------|----------------|-------------|

| MAX4968ECM+  | -40°C to +85°C | 16              | No             | 48 LQFP     |

| MAX4968AECM+ | -40°C to +85°C | 16              | Yes            | 48 LQFP     |

+Denotes a lead(Pb)-free/RoHS-compliant package.

####

Maxim Integrated Products 1

Yes 48 LQFP

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

### **ABSOLUTE MAXIMUM RATINGS**

(All voltages referenced to GND.)

| V <sub>DD</sub> Logic Supply Vo              | Itage Range           | 0.3V to +6V  |

|----------------------------------------------|-----------------------|--------------|

| V <sub>PP</sub> - V <sub>NN</sub> Supply Vol | ltage                 | +212V        |

| V <sub>PP</sub> Supply Voltage F             | Range                 | 0.3V to +12V |

| V <sub>NN</sub> Negative Supply              | Voltage               | 200V         |

| Logic Input Voltage F                        | Range (CLK, DIN, CLR) | 0.3V to +6V  |

| Logic Input Voltage F                        | Range                 |              |

|                                              | 0.01/1                |              |

(LE).....-0.3V to a minimum of (V<sub>PP</sub> + 0.3V) or 6V Logic Output Voltage Range (DOUT).....-0.3V to (V<sub>DD</sub> + 0.3V) Analog Signal Range (SW\_) ...... (V<sub>NN</sub> - 0.3V) to (V<sub>NN</sub> + 220V) Continuous Power Dissipation (T<sub>A</sub> = +70°C)

| LQFP (derate 22.7mW/°C above +70°C) | 1818mW         |

|-------------------------------------|----------------|

| Operating Temperature Range         | 40°C to +85°C  |

| Storage Temperature Range           | 65°C to +150°C |

| Junction Temperature                | +150°C         |

| Lead Temperature (soldering, 10s)   | +300°C         |

| Soldering Temperature (reflow)      | +260°C         |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### PACKAGE THERMAL CHARACTERISTICS (Note 1)

LQFP

Junction-to-Ambient Thermal Resistance ( $\theta_{JA}$ ).......44°C/W Junction-to-Case Thermal Resistance ( $\theta_{JC}$ )......10°C/W

Note 1: Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a fourlayer board. For detailed information on package thermal considerations, refer to <u>www.maxim-ic.com/thermal-tutorial</u>.

### **ELECTRICAL CHARACTERISTICS**

$(V_{DD} = +2.37V \text{ to } +5.5V, V_{PP} = +10V \pm 5\%, V_{NN} = 0 \text{ to } -200V, T_A = T_{MIN} \text{ to } T_{MAX}$ , unless otherwise noted. Typical values are  $V_{DD} = +3.3V$ ,  $V_{NN} = -100V$ ,  $V_{PP} = +10V$  at  $T_A = +25^{\circ}C$ .) (Note 2)

| PARAMETER                                                                            | SYMBOL            | CONDITIONS                                                                          | MIN             | ТҮР | MAX                      | UNITS |

|--------------------------------------------------------------------------------------|-------------------|-------------------------------------------------------------------------------------|-----------------|-----|--------------------------|-------|

| POWER SUPPLIES                                                                       |                   |                                                                                     |                 |     |                          |       |

| V <sub>DD</sub> Logic Supply Voltage                                                 | VDD               |                                                                                     | +2.37           |     | +5.5                     | V     |

| V <sub>NN</sub> Supply Voltage                                                       | VNN               |                                                                                     | -200            |     | 0                        | V     |

| VPP Supply Voltage                                                                   | VPP               |                                                                                     | +9.5            | +10 | +10.5                    | V     |

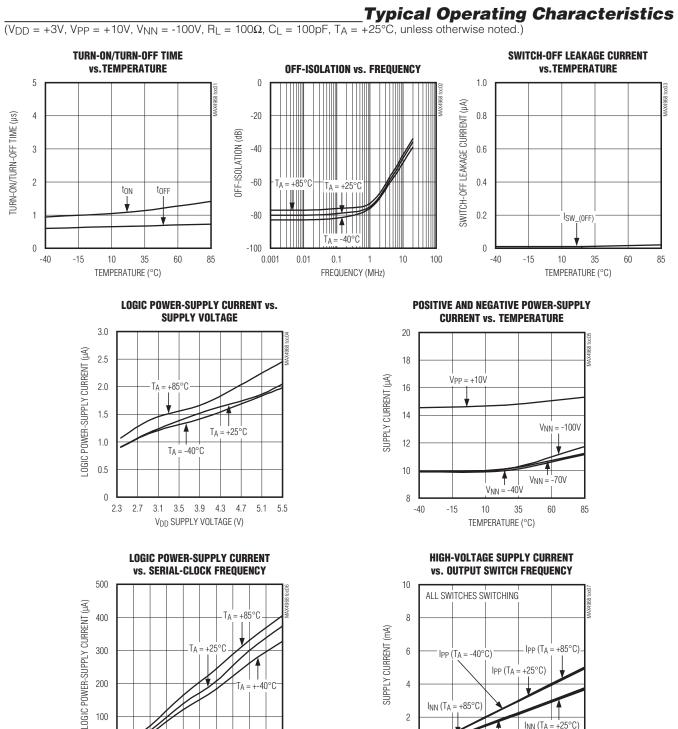

| V <sub>DD</sub> Static Current                                                       | IDDS              |                                                                                     |                 |     | 4                        | μA    |

| V <sub>DD</sub> Dynamic Current                                                      | IDD               | $V_{DD} = +5V$ , $f_{CLK} = 5MHz$ , $f_{DIN} = 2.5MHz$                              |                 |     | 200                      | μA    |

| V <sub>NN</sub> Static Current                                                       | INNS              | All switches remain on or off, SW_ = GND                                            |                 | 10  | 25                       | μA    |

| V <sub>NN</sub> Supply Dynamic Current<br>(All Channels Switching<br>Simultaneously) | I <sub>NN</sub>   | VPP = +10V, VNN = -100V,<br>fTURN_ON/OFF = 50kHz, SW_ = GND                         |                 | 3.3 | 5                        | mA    |

| VPP Supply Static Current                                                            | IPPS              | All switches remain on or off, SW_ = GND                                            |                 | 12  | 25                       | μΑ    |

| VPP Supply Dynamic Current<br>(All Channels Switching<br>Simultaneously)             | IPP               | VPP = +10V, VNN = -100V,<br>fTURN_ON/OFF = 50kHz, SW_ = GND                         |                 | 4   | 6                        | mA    |

| SWITCH CHARACTERISTICS                                                               |                   | ·                                                                                   |                 |     |                          |       |

| Analog Dynamic Signal Range                                                          | V <sub>SW</sub> _ | AC operation only, f > 500kHz                                                       | V <sub>NN</sub> |     | V <sub>NN</sub> +<br>210 | V     |

| Small-Signal On-Resistance                                                           | Rons              | VPP = +10V, V <sub>NN</sub> = -100V, V <sub>SW</sub> = 0V,<br>I <sub>SW</sub> = 5mA |                 | 18  | 34                       | Ω     |

### ELECTRICAL CHARACTERISTICS (continued)

(VDD = +2.37V to +5.5V, VPP = +10V  $\pm$ 5%, VNN = 0 to -200V, TA = TMIN to TMAX, unless otherwise noted. Typical values are VDD = +3.3V, VNN = -100V, VPP = +10V at TA = +25°C.) (Note 2)

| PARAMETER                                | SYMBOL                | CONDITIONS                                                                                                                                                     | MIN                       | TYP | MAX  | UNITS |

|------------------------------------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|-----|------|-------|

| Small-Signal On-Resistance<br>Matching   | ΔR <sub>ONS</sub>     | VPP = +10V, V <sub>NN</sub> = -100V, I <sub>SW</sub> = 5mA                                                                                                     |                           | 3   |      | %     |

| Small-Signal On-Resistance<br>Flatness   | Ronf                  | AC measured, $f_{SW}$ = 0.5MHz,<br>V <sub>SW</sub> = 80V <sub>P-P</sub> , R <sub>LOAD</sub> = 50 $\Omega$ , V <sub>PP</sub> = +10V,<br>V <sub>NN</sub> = -100V |                           | 2   |      | %     |

| Switch Output Bleed Resistor             | RINT                  | MAX4968A only                                                                                                                                                  | 30                        | 40  | 50   | kΩ    |

| Switch-Off Leakage                       | ISW_(OFF)             | Vsw_ = 0V, switch off (MAX4968 only)                                                                                                                           |                           | 0   | 1    | μA    |

| Switch-Off DC Offset                     |                       | No load (MAX4968A only)                                                                                                                                        | -15                       | 0   | +15  | mV    |

| Switch-On DC Offset                      |                       | No load (MAX4968A only)                                                                                                                                        | -15                       | 0   | +15  | mV    |

| Switch Output Isolation Diode<br>Current |                       | 300ns pulse width, 2% duty cycle                                                                                                                               |                           | 3.0 |      | А     |

| SWITCH DYNAMIC CHARACTEI                 | RISITICS              |                                                                                                                                                                |                           |     |      |       |

| Turn-On Time                             | ton                   | $V_{SW_A} = +1V$ , $R_L = 100\Omega$ , $V_{NN} = -100V$ ,<br>from enable to $V_{SW_B} = +0.9V$                                                                 |                           | 2   | 5    | μs    |

| Turn-Off Time                            | tOFF                  | $V_{SW}A = +1V$ , $R_L = 100\Omega$ , $V_{NN} = -100V$ ,<br>from disable to $V_{SW}B = +0.9V$                                                                  |                           | 2   | 3.5  | μs    |

| Maximum V <sub>SW</sub> _Slew Rate       | dV/dt                 | CL = 100pF                                                                                                                                                     | 20                        |     |      | V/ns  |

| Off-Isolation                            | Viso                  | $f = 2MHz, R_L = 50\Omega$                                                                                                                                     |                           | -76 |      | dB    |

| Crosstalk                                | VCT                   | $f = 5MHz, R_L = 50\Omega$                                                                                                                                     |                           | -76 |      | dB    |

| SW_ Off-Capacitance                      | CSW_(OFF)             | f = 1MHz, small signal close to zero                                                                                                                           |                           | 9   |      | рF    |

| SW_ On-Capacitance                       | C <sub>SW_</sub> (ON) | f = 1MHz, small signal close to zero                                                                                                                           |                           | 13  |      | рF    |

| Output Voltage Spike                     | VSPK                  | $R_L = 50\Omega$                                                                                                                                               |                           | ±70 |      | mV    |

| Large-Signal Analog Bandwidth<br>(-3dB)  | fBW_L                 | C <sub>LOAD</sub> = 200pF, 60V amplitude sinusoidal<br>burst, 1% duty cycle                                                                                    |                           | 30  |      | MHz   |

| Small-Signal Analog Bandwidth<br>(-3dB)  | fBW_S                 | C <sub>LOAD</sub> = 200pF, 100mV amplitude<br>sinusoidal                                                                                                       |                           | 50  |      | MHz   |

| Charge Injection                         | Q                     | VPP = +10V, V <sub>NN</sub> = -100V, Figure 1                                                                                                                  |                           | 150 |      | рС    |

| LOGIC LEVELS                             |                       |                                                                                                                                                                |                           |     |      |       |

| Logic-Input Low Voltage                  | VIL                   |                                                                                                                                                                |                           |     | 0.75 | V     |

| Logic-Input High Voltage                 | VIH                   |                                                                                                                                                                | V <sub>DD</sub> -<br>0.75 |     |      | V     |

| Logic-Output Low Voltage                 | Vol                   | ISINK = 1mA                                                                                                                                                    |                           |     | 0.4  | V     |

| Logic-Output High Voltage                | VOH                   | ISOURCE = 1mA                                                                                                                                                  | VDD -<br>0.4              |     |      | V     |

| Logic-Input Capacitance                  | CIN                   |                                                                                                                                                                |                           | 5   |      | pF    |

| Logic-Input Leakage                      | IIN                   |                                                                                                                                                                | -1                        |     | +1   | μA    |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = +2.37V \text{ to } +5.5V, V_{PP} = +10V \pm 5\%, V_{NN} = 0 \text{ to } -200V, T_A = T_{MIN} \text{ to } T_{MAX}$ , unless otherwise noted. Typical values are  $V_{DD} = +3.3V$ ,  $V_{NN} = -100V$ ,  $V_{PP} = +10V$  at  $T_A = +25^{\circ}C$ .) (Note 2)

| PARAMETER               | SYMBOL     | CONDITIONS                                   | MIN | TYP | MAX | UNITS |

|-------------------------|------------|----------------------------------------------|-----|-----|-----|-------|

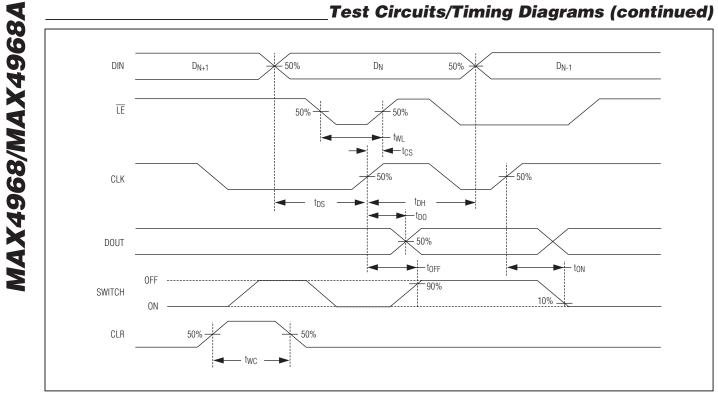

| TIMING CHARACTERISTICS  | (Figure 2) |                                              |     |     |     |       |

| CLK Frequency           | fCLK       |                                              |     |     | 25  | MHz   |

| DIN to CLK Setup Time   | tDS        |                                              | 8   |     |     | ns    |

| DIN to CLK Hold Time    | tDН        |                                              | 3   |     |     | ns    |

| CLK to LE Setup Time    | tCS        |                                              | 8   |     |     | ns    |

| LE Low Pulse Width      | twL        |                                              | 12  |     |     | ns    |

| CLR High Pulse Width    | twc        |                                              | 12  |     |     | ns    |

| CLK Rise and Fall Times | tR, tF     |                                              |     |     | 50  | ns    |

|                         | tao        | $V_{DD} = +5V \pm 10\%, C_{DOUT} = 15pF$     |     |     | 28  |       |

| CLK to DOUT Delay       | tDO        | $V_{DD} = +2.5V \pm 5\%$ , $C_{DOUT} = 15pF$ |     |     | 45  | ns    |

Note 2: All devices are 100% tested at  $T_A = +85^{\circ}C$ . Limits over the operating temperature range are guaranteed by design.

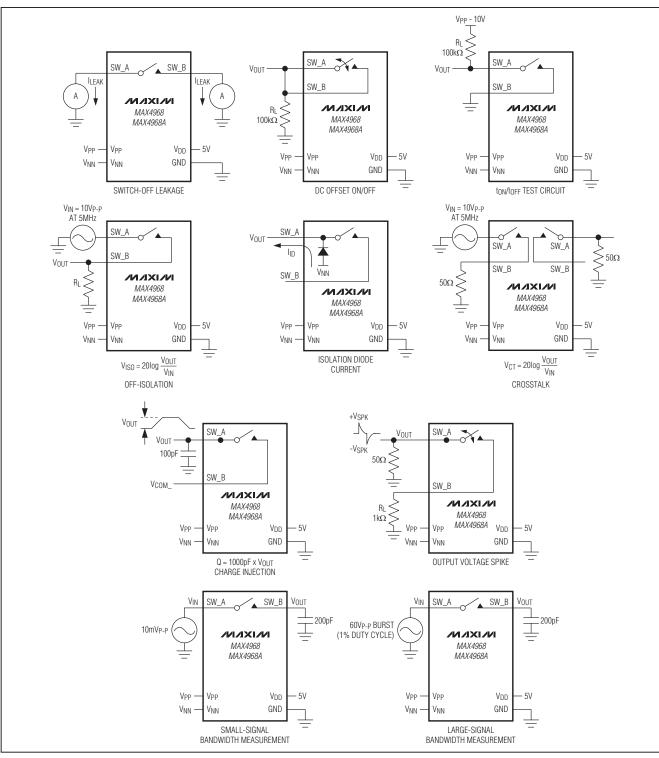

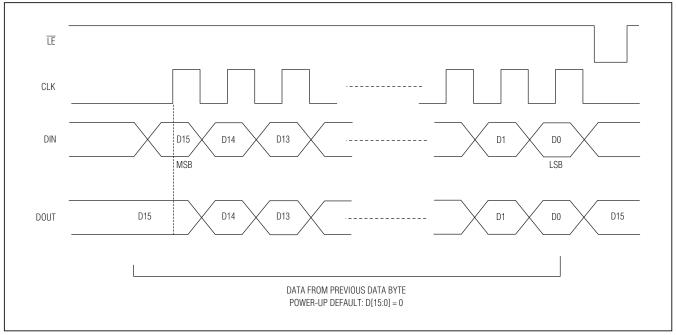

### Test Circuits/Timing Diagrams

Figure 1. Test Circuits

5

MAX4968/MAX4968A

Figure 2. Serial Interface Timing

Figure 3. Latch-Enable Interface Timing

6 8 10 12 14 16

SERIAL-CLOCK FREQUENCY(MHz)

INN (TA =

$I_{NN}$  (T<sub>A</sub> = -40°C)

OUTPUT SWITCH FREQUENCY (kHz)

+25°C)

MAX4968/MAX4968A

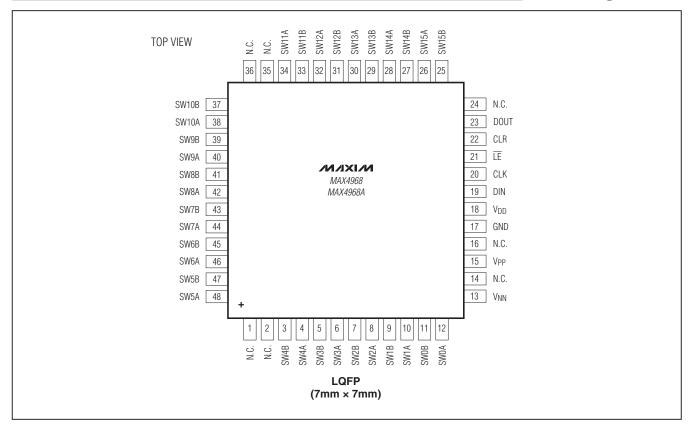

Pin Configuration

### **Pin Description**

| PIN | NAME  | FUNCTION                                                                                             |

|-----|-------|------------------------------------------------------------------------------------------------------|

| 15  | Vpp   | Positive Voltage Supply. Bypass<br>VPP to GND with a 0.1µF or<br>greater ceramic capacitor.          |

| 17  | GND   | Ground                                                                                               |

| 18  | Vdd   | Logic Supply Voltage. Bypass<br>V <sub>DD</sub> to GND with a 0.1µF or<br>greater ceramic capacitor. |

| 19  | DIN   | Serial-Data Input                                                                                    |

| 20  | CLK   | Serial-Clock Input                                                                                   |

| 21  | LE    | Active-Low Latch-Enable Input                                                                        |

| 22  | CLR   | Latch-Clear Input                                                                                    |

| 23  | DOUT  | Serial-Data Output                                                                                   |

| 25  | SW15B | Analog Switch 15—Terminal                                                                            |

| 26  | SW15A | Analog Switch 15—Terminal                                                                            |

| 27  | SW14B | Analog Switch 14—Terminal                                                                            |

|                             |                 | 1                                                                                                            |

|-----------------------------|-----------------|--------------------------------------------------------------------------------------------------------------|

| PIN                         | NAME            | FUNCTION                                                                                                     |

| 1, 2, 14, 16,<br>24, 35, 36 | N.C.            | No Connection. Not connected internally.                                                                     |

| 3                           | SW4B            | Analog Switch 4—Terminal                                                                                     |

| 4                           | SW4A            | Analog Switch 4—Terminal                                                                                     |

| 5                           | SW3B            | Analog Switch 3—Terminal                                                                                     |

| 6                           | SW3A            | Analog Switch 3—Terminal                                                                                     |

| 7                           | SW2B            | Analog Switch 2—Terminal                                                                                     |

| 8                           | SW2A            | Analog Switch 2—Terminal                                                                                     |

| 9                           | SW1B            | Analog Switch 1 —Terminal                                                                                    |

| 10                          | SW1A            | Analog Switch 1—Terminal                                                                                     |

| 11                          | SW0B            | Analog Switch 0—Terminal                                                                                     |

| 12                          | SW0A            | Analog Switch 0—Terminal                                                                                     |

| 13                          | V <sub>NN</sub> | Negative High-Voltage Supply.<br>Bypass V <sub>NN</sub> to GND with a 0.1µF<br>or greater ceramic capacitor. |

| NAME  | FUNCTION                                                                      |

|-------|-------------------------------------------------------------------------------|

| SW14A | Analog Switch 14—Terminal                                                     |

| SW13B | Analog Switch 13—Terminal                                                     |

| SW13A | Analog Switch 13—Terminal                                                     |

| SW12B | Analog Switch 12—Terminal                                                     |

| SW12A | Analog Switch 12—Terminal                                                     |

| SW11B | Analog Switch 11—Terminal                                                     |

| SW11A | Analog Switch 11—Terminal                                                     |

| SW10B | Analog Switch 10—Terminal                                                     |

| SW10A | Analog Switch 10—Terminal                                                     |

| SW9B  | Analog Switch 9—Terminal                                                      |

|       | SW14A<br>SW13B<br>SW13A<br>SW12B<br>SW12A<br>SW11B<br>SW11A<br>SW10B<br>SW10A |

### **Detailed Description**

The MAX4968/MAX4968A are 16-channel, high-linearity, high-voltage, bidirectional SPST analog switches with 18 $\Omega$  (typ) on-resistance. The devices are ideal for use in applications requiring high-voltage switching controlled by a low-voltage control signal, such as ultrasound imaging and printers. The MAX4968A provides integrated 40k $\Omega$  (typ) bleed resistors on each switch terminal to discharge capacitive loads. Using HVCMOS technology, these switches combine high-voltage, bilateral MOS switches and low-power CMOS logic to provide efficient control of high-voltage analog signals.

The MAX4968 is pin-to-pin compatible with the MAX14802 and Supertex HV2601. The MAX4968A is pin-to-pin compatible with the MAX14803 and Supertex HV2701. The only difference is the VPP positive supply voltage level. The MAX4968/MAX4968A require a low +10V (typ) voltage (VPP), whereas the MAX14802/MAX14803 and HV2601/HV2701 require a high +100V supply voltage.

In typical ultrasound applications, these devices do not require dedicated high-voltage supply, which implies a significant simplification of system requirement. The negative voltage supply can be shared with the transmitter and the positive voltage supply is typically +10V.

### Pin Description (continued)

| PIN | NAME | FUNCTION                 |

|-----|------|--------------------------|

| 40  | SW9A | Analog Switch 9—Terminal |

| 41  | SW8B | Analog Switch 8—Terminal |

| 42  | SW8A | Analog Switch 8—Terminal |

| 43  | SW7B | Analog Switch 7—Terminal |

| 44  | SW7A | Analog Switch 7—Terminal |

| 45  | SW6B | Analog Switch 6—Terminal |

| 46  | SW6A | Analog Switch 6—Terminal |

| 47  | SW5B | Analog Switch 5—Terminal |

| 48  | SW5A | Analog Switch 5—Terminal |

#### **Analog Switch**

The devices can transmit analog signals up to 210VP-P, with an analog signal range from V<sub>NN</sub> to V<sub>NN</sub> + 210V. Before starting the high-voltage burst transmission (VP-P > +20V), the input voltage is required to be close to GND to allow a proper settling of the pass FET. The high-voltage burst frequency must be greater than 500kHz.

Extremely long high-voltage bursts (VP-P > +10V) with duty cycle greater than 20% could result in signal degradation, especially for unipolar transmission. In general, this applies for burst transmission with a nonzero DC content.

Low-voltage signal (VP-P < 10V) continuous-wave bipolar transmission is supported for frequencies greater than 500kHz. For very small signals, such as the small echoes in typical ultrasound imaging systems (VP-P < 10V), the devices are not limited to a low-frequency bandwidth and can transmit DC signals.

#### **Voltage Supplies**

The devices operate with a high-voltage supply VNN from -200V to 0, VPP supply of +10V (typ), and a logic supply VDD (+2.37V to +5.5V).

#### **Bleed Resistors (MAX4968A)**

The MAX4968A features integrated  $40k\Omega$  (typ) bleed resistors to discharge capacitive loads such as piezoelectric transducers. Each analog switch terminal is connected to GND with a bleed resistor.

#### **Serial Interface**

The MAX4968/MAX4968A are controlled by a serial interface with a 16-bit serial shift register and transparent latch. Each of the 16 data bits controls a single analog switch (see Table 1). Data on DIN is clocked with the most significant bit (MSB) first into the shift register on the rising edge of CLK. Data is clocked out of the shift register onto DOUT on the rising edge of CLK. DOUT reflects the status of DIN, delayed by 16 clock cycles (see Figures 2 and 3).

#### Latch Enable (LE)

Drive LE logic-low to change the contents of the latch and update the state of the high-voltage switches (Figure 3). Drive  $\overline{\text{LE}}$  logic-high to freeze the contents of the latch and prevent changes to the switch states. To reduce noise due to clock feedthrough, drive  $\overline{\text{LE}}$  logic-high while data is clocked into the shift register. After the data shift register is loaded with valid data, pulse  $\overline{\text{LE}}$  logic-low to load the contents of the shift register into the latch.

#### Latch Clear (CLR)

The MAX4968/MAX4968A feature a latch-clear input. Drive CLR logic-high to reset the contents of the latch to zero and open all switches. CLR does not affect the contents of the data shift register. Pulse  $\overline{\text{LE}}$  logic-low to reload the contents of the shift register into the latch.

#### **Power-On Reset**

The MAX4968/MAX4968A feature a power-on-reset circuit to ensure all switches are open at power-on. The internal 16-bit serial shift register and latch are set to zero on power-up.

| DATA BITS   |    |    |    |    |    |    |    |    | TROL<br>TS | L FUNCTION          |     |     |     |     |     |     |     |

|-------------|----|----|----|----|----|----|----|----|------------|---------------------|-----|-----|-----|-----|-----|-----|-----|

| D0<br>(LSB) | D1 | D2 | D3 | D4 | D5 | D6 | D7 | LE | CLR        | SW0                 | SW1 | SW2 | SW3 | SW4 | SW5 | SW6 | SW7 |

| L           |    |    |    |    |    |    |    | L  | L          | Off                 |     |     |     |     |     |     |     |

| Н           |    |    |    |    |    |    |    | L  | L          | On                  |     |     |     |     |     |     |     |

|             | L  |    |    |    |    |    |    | L  | L          |                     | Off |     |     |     |     |     |     |

|             | н  |    |    |    |    |    |    | L  | L          |                     | On  |     |     |     |     |     |     |

|             |    | L  |    |    |    |    |    | L  | L          |                     |     | Off |     |     |     |     |     |

|             |    | Н  |    |    |    |    |    | L  | L          |                     |     | On  |     |     |     |     |     |

|             |    |    | L  |    |    |    |    | L  | L          |                     |     |     | Off |     |     |     |     |

|             |    |    | Н  |    |    |    |    | L  | L          |                     |     |     | On  |     |     |     |     |

|             |    |    |    | L  |    |    |    | L  | L          |                     |     |     |     | Off |     |     |     |

|             |    |    |    | Н  |    |    |    | L  | L          |                     |     |     |     | On  |     |     |     |

|             |    |    |    |    | L  |    |    | L  | L          |                     |     |     |     |     | Off |     |     |

|             |    |    |    |    | Н  |    |    | L  | L          |                     |     |     |     |     | On  |     |     |

|             |    |    |    |    |    | L  |    | L  | L          |                     |     |     |     |     |     | Off |     |

|             |    |    |    |    |    | Н  |    | L  | L          |                     |     |     |     |     |     | On  |     |

|             |    |    |    |    |    |    | L  | L  | L          |                     |     |     |     |     |     |     | Off |

|             |    |    |    |    |    |    | Н  | L  | L          |                     |     |     |     |     |     |     | On  |

| Х           | Х  | Х  | Х  | Х  | Х  | Х  | Х  | Н  | L          | Hold Previous State |     |     |     |     |     |     |     |

| Х           | Х  | Х  | Х  | Х  | Х  | Х  | Х  | Х  | Н          | Off                 | Off | Off | Off | Off | Off | Off | Off |

| DATA BITS |    |     |     |     |     | CONTROL<br>BITS |              | FUNCTION |     |                     |     |      |      |      |      |      |      |

|-----------|----|-----|-----|-----|-----|-----------------|--------------|----------|-----|---------------------|-----|------|------|------|------|------|------|

| D8        | D9 | D10 | D11 | D12 | D13 | D14             | D15<br>(MSB) | LE       | CLR | SW8                 | SW9 | SW10 | SW11 | SW12 | SW13 | SW14 | SW15 |

| L         |    |     |     |     |     |                 |              | L        | L   | Off                 |     |      |      |      |      |      |      |

| Н         |    |     |     |     |     |                 |              | L        | L   | On                  |     |      |      |      |      |      |      |

|           | L  |     |     |     |     |                 |              | L        | L   |                     | Off |      |      |      |      |      |      |

|           | Н  |     |     |     |     |                 |              | L        | L   |                     | On  |      |      |      |      |      |      |

|           |    | L   |     |     |     |                 |              | L        | L   |                     |     | Off  |      |      |      |      |      |

|           |    | Н   |     |     |     |                 |              | L        | L   |                     |     | On   |      |      |      |      |      |

|           |    |     | L   |     |     |                 |              | L        | L   |                     |     |      | Off  |      |      |      |      |

|           |    |     | Н   |     |     |                 |              | L        | L   |                     |     |      | On   |      |      |      |      |

|           |    |     |     | L   |     |                 |              | L        | L   |                     |     |      |      | Off  |      |      |      |

|           |    |     |     | Н   |     |                 |              | L        | L   |                     |     |      |      | On   |      |      |      |

|           |    |     |     |     | L   |                 |              | L        | L   |                     |     |      |      |      | Off  |      |      |

|           |    |     |     |     | Н   |                 |              | L        | L   |                     |     |      |      |      | On   |      |      |

|           |    |     |     |     |     | L               |              | L        | L   |                     |     |      |      |      |      | Off  |      |

|           |    |     |     |     |     | Н               |              | L        | L   |                     |     |      |      |      |      | On   |      |

|           |    |     |     |     |     |                 | L            | L        | L   |                     |     |      |      |      |      |      | Off  |

|           |    |     |     |     |     |                 | Н            | L        | L   |                     |     |      |      |      |      |      | On   |

| Х         | Х  | Х   | Х   | Х   | Х   | Х               | Х            | Н        | L   | Hold Previous State |     |      |      |      |      |      |      |

| Х         | Х  | Х   | Х   | Х   | Х   | Х               | Х            | Х        | Н   | Off                 | Off | Off  | Off  | Off  | Off  | Off  | Off  |

### Table 1. Serial Interface Programming (Notes 1–6) (continued)

Note 1: The 16 switches operate independently.

Note 2: Serial data is clocked in on the rising edge of CLK.

Note 3: The switches go to a state retaining their present condition on the rising edge of LE. When LE is low, the shift register data flows through the latch.

Note 4: DOUT is high when switch 15 is on.

**Note 5:** Shift register clocking has no effect on the switch states if <u>LE</u> is high.

**Note 6:** The CLR input overrides all other inputs.

### **Applications Information**

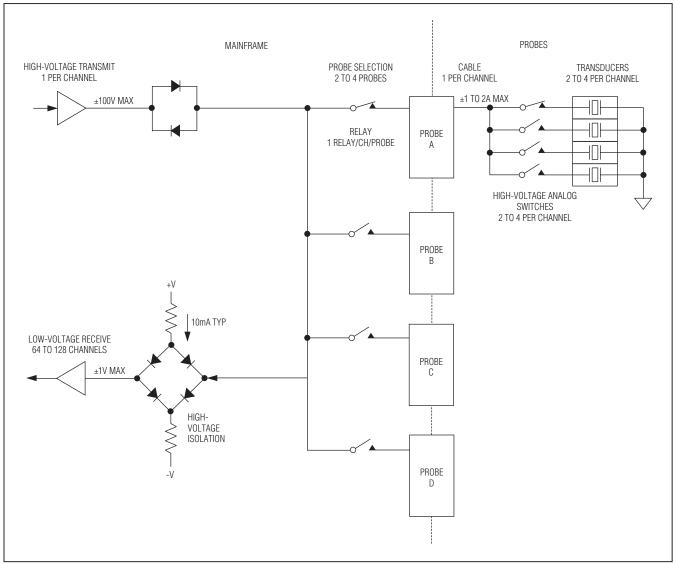

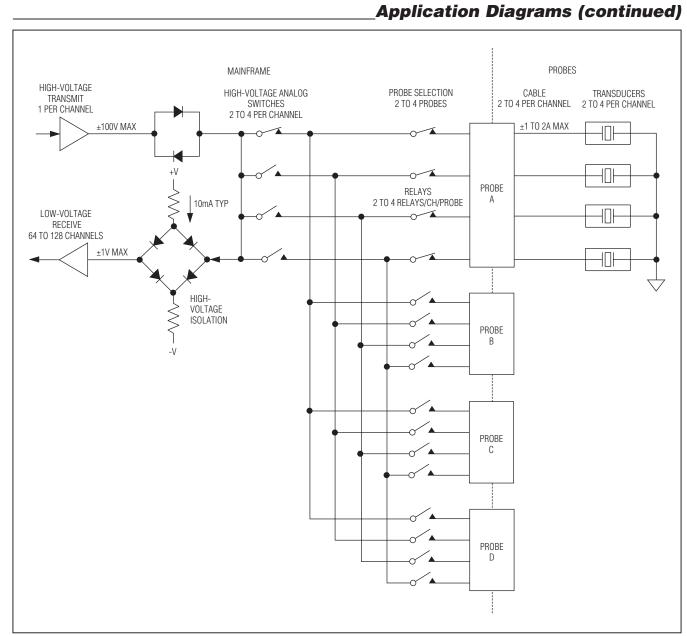

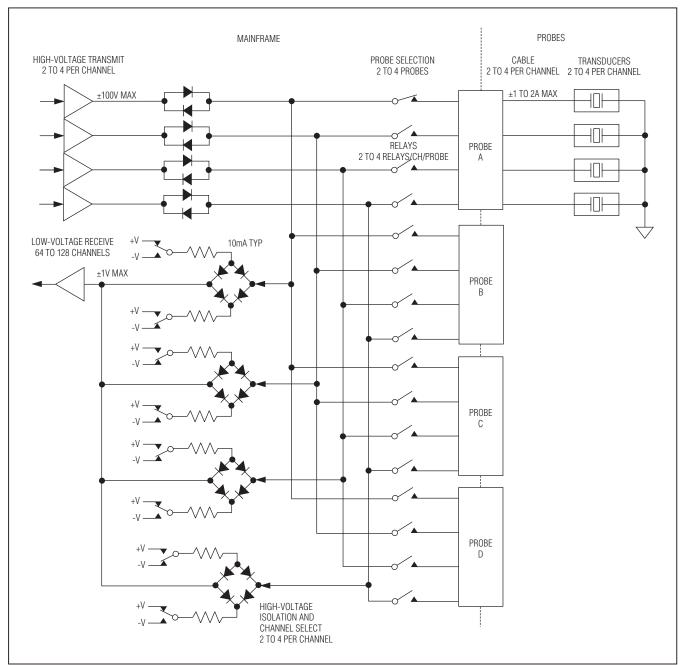

In typical ultrasound applications, the MAX4968/MAX4968A do not require dedicated high-voltage supplies; the negative voltage supply can be shared with the transmitter and the positive voltage supply is typically +10V. See Figures 5, 6, and 7 for medical ultrasound applications.

#### **Logic Levels**

The MAX4968/MAX4968A digital interface inputs CLK, DIN,  $\overline{\text{LE}}$ , and CLR operate on the VDD logic supply voltage.

#### **Daisy-Chaining Multiple Devices**

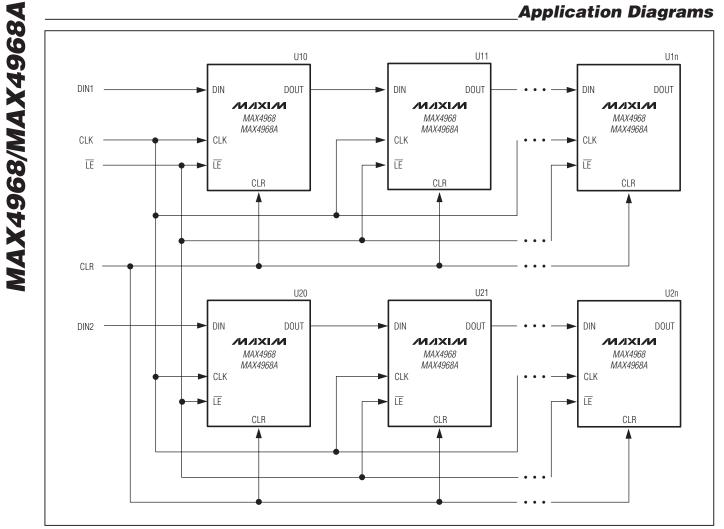

Digital output DOUT is provided to allow the connection of multiple MAX4968/MAX4968A devices by daisy-

chaining (Figure 4). Connect each DOUT to the DIN of the subsequent device in the chain. Connect CLK,  $\overline{\text{LE}}$ , and CLR inputs of all devices, and drive  $\overline{\text{LE}}$  logic-low to update all devices simultaneously. Drive CLR high to open all the switches simultaneously. Additional shift registers can be included anywhere in series with the MAX4968/MAX4968A daisy-chain.

#### **Supply Sequencing and Bypassing**

The MAX4968/MAX4968A do not require special sequencing of the VDD, VPP, and VNN supply voltages. Bypass VDD, VPP, and VNN to GND with a  $0.1\mu$ F ceramic capacitor as close as possible to the device.

**Note:** Keep  $\overline{\text{LE}}$  low during power-up.

Figure 4. Interfacing Multiple Devices by Daisy-Chaining

### Application Diagrams (continued)

Figure 5. Medical Ultrasound Application—High-Voltage Analog Switches in Probe

Figure 6. Medical Ultrasound Application—High-Voltage Analog Switches in Mainframe

M/X/M

MAX4968/MAX4968A

## Application Diagrams (continued)

Figure 7. Medical Ultrasound Application—Multiple Transmit and Isolation per Receiver Channel

**Functional Diagram** VDD Vpp CLR -SW0B LEVEL LATCH VNN SHIFTER DIN **SWOA** VNN M/IXI/M MAX4968 16-BIT CLK · MAX4968A SHIFT REGISTER SW15B DOUT -本 LEVEL LATCH SHIFTER V<sub>NN</sub> - SW15A 4 V<sub>NN</sub> LE GND V<sub>NN</sub> \*BLEED RESISTORS AVAILABLE ON THE MAX4968A ONLY.

### **Chip Information**

PROCESS: BICMOS

MAX4968/MAX4968A

### **Package Information**

For the latest package outline information and land patterns (footprints), go to www.maxim-ic.com/packages. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE | PACKAGE | OUTLINE        | LAND           |

|---------|---------|----------------|----------------|

| TYPE    | CODE    | NO.            | PATTERN NO.    |

| 48 LQFP | C48+6   | <u>21-0054</u> | <u>90-0093</u> |

## **Revision History**

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION                                                                                                                                                                      | PAGES<br>CHANGED |

|--------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| 0                  | 3/11             | Initial release                                                                                                                                                                  | —                |

| 1                  | 5/11             | Removed future product asterisk from MAX4968 in <i>Ordering Information</i> , corrected Off-Isolation specification in <i>Electrical Characteristics</i>                         | 1, 3             |

| 2                  | 1/12             | Updated V <sub>NN</sub> specifications in <i>Absolute Maximum Ratings</i> and <i>Electrical Characteristics</i> supply voltage and V <sub>NN</sub> static current specifications | 2, 3, 4, 9       |

MAX4968/MAX4968A

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

Maxim is a registered trademark of Maxim Integrated Products, Inc.

17

## **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Maxim Integrated:

MAX4968ACCM+ MAX4968ACCM+T MAX4968AECM+ MAX4968AECM+T MAX4968ECM+ MAX4968ECM+T