# 7.6A, 12ns, SOT23/TDFN, MOSFET Driver

### **General Description**

The MAX5048A/MAX5048B are high-speed MOSFET drivers capable of sinking/sourcing 7.6A/1.3A peak currents. These devices take logic input signals and drive a large external MOSFET. The MAX5048A/MAX5048B have inverting and noninverting inputs that give the user greater flexibility in controlling the MOSFET. They feature two separate outputs working in complementary mode, offering flexibility in controlling both turn-on and turn-off switching speeds.

The MAX5048A/MAX5048B have internal logic circuitry, which prevents shoot-through during output state changes. The logic inputs are protected against voltage spikes up to +14V, regardless of V+ voltage. Propagation delay time is minimized and matched between the inverting and noninverting inputs. The MAX5048A/MAX5048B have very fast switching times combined with very short propagation delays (12ns typ), making them ideal for high-frequency circuits.

The MAX5048A/MAX5048B operate from a +4V to +12.6V single power supply and typically consume 0.95mA of supply current. The MAX5048A has CMOS input logic levels, while the MAX5048B has standard TTL input logic levels. These devices are available in space-saving 6-pin SOT23 and TDFN packages.

### Applications

Power MOSFET Switching Switch-Mode Power Supplies DC-DC Converters Motor Control Power-Supply Modules

#### **Features**

- Independent Source-and-Sink Outputs for Controllable Rise and Fall Times

- ♦ +4V to +12.6V Single Power Supply

- ♦ 7.6A/1.3A Peak Sink/Source Drive Current

- ♦ 0.23Ω Open-Drain n-Channel Sink Output

- ♦ 2Ω Open-Drain p-Channel Source Output

- ♦ 12ns (typ) Propagation Delay

- ♦ Matching Delay Time Between Inverting and Noninverting Inputs

- ♦ V<sub>CC</sub>/2 CMOS (MAX5048A)/TTL (MAX5048B) Logic Inputs

- ♦ 1.6V Input Hysteresis

- ♦ Up to +14V Logic Inputs (Regardless of V+ Voltage)

- ♦ Low Input Capacitance: 2.5pF (typ)

- ♦ -40°C to +125°C Operating Temperature Range

- ♦ 6-Pin SOT23 and TDFN Packages

### **Ordering Information**

| PART      | TEM         | P RANGE   | PIN-<br>PACKAGE | LOGIC<br>INPUT             | -    |

|-----------|-------------|-----------|-----------------|----------------------------|------|

| MAX5048AA | NUT-T -40°C | to +125°C | 6 SOT23         | V <sub>CC</sub> /2<br>CMOS | ABEC |

| MAX5048BA | UT-T -40°C  | to +125°C | 6 SOT23         | TTL                        | ABED |

| MAX5048AA | ATT-T -40°C | to +125°C | 6 TDFN-EP*      | V <sub>CC</sub> /2<br>CMOS | AKV  |

| MAX5048BA | TT-T -40°C  | to +125°C | 6 TDFN-EP*      | TTL                        | AKW  |

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package.

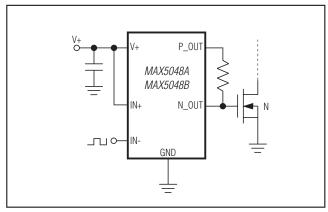

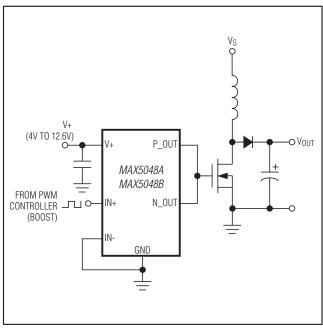

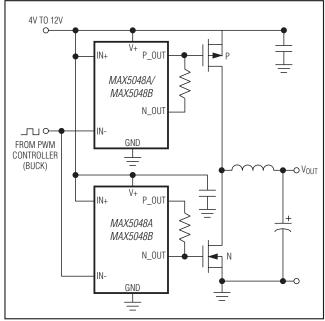

## **Typical Operating Circuit**

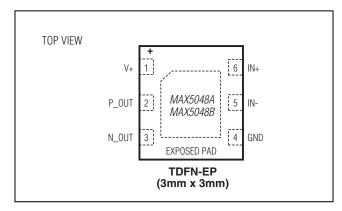

### **Pin Configurations**

T = Tape and reel.

<sup>\*</sup>EP = Exposed pad.

# 7.6A, 12ns, SOT23/TDFN, MOSFET Driver

#### **ABSOLUTE MAXIMUM RATINGS**

| Voltages Referenced to GND                             | 6-Pin TDFN (derate 18.2mW/°C above +70°C)1454mW |

|--------------------------------------------------------|-------------------------------------------------|

| V+0.3V to +13V                                         | Operating Temperature Range40°C to +125°C       |

| IN+, IN0.3V to +14V                                    | Storage Temperature Range65°C to +150°C         |

| N_OUT, P_OUT0.3V to (V+ + 0.3V)                        | Junction Temperature+150°C                      |

| N_OUT Continuous Output Current (Note 1)390mA          | Lead Temperature (soldering, 10s)+300°C         |

| P_OUT Continuous Output Current (Note 1)100mA          | Soldering Temperature (reflow)+260°C            |

| Continuous Power Dissipation* (T <sub>A</sub> = +70°C) |                                                 |

| 6-Pin SOT23 (derate 9.1mW/°C above +70°C)727mW         |                                                 |

**Note 1:** Continuous output current is limited by the power dissipation of the package.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **PACKAGE THERMAL CHARACTERISTICS (Note 2)**

SOT23

Junction-to-Case Thermal Resistance (θ<sub>JC</sub>).......75°C/W IDFN Junction-to-Case Thermal Resistance (θ<sub>JC</sub>)......8.5°C/W

**Note 2:** Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maximintegrated.com/thermal-tutorial">www.maximintegrated.com/thermal-tutorial</a>.

#### **ELECTRICAL CHARACTERISTICS**

$(V+ = +12V, T_A = -40^{\circ}C \text{ to } +125^{\circ}C, \text{ unless otherwise noted. Typical values are at } T_A = +25^{\circ}C.)$  (Note 3)

| PARAMETER                                            | SYMBOL             | COI                          | NDITIONS                | MIN  | TYP  | MAX  | UNITS |

|------------------------------------------------------|--------------------|------------------------------|-------------------------|------|------|------|-------|

| POWER SUPPLY                                         |                    |                              |                         |      |      |      |       |

| V+ Operating Range                                   | V+                 |                              |                         | 4.0  |      | 12.6 | V     |

| V+ Undervoltage Lockout                              | UVLO               | V+ rising                    |                         | 3.25 | 3.6  | 4.00 | V     |

| V+ Undervoltage Lockout<br>Hysteresis                |                    |                              |                         |      | 400  |      | mV    |

| V+ Undervoltage Lockout to<br>Output Delay Time      |                    | V+ rising                    |                         |      | 300  |      | ns    |

| V+ Supply Current                                    | l+                 | IN+ = IN- = V+               |                         |      | 0.95 | 1.5  | mA    |

| n-CHANNEL OUTPUT                                     |                    |                              |                         |      |      |      |       |

|                                                      |                    | $V_{V+} = +10V$ ,            | T <sub>A</sub> = +25°C  |      | 0.23 | 0.32 |       |

| Driver Output Resistance— Pulling Down (MAX5048AAUT/ | Pour               | $I_{N-OUT} = -100mA$         | $T_A = +125^{\circ}C$   |      | 0.38 | 0.43 | Ω     |

| MAX5048BAUT)                                         | R <sub>ON-N</sub>  | $V_{V+} = +4.5V$ ,           | $T_A = +25^{\circ}C$    |      | 0.24 | 0.34 | 52    |

|                                                      |                    | $I_{N-OUT} = -100mA$         | T <sub>A</sub> = +125°C |      | 0.40 | 0.47 |       |

|                                                      |                    | $V_{V+} = +10V$ ,            | $T_A = +25^{\circ}C$    |      | 0.31 | 0.34 |       |

| Driver Output Resistance—                            | Pour               | $I_{N-OUT} = -100 \text{mA}$ | T <sub>A</sub> = +125°C |      | 0.46 | 0.51 | Ω     |

| Pulling Down (MAX5048AATT/ RON-N MAX5048BATT)        | $V_{V+} = +4.5V$ , | T <sub>A</sub> = +25°C       |                         | 0.32 | 0.36 | 52   |       |

| ,                                                    |                    | $I_{N-OUT} = -100mA$         | T <sub>A</sub> = +125°C |      | 0.48 | 0.55 |       |

<sup>\*</sup>As per JEDEC51 standard.

# 7.6A, 12ns, SOT23/TDFN, MOSFET Driver

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V+=+12V, T_A=-40^{\circ}C \text{ to } +125^{\circ}C, \text{ unless otherwise noted. Typical values are at } T_A=+25^{\circ}C.)$  (Note 3)

| PARAMETER                                | SYMBOL             | С                                         | ONDITIONS                         | MIN      | TYP        | MAX      | UNITS |  |

|------------------------------------------|--------------------|-------------------------------------------|-----------------------------------|----------|------------|----------|-------|--|

| Power-Off Pulldown Resistance            |                    | V+ = 0 or unconne<br>$T_A = +25$ °C       | cted, I <sub>N-OUT</sub> = -10mA, |          | 3.3        | 10       | Ω     |  |

| Power-Off Pulldown Clamp<br>Voltage      |                    | V+ = 0 or unconne<br>$T_A = +25^{\circ}C$ | cted, I <sub>N-OUT</sub> = -10mA, |          | 0.85       | 1.0      | V     |  |

| Output Leakage Current                   | I <sub>LK-N</sub>  | N_OUT = V+                                |                                   |          | 6.85       | 20       | μΑ    |  |

| Peak Output Current (Sinking)            | I <sub>PK-N</sub>  | $C_L = 10,000pF$                          |                                   |          | 7.6        |          | А     |  |

| p-CHANNEL OUTPUT                         |                    |                                           |                                   |          |            |          |       |  |

|                                          |                    | $V_{V+} = +10V$ ,                         | T <sub>A</sub> = +25°C            |          | 2.00       | 3.00     |       |  |

| Driver Output Resistance—                |                    | $I_{P-OUT} = 50mA$                        | $T_A = +125^{\circ}C$             |          | 2.85       | 4.30     |       |  |

| Pulling Up (MAX5048AAUT/<br>MAX5048BAUT) | R <sub>ON-P</sub>  | $V_{V+} = +4.5V$ ,                        | T <sub>A</sub> = +25°C            |          | 2.20       | 3.30     | Ω     |  |

| W/ 0.0040B/ (01)                         |                    | $I_{P-OUT} = 50mA$                        | $T_A = +125^{\circ}C$             |          | 3.10       | 4.70     |       |  |

|                                          |                    | $V_{V+} = +10V$ ,                         | T <sub>A</sub> = +25°C            |          | 2.08       | 3.08     |       |  |

| Driver Output Resistance—                |                    | $I_{P-OUT} = 50mA$                        | $T_A = +125^{\circ}C$             |          | 2.93       | 4.38     | _     |  |

| Pulling Up (MAX5048AATT/<br>MAX5048BATT) | R <sub>ON-P</sub>  | $V_{V+} = +4.5V$ ,                        | T <sub>A</sub> = +25°C            |          | 2.28       | 3.38     | Ω     |  |

| WAXSO40DATT)                             |                    | $I_{P-OUT} = 50mA$                        | $T_A = +125^{\circ}C$             |          | 3.18       | 4.78     |       |  |

| Output Leakage Current                   | I <sub>LK-P</sub>  | P_OUT = 0                                 | <b>'</b>                          |          | 0.001      | 10       | μΑ    |  |

| Peak Output Current (Sourcing)           | I <sub>PK-P</sub>  | $C_L = 10,000pF$                          |                                   |          | 1.3        |          | А     |  |

| LOGIC INPUT                              | •                  |                                           |                                   |          |            |          | •     |  |

| Logic 4 logut Voltogo                    | Vi                 | MAX5048A                                  |                                   | 0.67 x V | <b>'</b> + |          | V     |  |

| Logic 1 Input Voltage                    | VIH                | MAX5048B                                  |                                   | 2.4      |            |          | V     |  |

| Logio O Input Voltago                    | VIL                | MAX5048A                                  |                                   |          | 0          | .33 x V+ | V     |  |

| Logic 0 Input Voltage                    | VIL.               | MAX5048B                                  |                                   |          |            | 0.8      | V     |  |

| Logic-Input Hysteresis                   | V. v. co           | MAX5048A                                  |                                   |          | 1.6        |          | V     |  |

| Logic-input Hysteresis                   | V <sub>H</sub> YS  | MAX5048B                                  |                                   |          | 0.68       |          | V     |  |

| Logic-Input Current                      |                    | $V_{IN} = V + \text{ or } 0$              |                                   |          | 0.001      | 10       | μΑ    |  |

| Input Capacitance                        | C <sub>IN</sub>    |                                           |                                   |          | 2.5        |          | рF    |  |

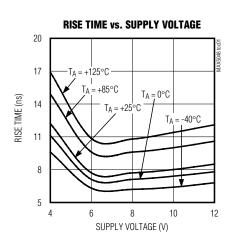

| SWITCHING CHARACTERISTICS                | FOR V+ =           | +10V                                      |                                   |          |            |          |       |  |

|                                          |                    | C <sub>L</sub> = 1000pF                   |                                   |          | 8<br>45    |          |       |  |

| Rise Time                                | t <sub>R</sub>     | $C_L = 5000pF$                            |                                   |          |            |          | ns    |  |

|                                          |                    | $C_L = 10,000pF$                          |                                   |          | 82         |          |       |  |

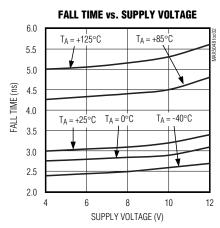

|                                          |                    | $C_L = 1000pF$                            |                                   |          | 3.2        |          |       |  |

| Fall Time                                | tF                 | C <sub>L</sub> = 5000pF                   |                                   |          | 7.5        |          | ns    |  |

|                                          |                    | C <sub>L</sub> = 10,000pF                 |                                   |          | 12.5       |          |       |  |

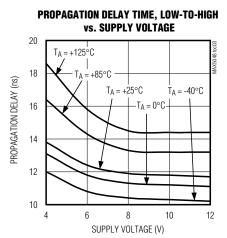

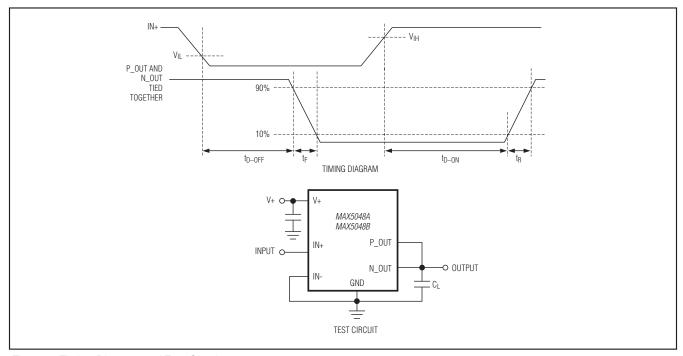

| Turn-On Propagation Delay Time           | t <sub>D-ON</sub>  | Figure 1, C <sub>L</sub> = 100            | OpF (Note 4)                      | 7        | 12         | 25       | ns    |  |

| Turn-Off Propagation Delay Time          | t <sub>D-OFF</sub> | Figure 1, C <sub>L</sub> = 100            | OpF (Note 4)                      | 7        | 12         | 25       | ns    |  |

| Break-Before-Make Time                   |                    |                                           |                                   |          | 2.5        |          | ns    |  |

# 7.6A, 12ns, SOT23/TDFN, MOSFET Driver

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V+=+12V, T_A=-40^{\circ}C \text{ to } +125^{\circ}C, \text{ unless otherwise noted. Typical values are at } T_A=+25^{\circ}C.)$  (Note 2)

| PARAMETER                       | SYMBOL             | CONDITIONS                                 | MIN | TYP  | MAX | UNITS |

|---------------------------------|--------------------|--------------------------------------------|-----|------|-----|-------|

| SWITCHING CHARACTERISTICS       | FOR V+ =           | +4.5V                                      |     |      |     |       |

|                                 |                    | $C_L = 1000pF$                             |     | 12   |     |       |

| Rise Time                       | t <sub>R</sub>     | C <sub>L</sub> = 5000pF                    |     | 41   |     | ns    |

|                                 |                    | $C_L = 10,000pF$                           |     | 74   |     |       |

|                                 |                    | $C_L = 1000pF$                             |     | 3.0  |     |       |

| Fall Time                       | tF                 | $C_L = 5000pF$                             |     | 7.0  |     | ns    |

|                                 |                    | $C_L = 10,000pF$                           |     | 11.3 |     |       |

| Turn-On Propagation Delay Time  | t <sub>D-ON</sub>  | Figure 1, C <sub>L</sub> = 1000pF (Note 4) | 8   | 14   | 27  | ns    |

| Turn-Off Propagation Delay Time | t <sub>D-OFF</sub> | Figure 1, C <sub>L</sub> = 1000pF (Note 4) | 8   | 14   | 27  | ns    |

| Break-Before-Make Time          |                    |                                            |     | 4.2  | •   | ns    |

**Note 3:** All DC specifications are 100% tested at  $T_A = +25^{\circ}C$ . Specifications over -40°C to +125°C are guaranteed by design.

Note 4: Guaranteed by design, not production tested.

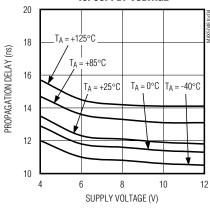

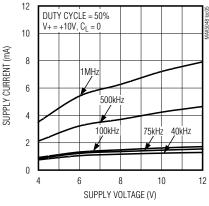

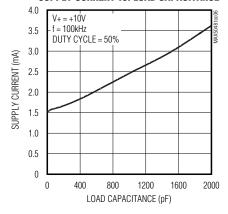

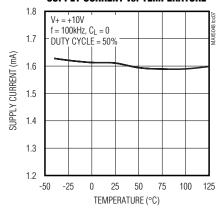

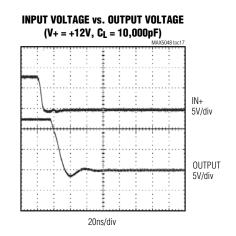

### Typical Operating Characteristics

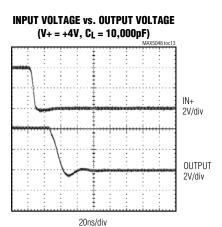

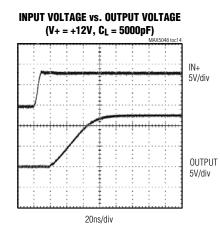

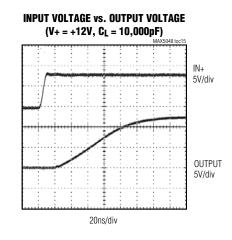

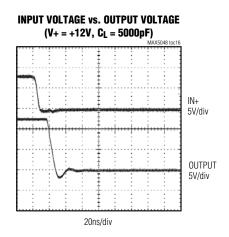

( $C_L = 1000 pF$ ,  $T_A = +25 °C$ , unless otherwise noted.)

# 7.6A, 12ns, SOT23/TDFN, MOSFET Driver

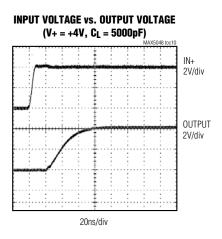

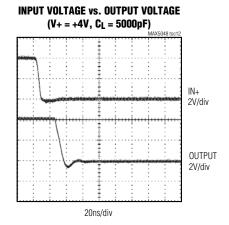

### Typical Operating Characteristics (continued)

( $C_L = 1000 pF$ ,  $T_A = +25 °C$ , unless otherwise noted.)

# PROPAGATION DELAY TIME, HIGH-TO-LOW vs. SUPPLY VOLTAGE

### SUPPLY CURRENT vs. SUPPLY VOLTAGE

#### SUPPLY CURRENT vs. LOAD CAPACITANCE

#### SUPPLY CURRENT vs. TEMPERATURE

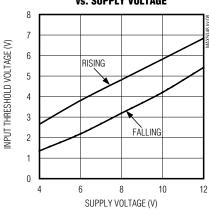

#### MAX5048A Input Threshold Voltage Vs. Supply Voltage

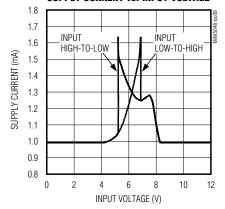

#### MAX5048A SUPPLY CURRENT VS. INPUT VOLTAGE

# 7.6A, 12ns, SOT23/TDFN, MOSFET Driver

### Typical Operating Characteristics (continued)

( $C_L = 1000 pF$ ,  $T_A = +25 °C$ , unless otherwise noted.)

# 7.6A, 12ns, SOT23/TDFN, MOSFET Driver

### Pin Description

| PIN | NAME                                                           | FUNCTION                                                                                     |

|-----|----------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| 1   | V+                                                             | Power Supply. Bypass to GND with a 0.1µF ceramic capacitor.                                  |

| 2   | P_OUT p-Channel Open-Drain Output. current for MOSFET turn-on. |                                                                                              |

| 3   | N_OUT                                                          | n-Channel Open-Drain Output. Sinks current for MOSFET turn-off.                              |

| 4   | GND                                                            | Ground                                                                                       |

| 5   | IN-                                                            | Inverting Logic Input Terminal. Connect to GND when not used.                                |

| 6   | IN+                                                            | Noninverting Logic Input Terminal. Connect to V+ when not used.                              |

| _   | EP                                                             | Exposed paddle. Connect to GND. Solder EP to the GND plane for improved thermal performance. |

### **Detailed Description**

#### **Logic Inputs**

The MAX5048A/MAX5048Bs' logic inputs are protected against voltage spikes up to +14V, regardless of the V+ voltage. The low 2.5pF input capacitance of the inputs reduces loading and increases switching speed. These devices have two inputs that give the user greater flexibility in controlling the MOSFET. Table 1 shows all possible input combinations.

The difference between the MAX5048A and the MAX5048B is the input threshold voltage. The MAX5048A has V<sub>CC</sub>/2 CMOS logic-level thresholds, while the MAX5048B has TTL logic-level thresholds (see the *Electrical Characteristics*). For V+ above 5.5V, V<sub>IH</sub> (typ) = 0.5x(V+) + 0.8V and V<sub>IL</sub> (typ) = 0.5x(V+) - 0.8V. As V+ is reduced from 5.5V to 4V, V<sub>IH</sub> and V<sub>IL</sub> gradually approach V<sub>IH</sub> (typ) = 0.5x(V+) + 0.65V and V<sub>IL</sub> (typ) = 0.5x(V+) - 0.65V. Connect IN+ to V+ or IN- to GND when not used. Alternatively, the unused input can be used as an ON/OFF pin (see Table 1).

**Table 1. Truth Table**

| IN+ | IN- | p-CHANNEL | n-CHANNEL |

|-----|-----|-----------|-----------|

| L   | L   | OFF       | ON        |

| L   | Н   | OFF       | ON        |

| Н   | L   | ON        | OFF       |

| Н   | Н   | OFF       | ON        |

L = Logic lowH = Logic high

#### **Undervoltage Lockout (UVLO)**

When V+ is below the UVLO threshold, the N-channel is ON and the P-channel is OFF, independent of the state of the inputs. The UVLO is typically 3.6V with 400mV typical hysteresis to avoid chattering.

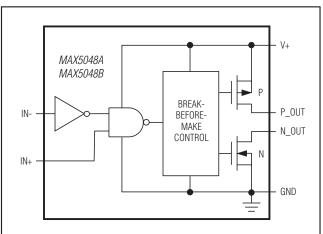

#### **Driver Outputs**

The MAX5048A/MAX5048B provide two separate outputs. One is an open-drain P-channel, the other an open-drain N-channel. They have distinct current sourcing/sinking capabilities to independently control the rise and fall times of the MOSFET gate. Add a resistor in series with P\_OUT/N\_OUT to slow the corresponding rise/fall time of the MOSFET gate.

### \_Applications Information

# Supply Bypassing, Device Grounding, and Placement

Ample supply bypassing and device grounding are extremely important because when large external capacitive loads are driven, the peak current at the V+ pin can approach 1.3A, while at the GND pin the peak current can approach 7.6A. VCC drops and ground shifts are forms of negative feedback for inverters and, if excessive, can cause multiple switching when the INinput is used and the input slew rate is low. The device driving the input should be referenced to the MAX5048A/MAX5048B GND pin especially when the INinput is used. Ground shifts due to insufficient device grounding may disturb other circuits sharing the same AC ground return path. Any series inductance in the V+. P OUT, N OUT and/or GND paths can cause oscillations due to the very high di/dt that results when the MAX5048A/MAX5048B are switched with any capacitive load. A 0.1µF or larger value ceramic capacitor is recommended bypassing V+ to GND and placed as close to the pins as possible. When driving very large loads (e.g., 10nF) at minimum rise time, 10µF or more of parallel storage capacitance is recommended. A ground plane is highly recommended to minimize ground return resistance and series inductance. Care should be taken to place the MAX5048A/MAX5048B as close as possible to the external MOSFET being driven to further minimize board inductance and AC path resistance.

#### **Power Dissipation**

Power dissipation of the MAX5048A/MAX5048B consists of three components, caused by the quiescent current, capacitive charge and discharge of internal nodes, and the output current (either capacitive or resistive load). The sum of these components must be kept below the maximum power-dissipation limit.

# 7.6A, 12ns, SOT23/TDFN, MOSFET Driver

Figure 1. Timing Diagram and Test Circuit

The quiescent current is 0.95mA typical. The current required to charge and discharge the internal nodes is frequency dependent (see the *Typical Operating Characteristics*). The MAX5048A/MAX5048B power dissipation when driving a ground referenced resistive load is:

$$P = D \times RON(MAX) \times ILOAD^2$$

where D is the fraction of the period the MAX5048A/MAX5048Bs' output pulls high,  $R_{ON}$  (MAX) is the maximum on-resistance of the device with the output high (P-channel), and  $I_{LOAD}$  is the output load current of the MAX5048A/MAX5048B.

For capacitive loads, the power dissipation is:

$$P = C_{LOAD} \times (V+)^2 \times FREQ$$

where C<sub>LOAD</sub> is the capacitive load, V+ is the supply voltage, and FREQ is the switching frequency.

#### **Layout Information**

The MOSFET drivers MAX5048A/MAX5048B source-and-sink large currents to create very fast rise and fall edges at the gate of the switching MOSFET. The high di/dt can cause unacceptable ringing if the trace lengths and impedances are not well controlled. The following PCB layout guidelines are recommended when designing with the MAX5048A/MAX5048B:

- Place one or more 0.1µF decoupling ceramic capacitor(s) from V+ to GND as close to the device as possible. At least one storage capacitor of 10µF (min) should be located on the PC board with a low resistance path to the V+ pin of the MAX5048A/MAX5048B.

- There are two AC current loops formed between the device and the gate of the MOSFET being driven. The MOSFET looks like a large capacitance from gate to source when the gate is being pulled low. The active current loop is from N\_OUT of the MAX5048A/MAX5048B to the MOSFET gate to the MOSFET source and to GND of the MAX5048A/ MAX5048B. When the gate of the MOSFET is being pulled high, the active current loop is from P\_OUT of the MAX5048A/MAX5048B to the MOSFET gate to the MOSFET source to the GND terminal of the decoupling capacitor to the V+ terminal of the decoupling capacitor and to the V+ terminal of the MAX5048A/MAX5048B. While the charging current loop is important, the discharging current loop is critical. It is important to minimize the physical distance and the impedance in these AC current paths.

- In a multilayer PCB, the component surface layer surrounding the MAX5048A/MAX5048B should consist of a GND plane containing the discharging and charging current loops.

# 7.6A, 12ns, SOT23/TDFN, MOSFET Driver

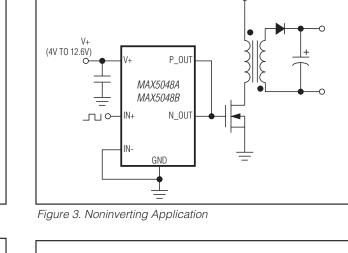

Figure 2. MAX5048A/MAX5048B Functional Diagram

Figure 4. Boost Converter

Figure 5. MAX5048A/MAX5048B in High-Power Synchronous Buck Converter

# 7.6A, 12ns, SOT23/TDFN, MOSFET Driver

### Pin Configurations (continued)

### \_Package Information

For the latest package outline information and land patterns (footprints), go to <a href="www.maximintegrated.com/package">www.maximintegrated.com/package</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE<br>TYPE | PACKAGE<br>CODE | OUTLINE NO.    | LAND<br>PATTERN NO. |

|-----------------|-----------------|----------------|---------------------|

| 6 SOT23         | U6F+6           | <u>21-0058</u> | <u>90-0175</u>      |

| 6 TDFN          | _               | 21-0137        | 90-0058             |

\_Chip Information

PROCESS: BICMOS

# 7.6A, 12ns, SOT23/TDFN, MOSFET Driver

### **Revision History**

| REVISION<br>NUMBER | REVISION DATE | DESCRIPTION                                                                              | PAGES<br>CHANGED |

|--------------------|---------------|------------------------------------------------------------------------------------------|------------------|

| 5                  | 11/12         | 11/12 Added "+" lead(Pb)-free/RoHS-compliant designations to <i>Ordering Information</i> |                  |

| 6                  | 10/14         | Updated Driver Output Resistance—Pulling Down specifications                             | 2                |

Maxim Integrated cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim Integrated product. No circuit patent licenses are implied. Maxim Integrated reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

## Maxim Integrated:

<u>MAX5048BAUT+T</u> <u>MAX5048BAUT-T</u> <u>MAX5048AATT+T</u> <u>MAX5048AAUT#TG16</u> <u>MAX5048BATT+T</u> MAX5048BAUT#TG16