# SMART SLAVE IC WITH INTEGRATED CURRENT AND TEMPERATURE SENSORS

| Device Type | Operating<br>Current | Input Voltage |  |

|-------------|----------------------|---------------|--|

| VT1697SB    | 55A Per Phase        | 8.5V to 14.0V |  |

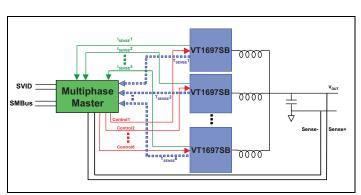

The VT1697SB is a feature-rich smart slave IC designed to work with Maxim's seventh-generation masters to implement a high-density multiphase voltage regulator. Up to six smart slave ICs, plus a master IC, provide a compact synchronous buck converter that includes accurate individual phase-current and temperature reporting via SMBus/PMBus. This smart slave device includes protection circuits for overtemperature, VX short, all power supplies UVLO faults and main power supply OVLO fault. If a fault is detected, the slave IC will immediately shut down and send a fault signal to the master IC.

Monolithic integration and advanced packaging technologies allow practical per-phase, high switching frequencies with significantly lower losses than alternative implementations. Smart slave devices are designed to support phase-shedding and DCM modes for efficiency optimization over a wide range of load currents. High per-phase current-capability designs with low  $C_{\text{OUT}}$  enable a design with fewer phases and a smaller footprint.

The VT1697SB is packaged in a QFN package with exposed topside thermal pads. Top-side cooling allows improved heat transfer to ambient and reduces PC board and component temperatures.

#### **FEATURES AND BENEFITS**

- Increased Power Density with Fewer External Components

- Monolithic Integration For Reduced Parasitics

- 4-Phase Scalable Architecture Compatible with Coupled Inductors

- 94% Peak Efficiency

- Top-Side Cooling For Improved Heat Transfer To Ambient

- Accurate Telemetry and Monitoring Provides Real-Time Reporting of Critical Parameters

- PMBus Compliant Interface via Master Controller for Telemetry and Power Management

- Junction Temperature Monitoring & Reporting

- Per-Phase Current Reporting

- Advanced Self-Protection Features Protects System and IC

- Overcurrent Protection

- Overtemperature Protection

- Boost Voltage UVLO

- VX Short Protection

#### **APPLICATIONS**

- Communication and Networking Equipment

- Servers and Storage Equipment

- High-Current Voltage Regulators

- Networking ASICs

- FPGAs

- Microprocessor Chipsets

- Memory

Figure 1: Basic Application Circuit

## **Ordering Information**

| Part Number                 | Description               | Package            | <b>Drawing Number</b> | Shipping Method   | Package Marking |

|-----------------------------|---------------------------|--------------------|-----------------------|-------------------|-----------------|

| RoHS Compliant <sup>3</sup> |                           |                    |                       |                   |                 |

| VT1697SBFQX                 | 55A smart slave<br>Device | QFN-16<br>[Type G] | ES AP-2896            | 2.5ku Tape & Reel | VT1697SBF       |

#### ABSOLUTE MAXIMUM RATINGS<sup>1</sup>

| Supply Voltage (12V)                                         | 0.3V to 16V   |

|--------------------------------------------------------------|---------------|

| Supply & Input Pin Voltages (1.8V)                           | 0.3V to 2.5V  |

| Switching Node Voltage (VX) DC                               | 0.3V to 16V   |

| Switching Node Voltage (VX) 25ns <sup>2</sup>                | 10V to 23V    |

| V <sub>DDH</sub> Pin - VX Pin Differential 25ns <sup>4</sup> | 10V to 23V    |

| BST Pin (BST) DC                                             | 0.3V to 20V   |

| BST Pin (BST) 25ns                                           | 6.0V to 27V   |

| BST Pin - VX Pin Differential                                | 2.5V          |

| Operating Junction Temperature (T <sub>J</sub> )             | 150°C         |

| Storage Temperature Range                                    | 65°C to 150°C |

| Peak Reflow Temperature                                      | 260°C         |

#### **OPERATING RATINGS**

| 12V Supply (V <sub>DDH</sub> )         | 8.5V to 14.0V    |

|----------------------------------------|------------------|

| Junction Temperature (T <sub>J</sub> ) | 40°C to 125°C    |

| Frequency (Fsw)                        | 300kHz to 1.3MHz |

| THERMAL RATINGS                        |                  |

| VT1697SB ⊕ <sub>JC</sub> Max           | 0.42°C/W         |

- **Note 1:** Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only; functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

- Note 2: The 25ns rating is the allowable voltage that the VX node may exceed the -0.3V to 16V ratings in either positive or negative direction for up to 25ns per cycle.

- Note 3: These products are completely Halogen-free and Pb-free, employing special materials sets: molding compounds/die attach materials and 100% matte tin plate including anneal. These products are RoHS compliant with an -e3 termination finish and are compatible with both SnPb and Pb-free soldering operations. These products are MSL classified at peak reflow temperatures that meet JEDEC JSTD-020.

- Note 4: The V<sub>DDH</sub> input pin voltage AC should not exceed 19V (25ns). This measurement is taken at the V<sub>DDH</sub> pin referenced to V<sub>SS</sub> pin immediately adjacent using a high frequency scope probe with I<sub>LOAD</sub> at I<sub>MAX</sub>. A high-frequency input bypass capacitor must be located less than 60mils (1.524mm) from the V<sub>DDH</sub> pin and the Maxim device per our design guidelines.

## **Electrical Characteristics**

$V_{DD} = V_{CC} = 1.71V$  - 1.98V,  $V_{DDH} = 12V$ . The \* symbol denotes specifications which apply over the following temperature range:  $T_J = 0$  to 125°C, otherwise specifications are for  $T_J = 25$ °C. The # symbol denotes specifications which apply over the following temperature range:  $T_J = -25$  to  $125^{\circ}$ C.

| Symbol                            | Parameter                                            | Conditions                                                | Min                    | Тур         | Max      | Units       |

|-----------------------------------|------------------------------------------------------|-----------------------------------------------------------|------------------------|-------------|----------|-------------|

| Supply Voltage                    | ges , Supply Current                                 | <u> </u>                                                  | •                      | •           |          |             |

| V <sub>DD</sub> , V <sub>CC</sub> | Bias Supply Voltage                                  |                                                           | 1.71                   |             | 1.98     | V           |

| V <sub>DDH</sub>                  | Power Train Input Voltage                            |                                                           | 8.5                    | 12.0        | 14.0     | V           |

|                                   |                                                      | Shutdown (See Note 1)                                     |                        | 0.5         | 2        | μΑ          |

|                                   |                                                      | Inactive, No Switching (See Note 2)                       |                        | 3.2         | 5.0      | mA          |

| I <sub>CC</sub> + I <sub>DD</sub> | 1.8V Bias Supply Current                             | Load = 0A, V <sub>OUT</sub> = 1.8V, Fsw = 1.5MHz          |                        | 43          | 61       | mA          |

|                                   |                                                      | Load = 0A, V <sub>OUT</sub> = 1.8V, Fsw = 300KHz          |                        | 14          | 20       | mA          |

|                                   |                                                      | Load = 0A, V <sub>OUT</sub> = 1.8V, Fsw = 600KHz          |                        | 29          | 41       | mA          |

| I <sub>DDH</sub>                  | 12V Bias Supply Current                              | Shutdown (See Note 1) Inactive, No Switching (See Note 2) |                        | 1.3<br>6.5  | 10<br>20 | μA<br>μA    |

| I <sub>RECON</sub> Speci          | fication                                             | inactive, No Switching (See Note 2)                       |                        | 6.5         | 20       | μA          |

| A <sub>I</sub>                    | Current gain (I <sub>L</sub> to I <sub>SENSE</sub> ) | -70A < I <sub>L</sub> < 70A                               | 95000                  | 100000      | 105000   | A/A         |

|                                   | Sensor Specifications                                | -704 \ 1[ \ 704                                           | 95000                  | 100000      | 105000   | _ A/A       |

| -                                 | <u> </u>                                             |                                                           |                        | 1           | 450      | 1 00        |

| T <sub>RANGE</sub>                | Temperature Sensor Dynamic Range                     |                                                           | 0                      | 0.04        | 150      | °C<br>mV/°C |

| A <sub>TEMP</sub>                 | Temperature Sensor Gain Temperature Sensor Voltage   | T <sub>.J</sub> = 0°C                                     |                        | 3.01<br>832 |          |             |

| Protection Fe                     | I - 1                                                | 13 = 0 0                                                  |                        | 032         |          | mV          |

| 11010011011110                    | V <sub>DD</sub> UVLO Threshold (Rising)              |                                                           | 1.47                   | 1.57        | 1.64     | Τv          |

| $V_{DD\_UVLO}$                    | V <sub>DD</sub> UVLO Threshold (Falling)             |                                                           | 1.41                   | 1.5         | 1.58     | V           |

|                                   | ·                                                    |                                                           |                        |             |          | V           |

| V <sub>DDH_OVLO</sub>             | V <sub>DDH</sub> OVLO Threshold (Rising)             |                                                           | 15.48                  | 16          | 16.41    | -           |

|                                   | V <sub>DDH</sub> OVLO Threshold (Falling)            |                                                           | 14.95                  | 15.5        | 15.81    | V           |

| V <sub>DDH UVLO</sub>             | V <sub>DDH</sub> UVLO Threshold (Rising)             |                                                           | 4.05                   | 4.27        | 4.40     | V           |

|                                   | V <sub>DDH</sub> UVLO Threshold (Falling)            |                                                           | 3.90                   | 4.09        | 4.25     | V           |

| V <sub>BST UVLO</sub>             | V <sub>BST</sub> UVLO Threshold (Rising)             | Note 3                                                    | 1.39                   | 1.52        | 1.66     | V           |

| VBS1_UVLO                         | V <sub>BST</sub> UVLO Threshold (Falling)            | Note 3                                                    | 1.32                   | 1.45        | 1.57     | V           |

|                                   | Peak Positive OCP Clamp Level                        |                                                           | 59                     | 67          | 80       | Α           |

|                                   | Peak Positive OCP Clamp Delay                        |                                                           |                        |             | 63       | ns          |

| 000                               | Peak Positive OCP Shutdown Level                     |                                                           | 99                     | 110         | 121      | Α           |

| OCP                               | Peak Positive OCP Shutdown Delay                     |                                                           |                        |             | 42       | ns          |

|                                   | Peak Negative OCP Clamp Level                        |                                                           | -79.1                  | -71.9       | -64.7    | Α           |

|                                   | Peak Negative OCP Delay                              |                                                           |                        |             | 110      | ns          |

| OTP                               | Overtemperature Shutdown                             | Rising Threshold                                          | 140                    | 150         | 165      | °C          |

| PWM Input                         |                                                      | <u>,                                      </u>            |                        | •           |          |             |

| V <sub>IH</sub>                   | Input Voltage, High State                            |                                                           | V <sub>DD</sub> - 0.20 |             |          | V           |

| $V_{IL}$                          | Input Voltage, Low State                             |                                                           |                        |             | 0.20     | V           |

| _                                 | Tristate Control Threshold (V <sub>IN</sub> Rising)  |                                                           |                        | 0.63        |          | V           |

| TS_FAULTB I                       | nput                                                 |                                                           |                        |             |          |             |

| V <sub>IH</sub>                   | TS_FAULTB Digital Threshold V <sub>IH</sub>          |                                                           | 0.41                   |             |          | V           |

| V <sub>IL</sub>                   | TS_FAULTB Digital Threshold V <sub>IL</sub>          |                                                           |                        |             | 0.17     | V           |

|                                   |                                                      | 1                                                         |                        | L           |          |             |

T<sub>SENSE</sub>, PWM and I<sub>SENSE</sub> pins of the slave are pulled LOW by the master. The slave is in this state before master OE is enabled. Inactive, no switching: PWM signal is tristated by the master. The slave is in this mode when the master sheds a phase (temporarily disabling this slave) to save Note 2: power at lighter loads.

<sup>.</sup>  $V_{\text{BST\_UVLO}}$  is measured with respect to VX and not from ground. Note 3:

## **Typical Operating Characteristics**

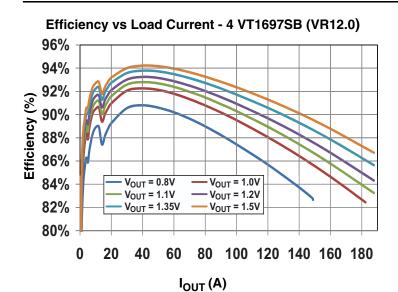

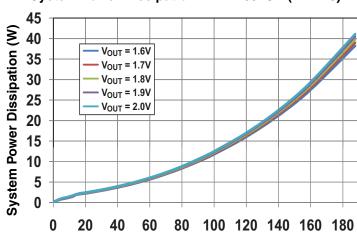

Master:  $T_A = 25^{\circ}C$ ; Fsw = 600kHz

Conditions:  $V_{IN} = 12V$

$V_{BIAS} = 1.8V$

Inductor: CLB1108-4-50TR-R

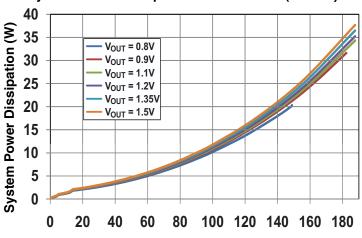

#### System Power Dissipation - 4 VT1697SB (VR12.0)

I<sub>OUT</sub> (A)

Conditions:  $V_{IN} = 12V$

$V_{BIAS} = 1.8V$

Inductor: CLB1108-4-50TR-R

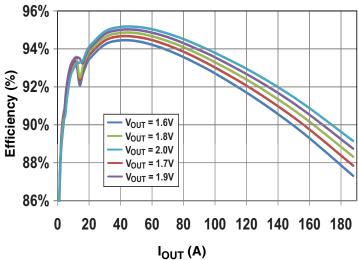

#### Efficiency vs Load Current - 4 VT1697SB (VR12.5)

Conditions:  $V_{IN} = 12V$  $V_{BIAS} = 1.8V$

Inductor: CLB1108-4-50TR-R

#### System Power Dissipation - 4 VT1697SB (VR12.5)

I<sub>OUT</sub> (A) Conditions:  $V_{IN} = 12V$

$V_{BIAS} = 1.8V$

Inductor: CLB1108-4-50TR-R

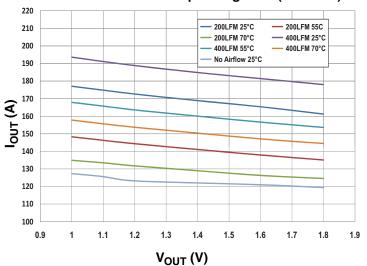

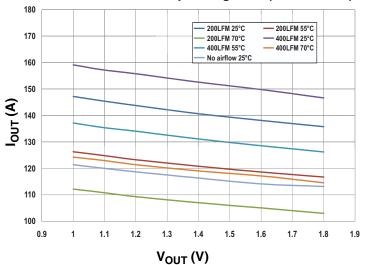

## **Typical Operating Characteristics**

Master:  $T_A = 25^{\circ}C$ ; Fsw = 600kHz

#### VT1697SB 4-Phase Safe Operating Area (Heatsink)

Conditions:  $V_{IN} = 12V$  $V_{BIAS} = 1.8V$

Inductor: CL1108-4-50TR-R

#### VT1697SB 4-Phase Safe Operating Area (No Heatsink)

Conditions:  $V_{IN} = 12V$

$V_{BIAS} = 1.8V$

Inductor: CL1108-4-50TR-R

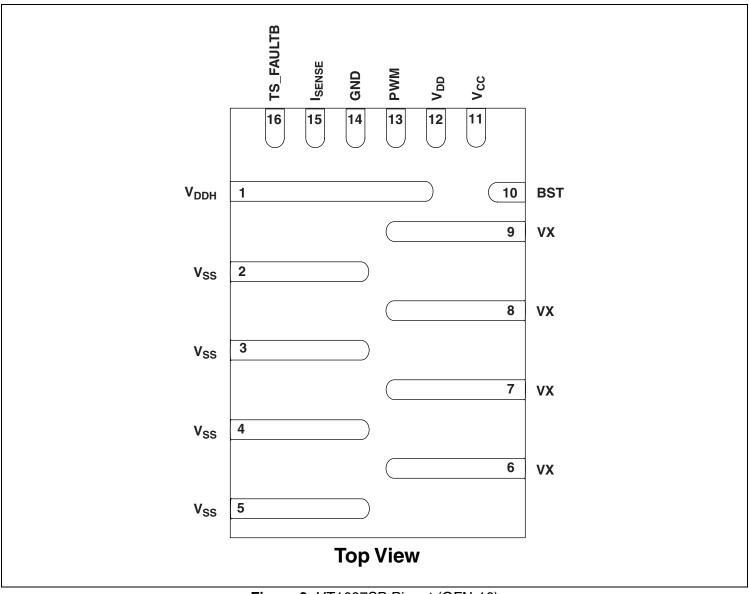

## **Pinout and Block Diagrams**

Figure 2: VT1697SB Pinout (QFN-16)

#### PIN INFORMATION FOR VT1697SB SMART SLAVE DEVICE

**V**<sub>DDH</sub> (Pin 1): 12V input supply voltage node. This node connects to the 12V input power supply source. High-frequency decoupling capacitors must be placed in close proximity to the slave IC on the same side as the VT1697SB. See Table 2 for reference.

**V<sub>SS</sub>** (Pins 2-5): Power switch ground node. These nodes normally connect directly to the ground plane.

**VX** (Pins 6-9): Switching node. These nodes connect the switching node of the power devices to the output inductor.

**BST** (Pin 10): Bootstrap supply for high-side drivers.

$\mathbf{V_{CC}}$  (Pin 11): 1.8V supply for low-side drivers.

**V<sub>DD</sub>** (Pin 12): 1.8V supply for control circuits.

**PWM** (Pin 13): PWM input node. Connect this node to the PWM output pin from the Master.

GND (Pin 14): Ground for control circuits.

**I**<sub>SENSE</sub> (Pin 15): Current sense output node. Connect this node to the current sense input of the Master through a simple passive filter.

**TS\_FAULTB** (Pin 16): Temperature sense and fault output node. Connect this node to the temperature sense pin of the Master through a simple passive filter.

## **Pinout and Block Diagrams**

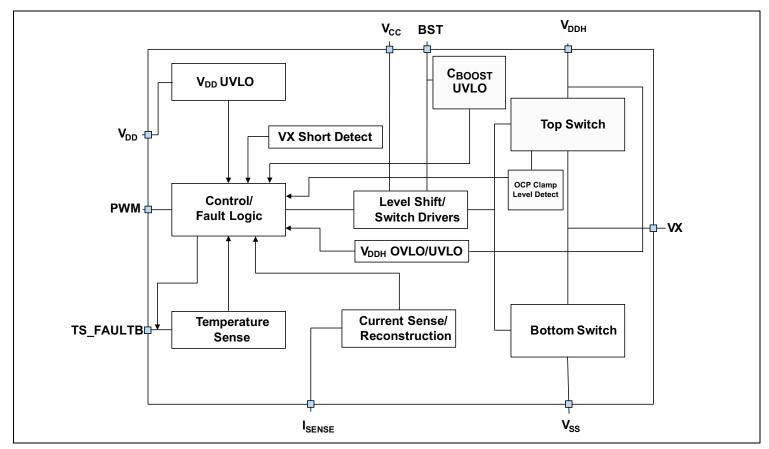

Figure 3: IC Block Diagram

### **Theory of Operation**

#### **VOLTAGE REGULATION**

Maxim smart slave ICs provide the control logic, drivers, monitoring circuits and power semiconductors for a synchronous buck converter with fault protection, status monitoring and accurate lossless current sensing. Phases are controlled by the Master IC independently by separate phase control signals.

#### **Power Switch Control and Drivers**

The smart slave ICs operate in conjunction with a Maxim Master IC. The Master controller will configure the voltage regulator based on its configuration resistors and the number of phases populated. The smart slave device's switching is controlled by the proprietary command signals on the phase control lines. The phase control signal has three defined states: high, low and a "tri-state". "Tri-state" is used for phase shedding and DCM modes. An external boost capacitor is required to supply the voltage for the high-side switch driver. VDD and VCC are brought out separately to allow separate decoupling to improve noise immunity on the VDD rail.

#### **Current Sense Output**

The integrated lossless current sense (or "current reconstruction") produces a precise ratiometric current sense signal for both positive and negative currents which is sent to the master as an analog current signal. This current sense technology provides accurate current information over load and temperature that is not affected by tolerances of passive elements such as the output inductor, resistors and capacitors.

#### **Phase Configuration**

The ability for the Master to dynamically disable and reenable a phase is an integral part of the Maxim Master/Slave architecture. The Master sets the phase control signal to "tristate" to disable a phase. The same state is used to control DCM operation. When using a coupled inductor, a proprietary mode (Coupled Inductor Mode) may be set by the master and communicated to the smart slave via the phase control signal to minimize losses due to coupled currents in inactive phases.

#### PROTECTION CIRCUITS

#### **Overcurrent Protection**

The smart slave ICs incorporate instantaneous overcurrent fault protection using the lossless current sense/reconstruction. This overcurrent protection is separate from the system overcurrent protection, and is intended to operate only in extreme fault conditions to protect the IC and other components. The system overcurrent protection set by the master should be set with sufficient margin below the individual Slave's threshold to ensure correct system operation.

For current sourcing operation, if the instantaneous current in the top switch (based on the current sense/reconstruction circuit) exceeds the overcurrent protection value shown in the Electrical Characteristics table, the slave will regulate the period of the top-side switch so as to keep its peak current at a safe level. The protection threshold has been set to ensure

that the IC's maximum allowable peak current is not exceeded when using the recommended inductors. The sourcing current limiting is not considered a hard fault condition for slave, and therefore TS\_FAULTB will not be asserted. Since clamping is based on instantaneous reconstructed current, the ripple current must be considered when calculating the maximum average current per slave. The maximum average current before clamping can be calculated as shown in Equation 1. Note that the clamping is based on reconstructed current. Limits shown in the Electrical Characteristics table for Clamp Level reflect expected variations in application conditions and external component characteristics. Also note that the master (i.e., system) overcurrent protection should be set lower than the corresponding slaves' maximum operating current as stated above.

#### **Equation 1**

$$\begin{array}{lll} \text{Maximum Average DC Slave Current} &=& \text{OCP} - \frac{I_{RIPPLE}}{2} \\ \\ \text{where,} & \text{OCP} &=& \text{Peak OCP Clamp Level (A)} \\ I_{RIPPLE} &=& \text{Peak-to-Peak Inductor Ripple Current (A)} \\ \end{array}$$

For current sinking protection, if the negative overcurrent protection threshold is reached, the slave limits the current and TS FAULTB is not asserted.

The VT1697SB implements an additional OCP shutdown level (beyond the clamp levels). If the current in the top switch exceeds the OCP shutdown level (shown in the Electrical Characteristics table), the IC is turned OFF and fault is reported by asserting FAULTB pin. The slave is then latched OFF until the power is cycled.

#### V<sub>DD</sub> and V<sub>BOOST</sub> Undervoltage Lockout

The smart slave ICs include undervoltage lockout circuits:  $V_{DD}$  and  $V_{BOOST}$ . For power sequencing guidelines and operation with separate bias rails for master and slaves, please refer to appropriate master data sheet.  $V_{BOOST}$  UVLO is active at all times after the initial system start up. It is not active during the initial system power on state (before regulation is enabled) and is activated approximately 20 $\mu$ s after initial start up. If either of these UVLO circuits is tripped during operation, the smart slave will stop switching and a fault signal (TS\_FAULTB pulled LOW) will be sent to the master.

## **Theory of Operation**

#### V<sub>IN</sub> (V<sub>DDH</sub>) Undervoltage and Overvoltage Lockout

The slaves include protection circuits that shut down the slave and assert TS\_FAULTB if  $V_{DDH}$  is above or below the correct operating range. If either of these circuits is tripped during operation, the slave will stop switching and a fault signal (TS\_FAULTB pulled LOW) will be sent to the master.

## Temperature Sensing and Overtemperature Protection

Each smart slave IC incorporates an accurate die temperature sensor. The temperature sense signal is sent to the master as an analog signal via the temperature sense pin. The actual temperature of each smart slave device is then made available via the SMBus of the master. The smart slave IC also includes overtemperature protection. If the trip point is reached, the IC immediately shuts down and the fault is reported to the master via the TS FAULTB pin.

Table 1: Fault Detection and Protection Circuits

#### **VX Short Protection**

The smart slave ICs include a VX short detection to detect a local short circuit from the VX node to either  $V_{DDH}$  or ground. If such a fault is detected, the slave shuts down and communicates a fault to the master via the TS\_FAULTB pin.

#### TS FAULTB Signal

If a fault is detected, the smart slave sends a signal to the master by pulling the TS\_FAULTB pin to ground. Under normal conditions, this pin is used to send an accurate analog representation of the slave temperature. If a fault is detected, this pin is asserted LOW to indicate that a fault condition was detected by a slave IC. Table 1 shows the faults that result in this signal being asserted. For a latching fault, the fault must be cleared and the  $V_{\mbox{\scriptsize DD}}$  power cycled to re-enable the IC (for non-latching faults, see note below the Table 1.). Please refer to the applicable master IC data sheet for details about han-

| Fault                 | Description                                    | Туре                         | Fault Flag (TS_FAULTB) |

|-----------------------|------------------------------------------------|------------------------------|------------------------|

| Boost UVLO            | Undervoltage Lockout on Boost Supply           | Shutdown*                    | Asserted               |

| V <sub>DDH</sub> UVLO | Undervoltage Lockout on V <sub>DDH</sub>       | Shutdown*                    | Asserted               |

| V <sub>DDH</sub> OVLO | Overvoltage Lockout Signal on V <sub>DDH</sub> | Shutdown*                    | Asserted               |

| V <sub>DD</sub> UVLO  | Undervoltage Lockout Signal on V <sub>DD</sub> | Shutdown*                    | Asserted               |

| V <sub>X</sub> Short  | VX Short-to-Ground or V <sub>DDH</sub>         | Shutdown                     | Asserted               |

| POCP (Sourcing)       | Positive/Sourcing Overcurrent Protection       | Cycle-by-Cycle Current Limit | Not Asserted           |

| NOCP (Sinking)        | Negative/Sinking Overcurrent Protection        | Cycle-by-Cycle Current Limit | Not Asserted           |

| OTP                   | Overtemperature Protection                     | Shutdown                     | Asserted               |

<sup>\*</sup> VDDH\_UVLO, VDDH\_OVLO, VBST\_UVLO and VDD\_UVLO are non-latching faults. If a non-latching fault is detected by the slave, it will assert TS\_FAULTB signal low and stop switching. The slave resumes switching and de-asserts TS\_FAULTB around 37µs from when the fault condition is removed. Please refer to the master data sheet for master response to TS\_FAULTB asserted LOW by the slave device.

#### **Theory of Operation**

#### **DESIGN CONSIDERATIONS**

#### **Phase Current Sharing and Steering Control**

Maxim master/slave chipsets offer options for thermal balancing in applications where one or more phases have different thermal characteristics. The current sense and chipset regulation system offer the potential for current steering, where a percentage of current can be steered away from any phase, allowing that phase to operate at a different current than the other phases. This allows a precise scaling of current in any slave(s) to achieve proper thermal balance between phases. Refer to the applicable Maxim master IC datasheet for more information on how to program this feature.

#### **Thermal Path and Printed Circuit Board Design**

The smart slave IC has an exposed pad on the top-side of the package that is designed as an additional thermal path. This pad is electrically connected to  $A_{GND}/V_{SS}$ , but is not intended for use as an electrical connection. Since there is normally sufficient airflow above the regulator, conducting heat from the top of the package results in a low junction-to-ambient thermal impedance, and hence lower junction temperature. This method provides additional thermal path to the heat flow from the die to the PCB to ambient and also reduces the temperature of the PCB. Thermal performance is presented for various thermal conditions and airflow rates in the SOA plots.

#### **Printed Circuit Board (PCB) Layout**

PCB layout can significantly affect the performance of the regulator. Careful attention should be paid to the location of the input capacitors and the output inductor which should be placed close to the IC. The VX traces include large voltage swings (greater than 12V) with dv/dt greater than 10V/ns. It is recommended that these traces are not only kept short, but also are shielded with a ground plane immediately beneath.

Gerber files with layout information and complete reference designs can be obtained by contacting a Maxim account representative. Please contact Maxim to obtain QFN layout guidelines for optimal design.

**Table 2:** Typical Boost, Filtering and Decoupling Capacitor Requirements

| Description                                  | Value       | Туре      | Package   | Qty |

|----------------------------------------------|-------------|-----------|-----------|-----|

| V <sub>DD</sub> Capacitor                    | 0.1μF/6.3V  | X7R/125°C | 0603      | 1   |

| V <sub>CC</sub> Capacitor                    | 1μF/6.3V    | X7R/125°C | 0603      | 1   |

| Boost Capacitor                              | 0.22μF/6.3V | X7R/125°C | 0402      | 1   |

| V <sub>DD</sub> R <sub>FILTER</sub>          | 10Ω         | 1/16W 1%  | 0402      | 1   |

| V <sub>DDH</sub> HF Capacitor <sup>1</sup>   | 1μF/16V     | X7R/125°C | 0603      | 2   |

| V <sub>DDH</sub> HF Capacitor <sup>1</sup>   | 0.1μF/16V   | X7R/125°C | 0402      | 2   |

| V <sub>DDH</sub> Bulk Capacitor <sup>2</sup> | 10μF/16V    | X5R       | 0805/1206 | 2   |

Note 1: All V<sub>DDH</sub> high-frequency capacitors must be placed in close proximity to the slave IC and on the same side of the PCB as the slave IC. Please refer to Maxim's layout guideline for component placement requirements and recommendations.

Note 2: For operation below 10.8V, two  $22\mu F$  bulk capacitor are recom-

mended instead of two  $10\mu F$  capacitors.

Note 3: V<sub>CC</sub> should be directly connected to bias supply.

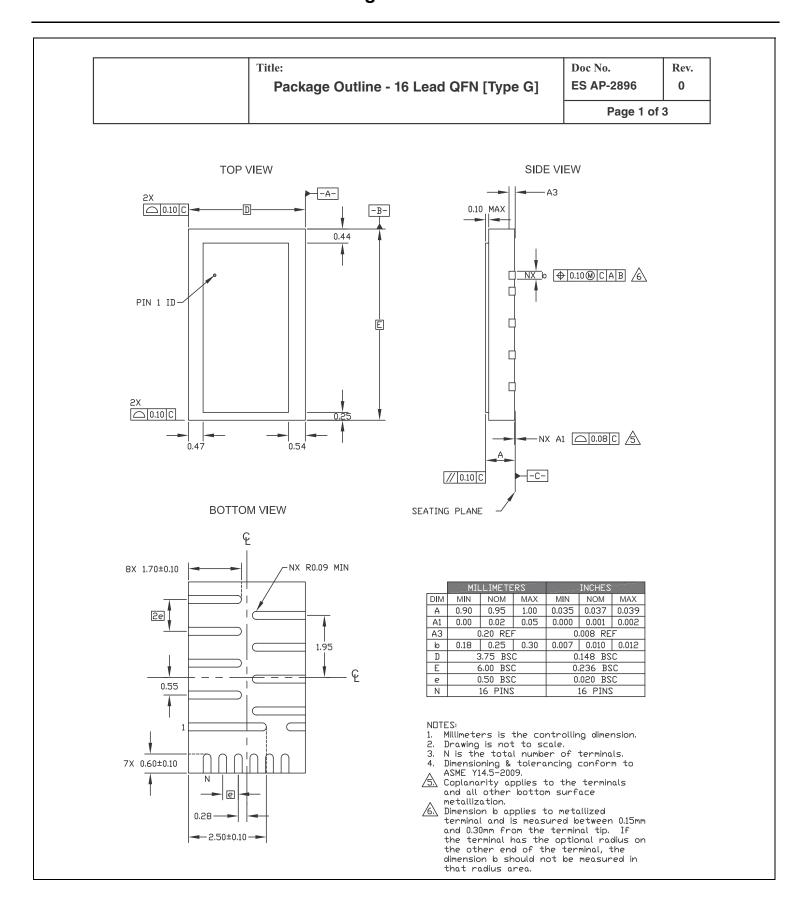

## **Package Dimensions**

## **Package Dimensions**

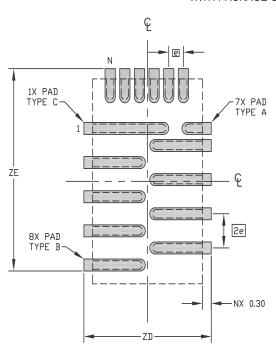

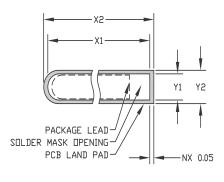

#### RECOMMENDED LAND PATTERN WITH PACKAGE OVERLAY

|     | MILLIMETERS |                     |     |     | INCHES    |     |  |

|-----|-------------|---------------------|-----|-----|-----------|-----|--|

| DIM | MIN         | NOM                 | MAX | MIN | NOM       | MAX |  |

| е   | (           | 0.50 BSC<br>16 PINS |     |     | 0.020 BSC |     |  |

| N   |             |                     |     |     | 16 PINS   |     |  |

| ZD  | 4           | 4.35 REF            |     |     | .171 RE   | F   |  |

| ZE  | 5.93 REF    |                     |     | 0.  | 233 RE    | F   |  |

#### PAD DETAIL INFORMATION

|     | MILLIMETERS |        |        |        | INCHF2 |        |

|-----|-------------|--------|--------|--------|--------|--------|

| DIM | TYPE A      | TYPE B | TYPE C | TYPE A | TYPE B | TYPE C |

| Y1  | 0.28        | 0.28   | 0.28   | 0.011  | 0.011  | 0.011  |

| Y2  | 0.35        | 0.35   | 0.35   | 0.014  | 0.014  | 0.014  |

| X1  | 0.90        | 2.00   | 2.80   | 0.035  | 0.079  | 0.110  |

| X5  | 1.00        | 2.10   | 2.90   | 0.039  | 0.083  | 0.114  |

- Millimeters is the controlling dimension

Drawing is not to scale.

N is the total number of terminals. Millimeters is the controlling dimension.

## **Revision History**

#### **REVISION HISTORY**

| Revision | Description                                                                                                                                                                                                                     | Date  |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 0        | Initial Data Sheet                                                                                                                                                                                                              | N/A   |

| 1        | Changed Status of VT1697SB to New Product. Updated $I_{CC} + I_{DD}$ , $V_{BST\_UVLO}$ and NOCP specifications in the Electrical Characteristics table. Made a change in the "filter" (from $V_{DDH}$ to $V_{DD}$ ) in Table 2. | 1/14  |

| 2        | Updated to Maxim Template                                                                                                                                                                                                       | 2/14  |

| 3        | Updated Electrical Characteristics Table and Overcurrent Protection section. Updated Operating Current Rating to 55A. Removed all VT1677SB references from data sheet.                                                          | 9/14  |

| 4        | Removed "Scalable 120A Multiphase Solution in < 835mm <sup>2</sup> " in <i>Features and Benefits</i> section                                                                                                                    | 11/14 |

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim Integrated's website at www.maximintegrated.com.

Maxim Integrated cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim Integrated product. No circuit patent licenses are implied. Maxim Integrated reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.

Maxim Integrated and the Maxim Integrated logo are trademarks of Maxim Integrated Products, Inc.

© 2014 Maxim Integrated Products, Inc.

## **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Maxim Integrated:

VT1697SBFQ VT1697SBFQX