**Technical Data**

# Single Wire CAN Transceiver

The 33897 series provides a physical layer for digital communication using a Carrier Sense Multiple Access/Collision Resolution (CSMA/CR) data link operating over a single wire medium. This is more commonly referred to as single-wire Controller Area Network (SWCAN).

The 33897 series operates directly from a vehicle's 12 V battery system or a broad range of DC-power sources. It can operate at low or high (33.33 kbps or 83.33 kbps) data rates. A high-voltage wake-up feature allows the device to control the regulator used in support of the MCU and other logic. The device includes a control pin that can be used to put the module regulator into Sleep mode. The presence of a defined wake-up voltage level on the bus will reactivate the control line to turn the regulator and the system back ON.

The device complies with the GMW3089v2.4 General Motors Corporation specification.

## Features

- · Waveshaping for low Electromagnetic Interference (EMI)

- Detects and automatically handles loss of ground

- Worst-case Sleep mode current of only 60 μA

- · Current limit prevents damage due to bus shorts

- · Built-in thermal shutdown on bus output

- · Protected against vehicular electrical transients

- · Under-voltage lockout prevents false data with low battery

Document Number: MC33897 Rev. 18.0, 4/2012

## √RoHS

33897

## SINGLE-WIRE CAN TRANSCEIVER

| ORDERING INFORMATION                          |               |          |  |

|-----------------------------------------------|---------------|----------|--|

| Device Temperature<br>Range (T <sub>A</sub> ) |               | Package  |  |

| MCZ33897TEF/R2                                | -40 to 125 °C | 14 SOICN |  |

| *MC33897CTEF/R2                               |               |          |  |

|                                               |               |          |  |

\*Recommended device for all new designs

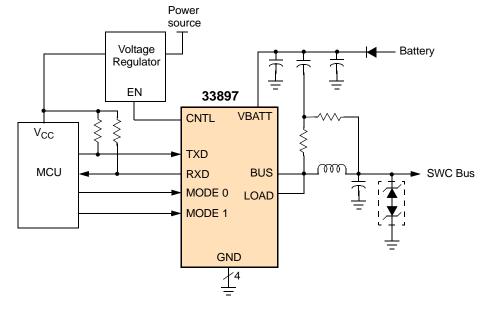

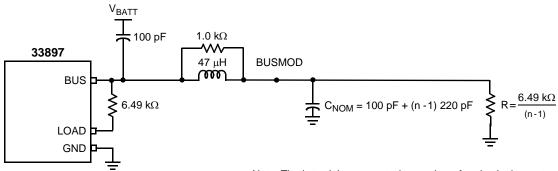

Figure 1. 33897 Simplified Application Diagram

Freescale Semiconductor, Inc. reserves the right to change the detail specifications, as may be required, to permit improvements in the design of its products. © Freescale Semiconductor, Inc., 2006 - 2012. All rights reserved.

# **DEVICE VARIATIONS**

## Table 1. Device Variations

| Part No. | Load Voltage Sleep Mode | See Page |

|----------|-------------------------|----------|

| 33897T   | 1.0 V Max               | Z        |

| *33897CT | 0.1 V Max               | <u>Z</u> |

\*Recommended device for all new designs

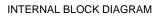

## **INTERNAL BLOCK DIAGRAM**

Figure 2. 33897 Simplified Internal Block Diagram

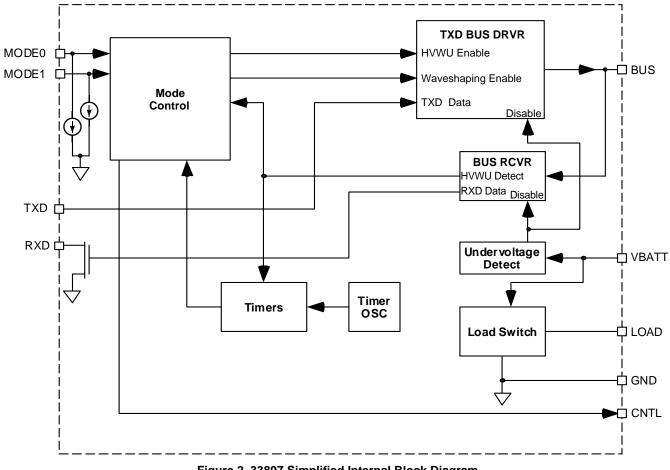

## **PIN CONNECTIONS**

Figure 3. 33897 Pin Connections

## Table 2. Pin Definitions

A functional description of each pin can be found in the Functional Pin Description section, beginning on page 12.

| 33897 Pin   | Pin Name        | Formal Name   | Definition                                                                                                                            |

|-------------|-----------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------|

| 1, 7, 8, 14 | GND             | Ground        | Electrical Common Ground and Heat removal. A good thermal path will also reduce the die temperature.                                  |

| 2           | TXD             | Transmit Data | Data input here will appear on the BUS pin. A logic [0] will assert the bus, a logic [1] will make the bus go to the recessive state. |

| 3, 4        | MODE0,<br>MODE1 | Mode Control  | These Pins control Sleep mode, Transmit Level, and Speed. They have weak pull-<br>downs.                                              |

| 5           | RXD             | Receive Data  | Open drain output of the data on BUS. A recessive bus = a logic [1], a dominant bus = logic [0]. An external pull-up is required.     |

| 6, 13       | NC              | No Connect    | No internal connection to these Pins. Pin 13 can be connected to GND.                                                                 |

| 9           | CNTL            | Control       | Provides a battery level logic signal.                                                                                                |

| 10          | VBATT           | Battery       | Power input. An external diode is needed for reverse battery protection.                                                              |

| 11          | LOAD            | Load          | The external bus load resistor connects here to prevent bus pull-up in the event of loss of module ground.                            |

| 12          | BUS             | Bus           | This pin connects to the bus through external components.                                                                             |

# **ELECTRICAL CHARACTERISTICS**

## **MAXIMUM RATINGS**

## Table 3. Maximum Ratings

All voltages are with respect to ground unless otherwise noted.

| Rating                                       | Symbol            | Value       | Unit |

|----------------------------------------------|-------------------|-------------|------|

| Electrical Ratings                           |                   |             |      |

| Supply Voltage                               | V <sub>BATT</sub> | -0.3 to 40  | V    |

| Input Logic Voltage                          | V <sub>IN</sub>   | -0.3 to 7.0 | V    |

| RXD Pin Voltage                              | V <sub>RXD</sub>  | -0.3 to 7.0 | V    |

| CNTL Pin Voltage                             | V <sub>CNTL</sub> | -0.3 to 40  | V    |

| ESD Voltage <sup>(1)</sup>                   | V <sub>ESD</sub>  |             | V    |

| Human Body Model                             |                   |             |      |

| All Pins Except BUS                          |                   | ±2000       |      |

| BUS Pin                                      |                   | ±4000       |      |

| Machine Model                                |                   | ±100        |      |

| Thermal Ratings                              |                   |             |      |

| Ambient Operating Temperature <sup>(1)</sup> | Т                 | -40 to 125  | °C   |

| Ambient Operating Temperature <sup>(1)</sup>                                  | Τ <sub>Α</sub>    | -40 to 125 | °C   |

|-------------------------------------------------------------------------------|-------------------|------------|------|

| Junction Operating Temperature                                                | TJ                | -40 to 150 | °C   |

| Storage Temperature                                                           | T <sub>STG</sub>  | -55 to 150 | °C   |

| Junction-to-Ambient Thermal Resistance                                        | $R_{	heta JA}$    | 150        | °C/W |

| Peak Package Reflow Temperature During Reflow <sup>(2)</sup> , <sup>(3)</sup> | T <sub>PPRT</sub> | Note 3.    | °C   |

Notes

1. ESD testing is performed in accordance with the Human Body Model ( $C_{ZAP} = 100 \text{ pF}$ ,  $R_{ZAP} = 1500 \Omega$ ), Machine Model ( $C_{ZAP} = 200 \text{ pF}$ ,  $R_{ZAP} = 0 \Omega$ ).

2. Pin soldering temperature limit is for 10 seconds maximum duration. Not designed for immersion soldering. Exceeding these limits may cause malfunction or permanent damage to the device.

Freescale's Package Reflow capability meets Pb-free requirements for JEDEC standard J-STD-020C. For Peak Package Reflow Temperature and Moisture Sensitivity Levels (MSL), Go to www.freescale.com, search by part number [e.g. remove prefixes/suffixes and enter the core ID to view all orderable parts. (i.e. MC33xxxD enter 33xxx), and review parametrics.

## STATIC ELECTRICAL CHARACTERISTICS

#### Table 4. Static Electrical Characteristics

Characteristics noted under conditions of -40 °C  $\leq$  T<sub>A</sub>  $\leq$  125 °C, unless otherwise stated. Voltages are relative to GND, unless otherwise noted. All positive currents are into the pin. All negative currents are out of the pin.

| Characteristic                                                                     | Symbol              | Min                     | Тур | Max               | Unit |

|------------------------------------------------------------------------------------|---------------------|-------------------------|-----|-------------------|------|

| GENERAL                                                                            |                     |                         |     |                   |      |

| Quiescent Current                                                                  |                     |                         |     |                   |      |

| Sleep                                                                              |                     |                         |     |                   |      |

| 5.0 V $\leq$ V <sub>BATT</sub> $\leq$ 13 V <sup>(4)</sup>                          | I <sub>QSLP</sub>   | -                       | 45  | 60                | μA   |

| Awake with Transmitter Disabled                                                    |                     |                         |     |                   |      |

| $5.0~V \le V_{BATT} \le 26.5~V$                                                    | I <sub>QATDIS</sub> | -                       | -   | 4.0               | mA   |

| Awake with Transmitter Enabled                                                     |                     |                         |     |                   | mA   |

| $5.0~V \leq V_{BATT} \leq 26.5~V$                                                  | I <sub>QATEN</sub>  | -                       | _   | 9.0               |      |

| Under-voltage Shutdown                                                             | V <sub>BATTUV</sub> | 4.0                     | -   | 5.0               | V    |

| Under-voltage Hysteresis                                                           | V <sub>UVHYS</sub>  | 0.1                     | -   | 0.5               | V    |

| Thermal Shutdown <sup>(5)</sup>                                                    | T <sub>SD</sub>     |                         |     |                   | °C   |

| $5.0~V \leq V_{BATT} \leq 26.5~V$                                                  |                     | 150                     | -   | 190               |      |

| Thermal Shutdown Hysteresis <sup>(5)</sup>                                         | T <sub>SDHYS</sub>  |                         |     |                   | °C   |

| $5.0~V \leq V_{BATT} \leq 26.5~V$                                                  |                     | 10                      | -   | 20                |      |

| LOGIC I/O, MODE0, MODE1, TXD, RXD                                                  | 1                   |                         |     | 1                 |      |

| Logic Input Low Level (MODE0, MODE1, and TXD)                                      | V <sub>IL</sub>     |                         |     |                   | V    |

| $5.0~V \leq V_{BATT} \leq 26.5~V$                                                  |                     | -                       | -   | 0.8               |      |

| Logic Input High Level (MODE0, MODE1, and TXD)                                     | V <sub>IH</sub>     |                         |     |                   | V    |

| $5.0~V \leq V_{BATT} \leq 26.5~V$                                                  |                     | 2.0                     | _   | _                 |      |

| Mode Pin Pull-down Current (MODE0 and MODE1)                                       | I <sub>PD</sub>     |                         |     |                   | μA   |

| Pin Voltage = 0.8 V, 5.0 V $\leq$ V_{BATT} $\leq$ 26.5 V                           |                     | 10                      | _   | 50                |      |

| Receiver Output Low (RXD)                                                          | V <sub>OL</sub>     |                         |     |                   | V    |

| $I_{IN}$ = 2.0 mA, 5.0 V $\leq$ V_{BATT} $\leq$ 26.5 V                             | 01                  | _                       | -   | 0.45              |      |

| CNTL                                                                               |                     |                         |     | - 1               |      |

| CNTL Output Low                                                                    | V <sub>OLCNTL</sub> |                         |     |                   | V    |

| $I_{IN}$ = 5.0 $\mu A,~5.0~V \leq V_{BATT} \leq 26.5~V$                            |                     | -                       | -   | 0.8               |      |

| CNTL Output High                                                                   | V <sub>OHCNTL</sub> |                         |     |                   | V    |

| $I_{OUT}$ = 180 $\mu\text{A},5.0~\text{V} \leq~\text{V}_{BATT} \leq 26.5~\text{V}$ |                     | V <sub>BATT</sub> - 0.8 | -   | V <sub>BATT</sub> |      |

Notes

4. After t<sub>CNTLFDLY</sub>

5. Thermal shutdown causes the BUS output driver to be disabled. Guaranteed by characterization.

## Table 4. Static Electrical Characteristics (continued)

Characteristics noted under conditions of -40 °C  $\leq$  T<sub>A</sub>  $\leq$  125 °C, unless otherwise stated. Voltages are relative to GND, unless otherwise noted. All positive currents are into the pin. All negative currents are out of the pin.

| Characteristic                                                                             | Symbol                 | Min                                         | Тур | Max                                   | Unit |

|--------------------------------------------------------------------------------------------|------------------------|---------------------------------------------|-----|---------------------------------------|------|

| LOAD                                                                                       |                        | •                                           | 1   |                                       |      |

| LOAD Voltage Rise <sup>(6)</sup>                                                           | V <sub>LDRISE</sub>    |                                             |     |                                       | V    |

| Normal Speed and Voltage Mode, Transmit High-<br>Voltage Mode, Transmit High Speed Mode    | _                      |                                             |     |                                       |      |

| $I_{IN}$ = 1.0 mA, 5.0 V $\leq$ V_{BATT} $\leq$ 26.5 V                                     |                        | -                                           | -   | 0.1                                   |      |

| Sleep Mode                                                                                 |                        |                                             |     |                                       |      |

| I <sub>IN</sub> = 7.0 mA 33897T                                                            |                        | -                                           | -   | 1.0                                   |      |

| I <sub>IN</sub> = 7.0 mA <sup>(7)</sup> 33897CT                                            |                        | -                                           | _   | 0.1                                   |      |

| Loss of Battery                                                                            |                        |                                             |     |                                       |      |

| I <sub>IN</sub> = 7.0 mA                                                                   |                        | -                                           | -   | 1.0                                   |      |

| LOAD Leakage During Loss of Module Ground <sup>(8)</sup>                                   | I <sub>LDLEAK</sub>    |                                             |     |                                       | μA   |

| $0.0 \text{ V} \leq \text{V}_{\text{BATT}} \leq 18 \text{ V} \qquad \qquad 33897 \text{T}$ | EDEE/IR                | 0.0                                         | -   | -90                                   |      |

| $0.0~V \leq V_{BATT} \leq 18~V \qquad \qquad 33897 CT$                                     |                        | -10                                         | -   | 10                                    |      |

| BUS                                                                                        |                        | I                                           |     | _                                     | 1    |

| Passive Out BUS Leakage                                                                    |                        |                                             |     |                                       | μA   |

| Passive In                                                                                 | ILEAK                  |                                             |     |                                       |      |

| 0.0 V $\leq$ V_{BATT} $\leq$ 26.5 V, -1.5 V $\leq$ V_{BUS} < 0 V                           |                        | -5.0                                        | _   | 5.0                                   |      |

| Active In                                                                                  | I <sub>LKAI</sub>      |                                             |     |                                       |      |

| 0.0 V $\leq$ V_BATT $\leq$ 26.5 V, 0 V < V_BUS $\leq$ 12.5 V                               |                        | -5.0                                        | -   | 5.0                                   |      |

| BUS Leakage During Loss of Module Ground <sup>(9)</sup>                                    |                        |                                             |     |                                       |      |

| $0.0 \text{ V} \leq \text{V}_{\text{BATT}} \leq 18 \text{ V} \qquad \qquad 33897 \text{T}$ | IBLKLOG                | -10                                         | -   | 10                                    |      |

| $0.0 \ V \leq V_{BATT} \leq 18 \ V \qquad \qquad 33897 CT$                                 |                        | 0.0                                         | -   | -90                                   |      |

| High Voltage Wake-up Mode Output High Voltage                                              |                        |                                             |     |                                       | V    |

| 12 V $\leq$ V_{BATT} $\leq$ 26.5 V, 200 $\Omega$ $\leq$ R_L $\leq$ 3332 $\Omega$           |                        |                                             |     |                                       |      |

| 33897                                                                                      | T V <sub>HVWUOHF</sub> | 9.7                                         | -   | 12.5                                  |      |

| 33897C                                                                                     | T V <sub>HVWUOHO</sub> | 9.9                                         | _   | 12.5                                  |      |

| 5.0 V $\leq$ V $_{BATT}$ $<$ 12 V, 200 $\Omega$ $\leq$ $R_{L}$ $\leq$ 3332 $\Omega$        |                        | Lesser of V <sub>BAT</sub> -<br>1.5 or 9.7  | -   | V <sub>BATT</sub>                     |      |

| High Speed Mode Output High Voltage                                                        | V <sub>OHHS</sub>      |                                             |     |                                       | V    |

| 8.0 V $\leq$ V $_{BATT}$ $\leq$ 16 V, 75 $\Omega$ $\leq$ $R_{L}$ $\leq$ 135 $\Omega$       |                        | 4.2                                         | -   | 5.1                                   |      |

| Normal Mode Output High Voltage                                                            |                        |                                             |     |                                       | V    |

| 6.0 V $\leq$ V $_{BATT}$ $\leq$ 26.5 V, 200 $\Omega$ $\leq$ $R_{L}$ $\leq$ 3332 $\Omega$   | V <sub>NOHF</sub>      | 4.4                                         | -   | 5.1                                   |      |

| 5.0 V $\leq$ V_BATT $<$ 6.0 V, 200 $\Omega$ $\leq$ $R_L$ $\leq$ 3332 $\Omega$              | V <sub>NOHO</sub>      | Lesser of V <sub>BATT</sub> -<br>1.6 or 4.4 | -   | Lesser of V <sub>BATT</sub><br>or 5.1 |      |

Notes

6. GMW3089V2.4 specifies the maximum load voltage rise to be 0.1 V whenever module battery is intact, including when in Sleep mode. The maximum load voltage rise of 1.0 V in Sleep mode is a GM-approved exception to GMW3089V2.4.

7. 33897CT removes the diode drop during Sleep mode.

8. LOAD pin is at system ground voltage.

9. BUS pin is at system ground voltage

## Table 4. Static Electrical Characteristics (continued)

Characteristics noted under conditions of -40 °C  $\leq$  T<sub>A</sub>  $\leq$  125 °C, unless otherwise stated. Voltages are relative to GND, unless otherwise noted. All positive currents are into the pin. All negative currents are out of the pin.

| Characteristic                                                                                   | Symbol            | Min                                           | Тур | Max                                            | Unit |

|--------------------------------------------------------------------------------------------------|-------------------|-----------------------------------------------|-----|------------------------------------------------|------|

| BUS (CONTINUED)                                                                                  |                   |                                               |     |                                                |      |

| BUS Low Voltage 5.0 V $\leq$ V_{BATT} $\leq$ 26.5 V, 200 $\Omega$ $\leq$ RL $\leq$ 3332 $\Omega$ | V <sub>OL</sub>   | -0.2                                          | _   | 0.2                                            | V    |

| Short-circuit BUS Output Current<br>Dominant State, 5.0 V $\leq$ V <sub>BATT</sub> $\leq$ 26.5 V | I <sub>BSC</sub>  | -350                                          | _   | -100                                           | mA   |

| Input Threshold                                                                                  |                   |                                               |     |                                                | V    |

| Awake 5.0 V $\leq$ V <sub>BATT</sub> $\leq$ 26.5 V                                               | V <sub>BIA</sub>  | 2.0                                           | _   | 2.2                                            |      |

| Sleep 12 V $\leq$ V <sub>BATT</sub> $\leq$ 26.5 V                                                | V <sub>BISF</sub> | 6.6                                           | -   | 7.9                                            |      |

| Sleep $5.0 \text{ V} \leq \text{V}_{BATT} < 12 \text{ V}$                                        | V <sub>BISO</sub> | Lesser of 6.6 V or<br>V <sub>BATT</sub> - 4.3 | _   | Lesser of 7.9 V or<br>V <sub>BATT</sub> - 3.25 |      |

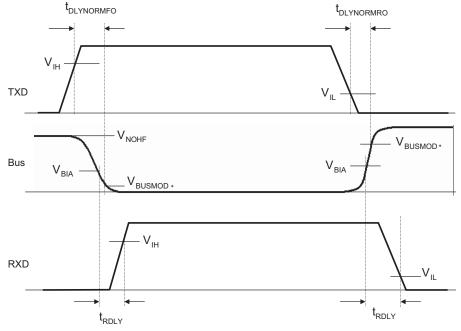

## **DYNAMIC ELECTRICAL CHARACTERISTICS**

## **Table 5. Dynamic Electrical Characteristics**

Characteristics noted under conditions of -40 °C  $\leq$  T<sub>A</sub>  $\leq$  125 °C, unless otherwise stated. Voltages are relative to GND unless otherwise noted. All positive currents are into the pin. All negative currents are out of the pin.

| Characteristic                                                                                                             | Symbol                 | Min  | Тур | Max | Unit |

|----------------------------------------------------------------------------------------------------------------------------|------------------------|------|-----|-----|------|

| BUS                                                                                                                        |                        |      | I   | I   |      |

| Normal Speed Rising Output Delay                                                                                           | t <sub>DLYNORMRO</sub> |      |     |     | μs   |

| 200 $\Omega \leq R_L \leq 3332~\Omega,~1.0~\mu s \leq Load$ Time Constants $\leq 4.0~\mu s$                                |                        | 2.0  | -   | 6.3 |      |

| Measured from TXD = $V_{IL}$ to $V_{BUS}$ as follows:                                                                      |                        |      |     |     |      |

| Max Time to V_{BUSMOD} = 3.7 V, 6.0 V $\leq$ V_{BATT} $\leq$ 26.5 V $^{(10)}$                                              |                        |      |     |     |      |

| Min Time to V_{BUSMOD} = 1.0 V, 6.0 V $\leq$ V_{BATT} $\leq$ 26.5 V $^{(10)}$                                              |                        |      |     |     |      |

| Max Time to $V_{BUSMOD}$ = 2.7 V, $V_{BATT}$ = 5.0 V <sup>(10)</sup>                                                       |                        |      |     |     |      |

| Min Time to V <sub>BUSMOD</sub> = 1.0 V, V <sub>BATT</sub> = 5.0 V $^{(10)}$                                               |                        |      |     |     |      |

| Normal Speed Falling Output Delay                                                                                          | t <sub>DLYNORMFO</sub> |      |     |     | μS   |

| 200 $\Omega \leq R_L \leq 3332~\Omega,~1.0~\mu s \leq Load$ Time Constants $\leq 4.0~\mu s$                                |                        | 1.8  | -   | 8.5 |      |

| Measured from TXD = $V_{IH}$ to $V_{BUS}$ as follows:                                                                      |                        |      |     |     |      |

| Max Time to V_{BUSMOD} = 1.0 V, 6.0 V $\leq$ V_{BATT} $\leq$ 26.5 V $^{(10)}$                                              |                        |      |     |     |      |

| Min Time to V_{BUSMOD} = 3.7 V, 6.0 V $\leq$ V_{BATT} $\leq$ 26.5 V $^{(10)}$                                              |                        |      |     |     |      |

| Max Time to $V_{BUSMOD}$ = 1.0 V, $V_{BATT}$ = 5.0 V <sup>(10)</sup>                                                       |                        |      |     |     |      |

| Min Time to V <sub>BUSMOD</sub> = 2.7 V, V <sub>BATT</sub> = 5.0 V $^{(10)}$                                               |                        |      |     |     |      |

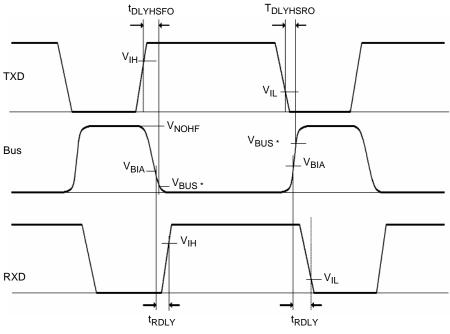

| High Speed Rising Output Delay                                                                                             | t <sub>DLYHSRO</sub>   |      |     |     | μS   |

| 75 $\Omega \le R_L \le 135 \Omega$ , 0.0 $\mu s \le Load$ Time Constants $\le 1.5 \mu s$ ,                                 |                        | 0.1  | -   | 1.7 |      |

| 8.0 V $\leq$ V <sub>BATT</sub> $\leq$ 16 V<br>Measured from TXD = V <sub>IL</sub> to V <sub>BUS</sub> as follows:          |                        |      |     |     |      |

|                                                                                                                            |                        |      |     |     |      |

| Max Time to $V_{BUS} = 3.7 V (11)$                                                                                         |                        |      |     |     |      |

| Min Time to $V_{BUS} = 1.0 V (11)$                                                                                         |                        |      |     |     |      |

| High Speed Falling Output Delay                                                                                            | t <sub>DLYHSFO</sub>   |      |     |     | μs   |

| 75 $\Omega \le R_L \le 135 \ \Omega$ , 0.0 µs $\le$ Load Time Constants $\le 1.5 \ \mu$ s, 8.0 V $\le V_{BATT} \le 16 \ V$ |                        | 0.04 | -   | 3.0 |      |

| Measured from TXD = $V_{IH}$ to $V_{BUS}$ as follows:                                                                      |                        |      |     |     |      |

| Max Time to $V_{BUS}$ = 1.0 V <sup>(11)</sup>                                                                              |                        |      |     |     |      |

| Min Time to $V_{BUS} = 3.7 V (11)$                                                                                         |                        |      |     |     |      |

Notes

10.  $V_{BUSMOD}$  is the voltage at the BUSMOD node in <u>Figure 6</u>, page <u>13</u>.

11.  $V_{BUS}$  is the voltage at the BUS pin in <u>Figure 7</u>, page <u>14</u>.

## Table 5. Dynamic Electrical Characteristics (continued)

Characteristics noted under conditions of -40 °C  $\leq$  T<sub>A</sub>  $\leq$  125 °C, unless otherwise stated. Voltages are relative to GND unless otherwise noted. All positive currents are into the pin. All negative currents are out of the pin.

| Characteristic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Symbol               | Min               | Тур         | Max              | Unit |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-------------------|-------------|------------------|------|

| BUS (CONTINUED)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                      |                   | I           |                  |      |

| $ \begin{array}{l} \mbox{High Voltage Rising Output Delay} \\ 200 \ \Omega \leq R_L \leq 3332 \ \Omega, \ 1.0 \ \mu s \leq \ Load \ Time \ Constants \leq 4.0 \ \mu s \\ \mbox{Measured from TXD=V_{IL} to V_{BUS} \ as follows:} \\ \mbox{Max Time to V}_{BUSMOD} = 3.7 \ V, \ 6.0 \ V \leq V_{BATT} \leq 26.5 \ V \ ^{(12)} \\ \mbox{Min Time to V}_{BUSMOD} = 1.0 \ V, \ 6.0 \ V \leq V_{BATT} \leq 26.5 \ V \ ^{(12)} \\ \mbox{Max Time to V}_{BUSMOD} = 9.4 \ V, \ 12.0 \ V \leq V_{BATT} \leq 26.5 \ V \ ^{(12)} \\ \end{array} $ | tdlyhvro             | 2.0<br>2.0<br>2.0 | -<br>-<br>- | 6.3<br>6.3<br>18 | μs   |

| $ \begin{array}{l} \mbox{High Voltage Falling Output Delay} \\ 200 \ \Omega \leq R_L \leq 3332 \ \Omega, \ 1.0 \ \mu s \leq \mbox{Load Time Constants} \leq 4.0 \ \mu s, \\ 12.0 \ V \leq V_{BATT} \leq 26.5 \ V \\ \mbox{Measured from TXD=V}_{IH} \ to \ V_{BUS} \ as \ follows: \\ \mbox{Max Time to } V_{BUSMOD} = 1.0 \ V \ ^{(12)} \\ \mbox{Min Time to } V_{BUSMOD} = 3.7 \ V \ ^{(12)} \end{array} $                                                                                                                            | t <sub>DLYHVFO</sub> | 1.8<br>1.8        | -           | 14<br>14         | μs   |

**RECEIVER RXD**

| Receive Delay Time (5.0 V $\leq$ V_BATT $\leq$ 26.5 V)                              | t <sub>RDLY</sub>     |     |   |      | μS |

|-------------------------------------------------------------------------------------|-----------------------|-----|---|------|----|

| Awake                                                                               |                       | 0.2 | - | 1.0  |    |

| Receive Delay Time (BUS Rising to RXD Falling, 5.0 V $\leq$ V_{BATT} $\leq$ 26.5 V) | t <sub>RDLYSL</sub>   |     |   |      | μS |

| Sleep                                                                               |                       | 10  | - | 70   |    |

| CNTL                                                                                |                       |     |   |      |    |

| CNTL Falling Delay Time (5.0 V $\leq$ V <sub>BATT</sub> $\leq$ 26.5 V)              | t <sub>CNTLFDLY</sub> | 300 | - | 1000 | ms |

Notes

12.  $V_{BUSMOD}$  is the voltage at the BUSMOD node in <u>Figure 6</u>, page <u>13</u>.

## TIMING DIAGRAMS

\* V<sub>BUSMOD</sub> is the voltage at the BUSMOD node in Figure 7.

\*  $V_{BUS}$  is the voltage at the BUS pin in Figure 8.

## Figure 5. TXD, Bus and RXD Waveforms in High Speed Mode

# FUNCTIONAL DESCRIPTION

## **INTRODUCTION**

The 33897 Series is intended for use as a physical layer device in a Single Wire CAN communications bus.

Communications takes place from a single pin over a single wire using a common ground for a current return path. Two data rates are available, with the high rate used for factory or assembly line communications and the lower for actual

The 33897 Series is intended to be used with an MCU to control its operation and to process and generate the data for the bus.

#### **GROUND PINS**

The four ground pins are not only for electrical conduction, their number and locations at each of the four corners serve also to remove heat from the IC. The biggest benefit of this is obtained by putting a lot of copper on the PCB in this area and, if ground is an internal layer, by adding numerous plated-through connections to it with the largest diameter holes the layout can use.

## **TXD DATA**

The data driven onto the SWCAN bus is inverted from the TXD pin. A "1" driven on TXD will result in an undriven (recessive) state (bus at near zero volts). When the TXD pin is low, the output goes to a driven state. The voltage and waveshaping in the driven state is determined by the levels on the MODE0 and MODE1 Pins (refer to Table 6).

| Logic | : Level | Operation                 |

|-------|---------|---------------------------|

| MODE0 | MODE1   | Operation                 |

| 0     | 0       | Sleep mode                |

| 0     | 1       | High voltage wake-up mode |

| 1     | 0       | High speed mode           |

| 1     | 1       | Normal mode               |

## MODE CONTROL

The MODE pins control the transmitter filtering and BUS voltage and the IC Sleep mode operation. <u>Table 6</u> shows the mode versus the logic levels on MODE0 and MODE1.

The MODE0 and MODE1 pins have a weak pull-down in the IC so that in case the pins are not driven, the device will enter the Sleep mode. This is usually the situation as the

system communications where the radiated EMI of the higher rate could be an issue.

Two pins control the mode of operation (sleep, low speed, high speed, and high voltage wake-up).

## FUNCTIONAL PIN DESCRIPTION

MCU comes out of reset, before the driving signals have been configured as outputs.

## **RXD DATA**

The data received on the bus is translated to logic levels on this pin. This pin is a logic high when the bus is in the recessive state (near zero volts) and is logic low when the bus is in either the normal or high voltage dominant state.

This is an open-drain type of output that requires an external resistor to pull it up. When the device is in sleep mode, the output will be off unless a high voltage wake-up level is detected on the bus. If the wake-up level is detected, the output will be driven by the data on the bus. If the level of the data returns to normal level, the output will return to off after a short delay unless a non-sleep mode condition is set by the MCU.

#### LOAD SWITCH

This switch is ON in all operating modes unless a loss of ground is detected. If this happens, the switch is opened and the resistor normally attached to its pin will no longer pass current to or from the bus.

## CNTL OUTPUT

This logic level signal is used to control a V<sub>CC</sub> regulator. When the output is low, the V<sub>CC</sub> regulator is expected to shutdown. This is normally used to shut down the MCU and all the devices powered by V<sub>CC</sub> when the IC is in Sleep mode. This is done to save power. When the part is taken out of the Sleep mode by the higher than normal bus voltage, this pin is asserted high and the V<sub>CC</sub> regulator brings its output up to the regulated level. This starts the MCU, which controls the mode of the IC. The MCU must change the mode signals to non-Sleep mode levels in order to keep this pin from going low. There is a delay to allow the MCU to fully wake-up and take control after the high voltage signaling is removed before the level on this output returns low. After a delay time, even if the bus is at high voltage, the IC will return to Sleep mode if both MODE pins are low.

## **VBATT INPUT**

This power input is not reverse battery protected and should use an external diode to protect it from damage due to reverse battery if this protection is desired. The voltage drop of the diode must be taken into consideration when the operating range of the system is being determined. This diode is generally used to protect the entire module from reverse battery and should be selected accordingly.

## BUS I/O

This input/output may require electrostatic discharge (ESD) and/or EMI external circuitry. A set of components is shown in the simplified application diagrams on page 15. The value of the capacitor should be adjusted downward in direct proportion to the added capacitance of the ESD or EMI circuits. The series resistance of the inductor should be kept below  $3.5 \Omega$  to prevent its voltage drop from significantly degrading system noise margins.

## FUNCTIONAL BLOCK DIAGRAM COMPONENTS

## TIMER OSC

This circuit generates a 500 kHz signal to be used for internal logic. It is the reference for some of the required delays.

## TIMERS

This circuit contains the timing logic used to hold the CNTL active for the required time after the conditions for sleep mode have been met. It is also used to keep the TXD driver active for a period of time after it has generated a passive level on the bus.

## MODE CONTROL

This circuit contains the control logic for the various operating modes and conditions required for the IC.

#### **BUS RCVR**

This circuit translates the levels on the BUS pin to a CMOS level indicating the presence of a logic [0] or a logic [1]. It also determines the presence of a high voltage wake-up (HVWU) signal that is passed to Mode Control and Timers circuits. An analog filter is used to "de-glitch" the high voltage wake-up signal and prevent false exits from the Sleep mode.

## **TXD BUS DRVR**

This circuit drives the BUS. It can drive it with the higher voltage wake-up signals when enabled by the Mode Control circuit. It can also provide waveshaping for reduced EMI or not provide it for the higher data rate mode. The actual data is received on TXD at CMOS logic levels, then translated by this circuit to the necessary operating voltages.

#### UNDER-VOLTAGE DETECT

This circuit monitors internal operating voltage to assure proper operation of the part. If a low-voltage condition is detected, it sends a signal to disable the BUS RCVR and TXD BUS DRVR circuits. This prevents incorrect data from being put on the bus or sent to the MCU.

## LOAD SWITCH

The LOAD switch provides a path for an external resistor connected to the BUS to be connected to ground. When a loss of ground is detected, this switch is opened to prevent the current that would normally be flowing to the ground from the module from going back through the load resistor and raising the bus level. The circuit is opened when the voltage between GND and VBATT becomes too low as would be the case if module ground were lost.

## **BUS LOADING PARAMETERS**

Note: The letter 'n' represents the number of nodes in the system.

Note: The letter 'n' represents the number of nodes in the system.

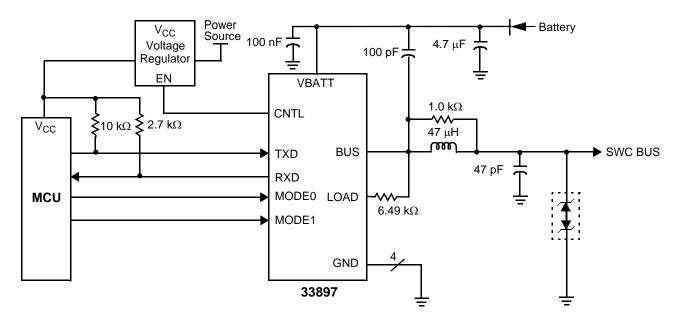

Figure 7. Transmitter Delays in Transmit High Speed Mode

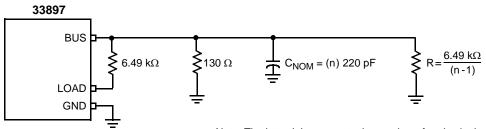

The 33897 can be used in applications where the module includes a regulator that has the capability of going into Sleep mode by having an Enable pin. See Figure 8. When the module's regulator is in Sleep mode, the module is turned off. The module waits for a defined wake-up voltage level on the

bus. This wake-up voltage will activate the CNTL line, which enables the regulator and turns the module back ON. This feature allows the module to be more energy efficient since the current consumption is significantly lowered when it goes into sleep mode.

Figure 8. 33897 Typical Application Schematic

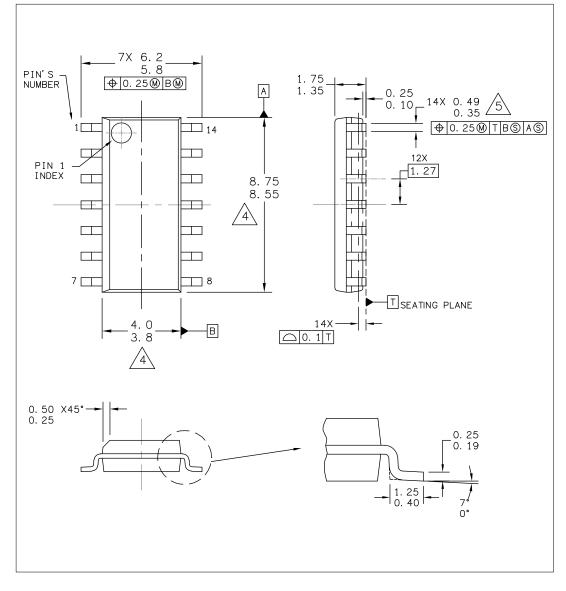

# PACKAGING

## PACKAGE DIMENSIONS

**Important**: For the most current Package revision, visit <u>www.freescale.com</u> and perform a Keyword Search on the 98ASB42565B drawing number below. Dimensions shown are provided for reference ONLY.

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED. | MECHANICA | LOUTLINE             | PRINT VERSION NO | DT TO SCALE |

|---------------------------------------------------------|-----------|----------------------|------------------|-------------|

| TITLE:<br>14LD SOIC N/B, 1.27 PITCH<br>CASE-OUTLINE     |           | DOCUMENT NO          | ): 98ASB42565B   | REV: J      |

|                                                         |           | CASE NUMBER: 751A-04 |                  | 04 DEC 2007 |

|                                                         |           | STANDARD: JE         | CDEC MS-012AB    |             |

EF (Pb-FREE) SUFFIX 14-pin SOICN 98ASB42565B ISSUE J

| NO      | TES:                                                                                                                                                                                                                                                  |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.      | DIMENSIONS ARE IN MILLIMETERS.                                                                                                                                                                                                                        |

| 2.      | DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994.                                                                                                                                                                                                    |

| 3.      | DATUMS A AND B TO BE DETERMINED AT THE PLANE WHERE THE BOTTOM OF THE LEADS EXIT THE PLASTIC BODY. DATUM T IS A SURFACE.                                                                                                                               |

| 4       | THIS DIMENSION DOES NOT INCLUDE MOLD FLASH, PROTRUSION OR GATE BURRS. MOLD<br>FLASH, PROTRUSION OR GATE BURRS SHALL NOT EXCEED 0.15 MM PER SIDE. THIS<br>DIMENSION IS DETERMINED AT THE PLANE WHERE THE BOTTOM OF THE LEADS EXIT<br>THE PLASTIC BODY. |

| <u></u> | THIS DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.127 TOTOAL IN EXCESS OF THE LEAD WIDTH AT MAXIMUM MATERIAL CONDITION.                                                                                       |

|         |                                                                                                                                                                                                                                                       |

|         |                                                                                                                                                                                                                                                       |

|         |                                                                                                                                                                                                                                                       |

|         |                                                                                                                                                                                                                                                       |

|         |                                                                                                                                                                                                                                                       |

|         |                                                                                                                                                                                                                                                       |

|         |                                                                                                                                                                                                                                                       |

|         |                                                                                                                                                                                                                                                       |

|         |                                                                                                                                                                                                                                                       |

|         |                                                                                                                                                                                                                                                       |

|         |                                                                                                                                                                                                                                                       |

|         |                                                                                                                                                                                                                                                       |

|         |                                                                                                                                                                                                                                                       |

|         |                                                                                                                                                                                                                                                       |

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED. | MECHANICA | LOUTLINE     | PRINT VERSION NO | OT TO SCALE |

|---------------------------------------------------------|-----------|--------------|------------------|-------------|

| TITLE:<br>14LD SOIC N/B, 1.27 PITCH<br>CASE-OUTLINE     |           | DOCUMENT NO  | ): 98ASB42565B   | REV: J      |

|                                                         |           | CASE NUMBER  | R: 751A-04       | 04 DEC 2007 |

|                                                         |           | STANDARD: JE | ECDEC MS-012AB   | •           |

EF (Pb-FREE) SUFFIX 14-pin SOICN 98ASB42565B ISSUE J

# **REVISION HISTORY**

| REVISION | DATE    | DESCRIPTION OF CHANGES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9.0      | 5/2005  | <ul> <li>Converted to Freescale format</li> <li>Added A &amp; B Versions</li> <li>Updated Device Variation Table, and Note "* Recommended device for all new designs"</li> <li>Added EF (Pb-Free) Devices, and higher soldering temperature</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 10.0     | 8/2005  | <ul> <li>Implemented Revision History page</li> <li>Updated Simplified Application Diagrams</li> <li>Updated Typical Application Schematic</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 11.0     | 12/2005 | Added 33897C and D versions and Timing Diagrams                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 12.0     | 1/2006  | <ul> <li>Updated Table 4, Static Electrical Characteristics - LOAD and BUS parameters</li> <li>Updated Ordering Information.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 13.0     | 6/2006  | Removed "Unless otherwise noted" from Static Electrical Characteristics & Dynamic Electrical<br>Characteristics table introductions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 14.0     | 8/2006  | <ul> <li>Added Part Numbers MC33897TD and MC33897TEF to Ordering Information on Page 1.</li> <li>Added 33897T to Table 1, Device Variations on Page 3, Referencing Electrical Changes per Errata MC33897TER, Revision 3 and specifying ESD variations</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 15.0     | 10/2006 | <ul> <li>Removed Part Numbers MC33897TD/R2, MC33897TEF/R2, MC33897CLEF/R2, PC33897CLEF/<br/>R2, MC33897DLEF/R2, and PC33897DLEF/R2</li> <li>Added Part Numbers MCZ33897EF/R2, MCZ33897TEF/R2, MCZ33897AEF/R2, MCZ33897EF/<br/>R2, MCZ33897BEF/R2, and MCZ33897DEF/R2 to the Ordering Information block on Page 1.</li> <li>Updated Device Variations on page 2 for "T" suffix products</li> <li>Split out Human Body Model on page 5 to differentiate between T and non-T versions</li> <li>Added Under-voltage Hysteresis on page 6</li> <li>Removed Peak Package Reflow Temperature During Reflow (solder reflow) parameter from<br/>Maximum Ratings on page 5. Added note with instructions to obtain this information from<br/>www.freescale.com.</li> </ul> |

| 16.0     | 6/2007  | Removed watermark, "Advance Information" from page 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 17.0     | 1/2011  | <ul> <li>Improved HBM ESD All Pins Except BUS to ±2.0 kV on MC33897CT</li> <li>Added MC33897CTEKF/R2 to the ordering information</li> <li>Removed all 8-Pin SOICN device information</li> <li>Changed Short-circuit BUS Output Current to -100 mA (Approved by GM)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 18.0     | 4/2012  | Updated Quiescent Current I <sub>QSLP</sub> to 60 μA max.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

#### How to Reach Us:

Home Page: freescale.com

Web Support: freescale.com/support Information in this document is provided solely to enable system and software implementers to use Freescale products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits on the information in this document.

Freescale reserves the right to make changes without further notice to any products herein. Freescale makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by customer's technical experts. Freescale does not convey any license under its patent rights nor the rights of others. Freescale sells products pursuant to standard terms and conditions of sale, which can be found at the following address: http://www.reg.net/v2/webservices/Freescale/Docs/TermsandConditions.htm

Freescale, the Freescale logo, AltiVec, C-5, CodeTest, CodeWarrior, ColdFire, C-Ware, Energy Efficient Solutions logo, mobileGT, PowerQUICC, QorlQ, Qorivva, StarCore, and Symphony are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. Airfast, BeeKit, BeeStack, ColdFire+, CoreNet, Flexis, MagniV, MXC, Platform in a Package, Processor expert, QorlQ Qonverge, QUICC Engine, Ready Play, SMARTMOS, TurboLink, Vybrid, and Xtrinsic are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners.

© 2012 Freescale Semiconductor, Inc.

Document Number: MC33897 Rev. 18.0 4/2012

# **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Freescale Semiconductor:

<u>MCZ33897TEF</u> <u>MCZ33897TEFR2</u> <u>MC33897EF</u> <u>MC33897BEFR2</u> <u>MC33897BEFR2</u> <u>MC33897EFR2</u> <u>MC33897EFR2</u> <u>MC33897AEFR2</u> <u>MC33897AEFR2</u>

NXP:

MC33897CTEF MC33897CTEFR2