# 1. General description

Dual Standard level N-channel MOSFET in an LFPAK56D (Dual Power-SO8) package using TrenchMOS technology. This product has been designed and qualified to AEC Q101 standard for use in high performance automotive applications.

#### 2. Features and benefits

- Dual MOSFET

- Q101 Compliant

- Repetitive avalanche rated

- Suitable for thermally demanding environments due to 175 °C rating

- True standard level gate with V<sub>GS(th)</sub> rating of greater than 1 V at 175 °C

# 3. Applications

- 12 V, 24 V and 48 V Automotive systems

- Motors, lamps and solenoid control

- · Transmission control

- Ultra high performance power switching

### 4. Quick reference data

Table 1. Quick reference data

| Symbol                                | Parameter                            | Conditions                                                                                                                                          |  | Min | Тур | Max | Unit |

|---------------------------------------|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--|-----|-----|-----|------|

| $V_{DS}$                              | drain-source voltage                 | T <sub>j</sub> ≥ 25 °C; T <sub>j</sub> ≤ 175 °C                                                                                                     |  | -   | -   | 100 | V    |

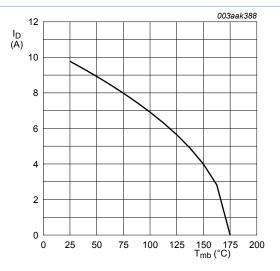

| I <sub>D</sub>                        | drain current                        | V <sub>GS</sub> = 10 V; T <sub>mb</sub> = 25 °C; <u>Fig. 2</u>                                                                                      |  | -   | -   | 9.8 | Α    |

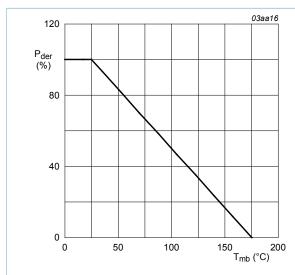

| P <sub>tot</sub>                      | total power dissipation              | T <sub>mb</sub> = 25 °C; <u>Fig. 1</u>                                                                                                              |  | -   | -   | 32  | W    |

| Static characte                       | Static characteristics FET1 and FET2 |                                                                                                                                                     |  |     |     |     |      |

| R <sub>DSon</sub>                     | drain-source on-state resistance     | $V_{GS} = 10 \text{ V}; I_D = 5 \text{ A}; T_j = 25 \text{ °C}; Fig. 11$                                                                            |  | -   | 97  | 121 | mΩ   |

| Dynamic characteristics FET1 and FET2 |                                      |                                                                                                                                                     |  |     |     |     |      |

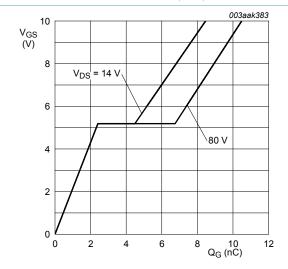

| $Q_{GD}$                              | gate-drain charge                    | $I_D = 5 \text{ A}; V_{DS} = 80 \text{ V}; V_{GS} = 10 \text{ V};$<br>$T_j = 25 \text{ °C}; \underline{\text{Fig. 13}}; \underline{\text{Fig. 14}}$ |  | -   | 4.3 | -   | nC   |

# 5. Pinning information

Table 2. Pinning information

| Pin | Symbol | Description | Simplified outline                      | Graphic symbol |

|-----|--------|-------------|-----------------------------------------|----------------|

| 1   | S1     | source1     | 8 7 6 5                                 | D1 D1 D2 D2    |

| 2   | G1     | gate1       | \\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\ |                |

| 3   | S2     | source2     |                                         |                |

| 4   | G2     | gate2       |                                         |                |

| 5   | D2     | drain2      |                                         |                |

| 6   | D2     | drain2      |                                         | mbk725         |

| 7   | D1     | drain1      | 1 2 3 4 <b>LFPAK56D (SOT1205)</b>       |                |

| 8   | D1     | drain1      | 2                                       |                |

# 6. Ordering information

Table 3. Ordering information

| Type number   | Package  |                                                                  |         |  |  |

|---------------|----------|------------------------------------------------------------------|---------|--|--|

|               | Name     | Description                                                      | Version |  |  |

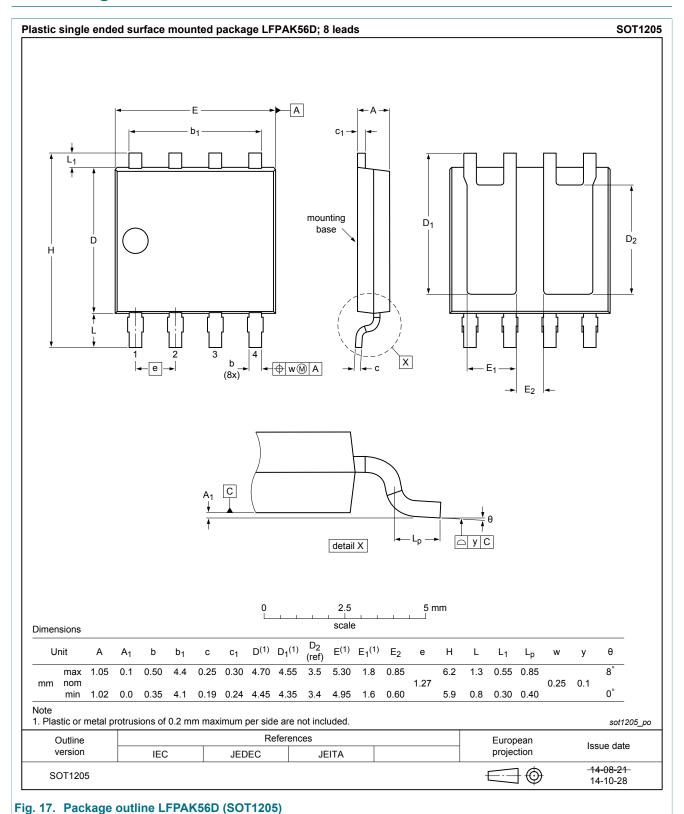

| BUK7K134-100E | LFPAK56D | Plastic single ended surface mounted package (LFPAK56D); 8 leads | SOT1205 |  |  |

# 7. Marking

Table 4. Marking codes

| Type number   | Marking code |

|---------------|--------------|

| BUK7K134-100E | 713410E      |

# 8. Limiting values

Table 5. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134).

| Symbol                                                                                                                                       | Parameter               | Conditions                                                      | Min | Max | Unit |

|----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-----------------------------------------------------------------|-----|-----|------|

| $V_{DS}$                                                                                                                                     | drain-source voltage    | T <sub>j</sub> ≥ 25 °C; T <sub>j</sub> ≤ 175 °C                 | -   | 100 | V    |

| $V_{DGR}$                                                                                                                                    | drain-gate voltage      | $R_{GS} = 20 \text{ k}\Omega$                                   | -   | 100 | V    |

| V <sub>GS</sub>                                                                                                                              | gate-source voltage     | T <sub>j</sub> ≤ 175 °C; DC                                     | -20 | 20  | V    |

| P <sub>tot</sub>                                                                                                                             | total power dissipation | T <sub>mb</sub> = 25 °C; <u>Fig. 1</u>                          | -   | 32  | W    |

| I <sub>D</sub>                                                                                                                               | drain current           | T <sub>mb</sub> = 25 °C; V <sub>GS</sub> = 10 V; <u>Fig. 2</u>  | -   | 9.8 | Α    |

|                                                                                                                                              |                         | T <sub>mb</sub> = 100 °C; V <sub>GS</sub> = 10 V; <u>Fig. 2</u> | -   | 6.9 | Α    |

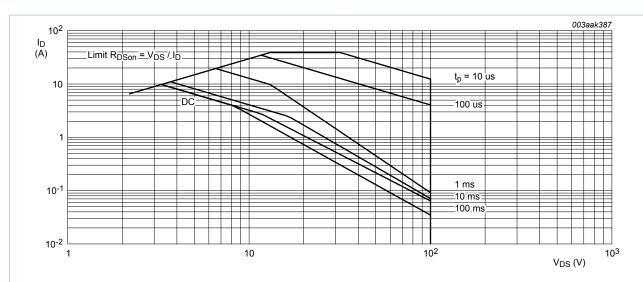

| I <sub>DM</sub>                                                                                                                              | peak drain current      | $T_{mb}$ = 25 °C; pulsed; $t_p \le 10 \mu s$ ; Fig. 3           | -   | 39  | Α    |

| BUK7K134-100E All information provided in this document is subject to legal disclaimers. © NXP Semiconductors N.V. 2015. All rights reserved |                         |                                                                 |     |     |      |

| Symbol                             | Parameter                                    | Conditions                                                                                                     |        | Min | Max  | Unit |

|------------------------------------|----------------------------------------------|----------------------------------------------------------------------------------------------------------------|--------|-----|------|------|

| T <sub>stg</sub>                   | storage temperature                          |                                                                                                                |        | -55 | 175  | °C   |

| T <sub>j</sub>                     | junction temperature                         |                                                                                                                |        | -55 | 175  | ##C  |

| T <sub>sld(M)</sub>                | peak soldering temperature                   |                                                                                                                |        | -   | 260  | °C   |

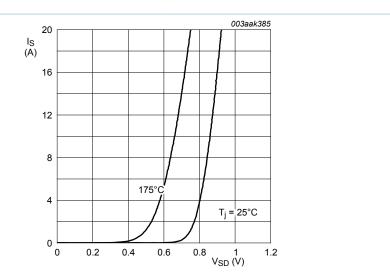

| Source-drain                       | diode FET1 and FET2                          |                                                                                                                |        |     |      |      |

| I <sub>S</sub>                     | source current                               | T <sub>mb</sub> = 25 °C                                                                                        |        | -   | 9.8  | Α    |

| I <sub>SM</sub>                    | peak source current                          | pulsed; $t_p \le 10 \ \mu s$ ; $T_{mb} = 25 \ ^{\circ}C$                                                       |        | -   | 39   | Α    |

| Avalanche Ruggedness FET1 and FET2 |                                              |                                                                                                                |        |     |      |      |

| E <sub>DS(AL)S</sub>               | non-repetitive drain-source avalanche energy | $I_D$ = 9.8 A; $V_{sup} \le 100$ V; $R_{GS}$ = 50 Ω; $V_{GS}$ = 10 V; $T_{j(init)}$ = 25 °C; unclamped; Fig. 4 | [1][2] | -   | 10.9 | mJ   |

- [1] Refer to application note AN10273 for further information

- [2] Single-pulse avalanche rating limited by maximum junction temperature of 175 °C

Fig. 1. Normalized total power dissipation as a function of mounting base temperature

$$P_{der} = \frac{P_{tot}}{P_{tot(25^{\circ}C)}} \times 100\%$$

Fig. 2. Continuous drain current as a function of mounting base temperature

$$V_{GS} \ge 10V$$

3 / 13

Fig. 3. Safe operating area; continuous and peak drain currents as a function of drain-source voltage

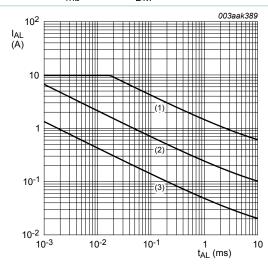

Fig. 4. Avalanche rating; avalanche current as a function of avalanche time

(1)

$$T_{j(init)} = 25$$

°C; (2)  $T_{j(init)} = 150$ °C; (3) Repetitive Avalanche

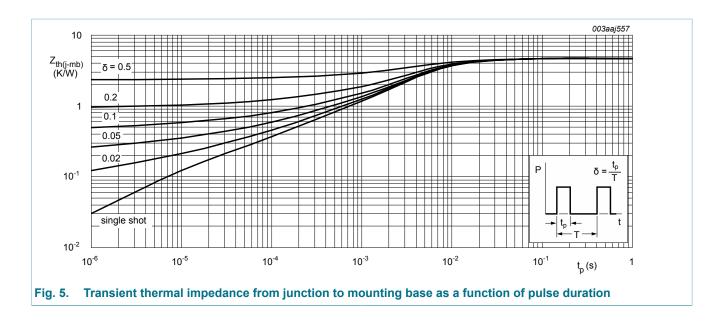

## 9. Thermal characteristics

Table 6. Thermal characteristics

| Symbol                | Parameter                                               | Conditions                                            | Min | Тур | Max  | Unit |

|-----------------------|---------------------------------------------------------|-------------------------------------------------------|-----|-----|------|------|

| R <sub>th(j-mb)</sub> | thermal resistance<br>from junction to<br>mounting base | Fig. 5                                                | -   | -   | 4.68 | K/W  |

| R <sub>th(j-a)</sub>  | thermal resistance<br>from junction to<br>ambient       | Minimum footprint; mounted on a printed circuit board | -   | 95  | -    | K/W  |

BUK7K134-100E

All information provided in this document is subject to legal disclaimers.

© NXP Semiconductors N.V. 2015. All rights reserved

## 10. Characteristics

Table 7. Characteristics

| Symbol                                              | Parameter                                           | Conditions                                                                                                                                          | Min | Тур  | Max | Unit |

|-----------------------------------------------------|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|------|

| Static chara                                        | acteristics FET1 and FET2                           |                                                                                                                                                     | '   |      |     |      |

| V <sub>(BR)DSS</sub> drain-source breakdown voltage | $I_D = 250 \mu A; V_{GS} = 0 V; T_j = -55 °C$       | 90                                                                                                                                                  | -   | -    | V   |      |

|                                                     | $I_D = 250 \mu A; V_{GS} = 0 V; T_j = 25 ^{\circ}C$ | 100                                                                                                                                                 | -   | -    | V   |      |

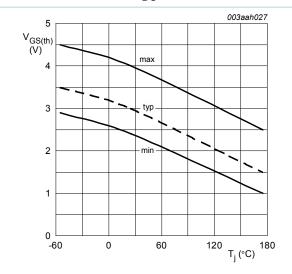

| V <sub>GS(th)</sub>                                 | gate-source threshold voltage                       | $I_D$ = 1 mA; $V_{DS}$ = $V_{GS}$ ; $T_j$ = 25 °C;<br>Fig. 9; Fig. 10                                                                               | 2.4 | 3    | 4   | V    |

|                                                     |                                                     | I <sub>D</sub> = 1 mA; V <sub>DS</sub> = V <sub>GS</sub> ; T <sub>j</sub> = 175 °C;<br>Fig. 10                                                      | 1   | -    | -   | V    |

|                                                     |                                                     | $I_D$ = 1 mA; $V_{DS}$ = $V_{GS}$ ; $T_j$ = -55 °C;<br>Fig. 10                                                                                      | -   | -    | 4.5 | V    |

| I <sub>DSS</sub> drain leakage current              | drain leakage current                               | V <sub>DS</sub> = 100 V; V <sub>GS</sub> = 0 V; T <sub>j</sub> = 25 °C                                                                              | -   | 0.02 | 1   | μA   |

|                                                     |                                                     | V <sub>DS</sub> = 100 V; V <sub>GS</sub> = 0 V; T <sub>j</sub> = 175 °C                                                                             | -   | -    | 500 | μA   |

| I <sub>GSS</sub> gate leakage current               | gate leakage current                                | V <sub>GS</sub> = -20 V; V <sub>DS</sub> = 0 V; T <sub>j</sub> = 25 °C                                                                              | -   | 2    | 100 | nA   |

|                                                     |                                                     | V <sub>GS</sub> = 20 V; V <sub>DS</sub> = 0 V; T <sub>j</sub> = 25 °C                                                                               | -   | 2    | 100 | nA   |

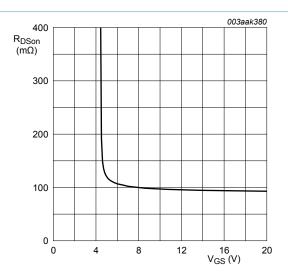

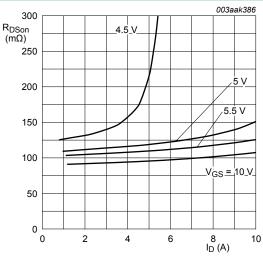

| R <sub>DSon</sub>                                   | drain-source on-state                               | $V_{GS} = 10 \text{ V}; I_D = 5 \text{ A}; T_j = 25 ^{\circ}\text{C}; Fig. 11$                                                                      | -   | 97   | 121 | mΩ   |

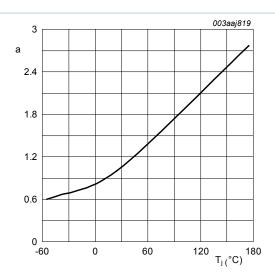

|                                                     | resistance                                          | V <sub>GS</sub> = 10 V; I <sub>D</sub> = 5 A; T <sub>j</sub> = 175 °C;<br>Fig. 12; Fig. 11                                                          | -   | 260  | 335 | mΩ   |

| Dynamic ch                                          | naracteristics FET1 and FE                          | T2                                                                                                                                                  | '   |      |     |      |

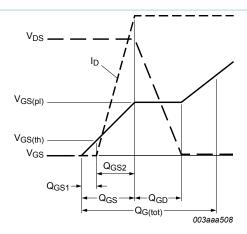

| Q <sub>G(tot)</sub>                                 | total gate charge                                   | $I_D = 5 \text{ A}; V_{DS} = 80 \text{ V}; V_{GS} = 10 \text{ V};$<br>$T_j = 25 \text{ °C}; \underline{\text{Fig. 13}}; \underline{\text{Fig. 14}}$ | -   | 10.5 | -   | nC   |

| Q <sub>GS</sub>                                     | gate-source charge                                  |                                                                                                                                                     | -   | 2.4  | -   | nC   |

| $Q_{GD}$                                            | gate-drain charge                                   |                                                                                                                                                     | -   | 4.3  | -   | nC   |

| Symbol              | Parameter                    | Conditions                                                                                                           |   | Min | Тур  | Max | Unit |

|---------------------|------------------------------|----------------------------------------------------------------------------------------------------------------------|---|-----|------|-----|------|

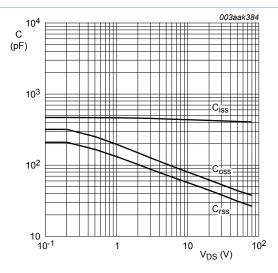

| C <sub>iss</sub>    | input capacitance            | V <sub>GS</sub> = 0 V; V <sub>DS</sub> = 25 V; f = 1 MHz;                                                            |   | -   | 423  | 564 | pF   |

| C <sub>oss</sub>    | output capacitance           | T <sub>j</sub> = 25 °C; <u>Fig. 15</u>                                                                               |   | -   | 57   | 69  | pF   |

| C <sub>rss</sub>    | reverse transfer capacitance |                                                                                                                      |   | -   | 41   | 56  | pF   |

| t <sub>d(on)</sub>  | turn-on delay time           | $V_{DS}$ = 80 V; R <sub>L</sub> = 15 Ω; V <sub>GS</sub> = 10 V;<br>R <sub>G(ext)</sub> = 5 Ω; T <sub>j</sub> = 25 °C |   | -   | 4.3  | -   | ns   |

| t <sub>r</sub>      | rise time                    |                                                                                                                      |   | -   | 5.5  | -   | ns   |

| t <sub>d(off)</sub> | turn-off delay time          |                                                                                                                      |   | -   | 8.6  | -   | ns   |

| t <sub>f</sub>      | fall time                    |                                                                                                                      |   | -   | 5.8  | -   | ns   |

| Source-dra          | in diode FET1 and FET2       | 1                                                                                                                    | 1 |     |      |     |      |

| V <sub>SD</sub>     | source-drain voltage         | $I_S = 5 \text{ A}; V_{GS} = 0 \text{ V}; T_j = 25 \text{ °C}; Fig. 16$                                              |   | -   | 0.82 | 1.2 | V    |

| t <sub>rr</sub>     | reverse recovery time        | $I_S = 5 \text{ A}$ ; $dI_S/dt = -100 \text{ A/}\mu\text{s}$ ; $V_{GS} = 0 \text{ V}$ ;                              |   | -   | 33.4 | -   | ns   |

| Q <sub>r</sub>      | recovered charge             | $V_{DS} = 50 \text{ V}; T_j = 25 \text{ °C}$                                                                         |   | -   | 45.1 | -   | nC   |

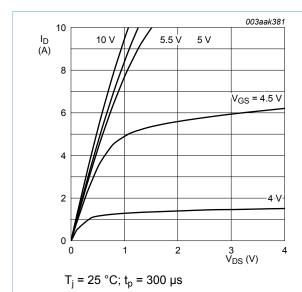

Fig. 6. Output characteristics; drain current as a function of drain-source voltage; typical values

Fig. 7. Drain-source on-state resistance as a function of gate-source voltage; typical values

$$T_j = 25^{\circ}C; I_D = 5A$$

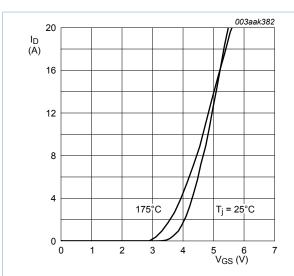

Fig. 8. Transfer characteristics; drain current as a function of gate-source voltage; typical values

$$V_{DS} = 12V$$

Fig. 10. Gate-source threshold voltage as a function of junction temperature

$$I_D$$

= 1 mA;  $V_{DS}$  =  $V_{GS}$

Fig. 9. Sub-threshold drain current as a function of gate-source voltage

$$T_i = 25$$

°C;  $V_{DS} = 5V$

$T_i = 25 \,^{\circ}\text{C}; t_p = 300 \,\mu\text{s}$

Fig. 11. Drain-source on-state resistance as a function of drain current; typical values

Fig. 12. Normalized drain-source on-state resistance factor as a function of junction temperature

$$a = \frac{R_{DSon}}{R_{DSon}(25^{\circ}C)}$$

Fig. 14. Gate-source voltage as a function of gate charge; typical values

$$T_j = 25^{\circ}C; I_D = 5A$$

Fig. 13. Gate charge waveform definitions

Fig. 15. Input, output and reverse transfer capacitances as a function of drain-source voltage; typical values

$$V_{GS} = 0V$$

;  $f = 1MHz$

NXP Semiconductors BUK7K134-100E

Fig. 16. Source (diode forward) current as a function of source-drain (diode forward) voltage; typical values

# 11. Package outline

# 12. Legal information

#### 12.1 Data sheet status

| Document status [1][2]               | Product status [3] | Definition                                                                            |

|--------------------------------------|--------------------|---------------------------------------------------------------------------------------|

| Objective<br>[short] data<br>sheet   | Development        | This document contains data from the objective specification for product development. |

| Preliminary<br>[short] data<br>sheet | Qualification      | This document contains data from the preliminary specification.                       |

| Product<br>[short] data<br>sheet     | Production         | This document contains the product specification.                                     |

- Please consult the most recently issued document before initiating or completing a design.

- [2] The term 'short data sheet' is explained in section "Definitions".

- The product status of device(s) described in this document may have changed since this document was published and may differ in case of multiple devices. The latest product status information is available on the Internet at URL <a href="http://www.nxp.com">http://www.nxp.com</a>.

#### 12.2 Definitions

**Preview** — The document is a preview version only. The document is still subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

Draft — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

Short data sheet — A short data sheet is an extract from a full data sheet with the same product type number(s) and title. A short data sheet is intended for quick reference only and should not be relied upon to contain detailed and full information. For detailed and full information see the relevant full data sheet, which is available on request via the local NXP Semiconductors sales office. In case of any inconsistency or conflict with the short data sheet, the full data sheet shall prevail.

Product specification — The information and data provided in a Product data sheet shall define the specification of the product as agreed between NXP Semiconductors and its customer, unless NXP Semiconductors and customer have explicitly agreed otherwise in writing. In no event however, shall an agreement be valid in which the NXP Semiconductors product is deemed to offer functions and qualities beyond those described in the Product data sheet.

#### 12.3 Disclaimers

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. NXP Semiconductors takes no responsibility for the content in this document if provided by an information source outside of NXP Semiconductors.

In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the *Terms and conditions of commercial sale* of NXP Semiconductors.

Right to make changes — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use in automotive applications — This NXP Semiconductors product has been qualified for use in automotive applications. Unless otherwise agreed in writing, the product is not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors and its suppliers accept no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk

**Quick reference data** — The Quick reference data is an extract of the product data given in the Limiting values and Characteristics sections of this document, and as such is not complete, exhaustive or legally binding.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect.

Limiting values — Stress above one or more limiting values (as defined in the Absolute Maximum Ratings System of IEC 60134) will cause permanent damage to the device. Limiting values are stress ratings only and (proper) operation of the device at these or any other conditions above those given in the Recommended operating conditions section (if present) or the Characteristics sections of this document is not warranted. Constant or repeated exposure to limiting values will permanently and irreversibly affect the quality and reliability of the device.

Terms and conditions of commercial sale — NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at <a href="http://www.nxp.com/profile/terms">http://www.nxp.com/profile/terms</a>, unless otherwise agreed in a valid written individual agreement. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. NXP Semiconductors hereby expressly objects to applying the customer's general terms and conditions with regard to the purchase of NXP Semiconductors products by customer.

BUK7K134-100E

All information provided in this document is subject to legal disclaimers.

© NXP Semiconductors N.V. 2015. All rights reserved

**No offer to sell or license** — Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

**Translations** — A non-English (translated) version of a document is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.

#### 12.4 Trademarks

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

Bitsound, CoolFlux, CoReUse, DESFire, FabKey, GreenChip, HiPerSmart, HITAG, I²C-bus logo, ICODE, I-CODE, ITEC, MIFARE, MIFARE Plus, MIFARE Ultralight, SmartXA, STARPlug, TOPFET, TrenchMOS, TriMedia and UCODE — are trademarks of NXP Semiconductors N.V.

$\ensuremath{\mathbf{HD}}$   $\ensuremath{\mathbf{Radio}}$  and  $\ensuremath{\mathbf{HD}}$   $\ensuremath{\mathbf{Radio}}$  logo — are trademarks of iBiquity Digital Corporation.

## 13. Contents

| 1    | General description     | 1  |

|------|-------------------------|----|

| 2    | Features and benefits   | 1  |

| 3    | Applications            | 1  |

| 4    | Quick reference data    | 1  |

| 5    | Pinning information     | 2  |

| 6    | Ordering information    |    |

| 7    | Marking                 | 2  |

| 8    | Limiting values         |    |

| 9    | Thermal characteristics | 4  |

| 10   | Characteristics         | 5  |

| 11   | Package outline         | 10 |

| 12   | Legal information       | 11 |

| 12.1 | Data sheet status       | 11 |

| 12.2 | Definitions             | 11 |

| 12.3 | Disclaimers             | 11 |

| 12.4 | Trademarks              | 12 |

#### © NXP Semiconductors N.V. 2015. All rights reserved

For more information, please visit: http://www.nxp.com For sales office addresses, please send an email to: salesaddresses@nxp.com Date of release: 2 September 2015

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

NXP:

BUK7K134-100EX