# NT3H2111/NT3H2211

NTAG I<sup>2</sup>C *plus*, NFC Forum Type 2 Tag compliant IC with I<sup>2</sup>C interface

Rev. 3.0 — 3 February 2016 359930

Product data sheet COMPANY PUBLIC

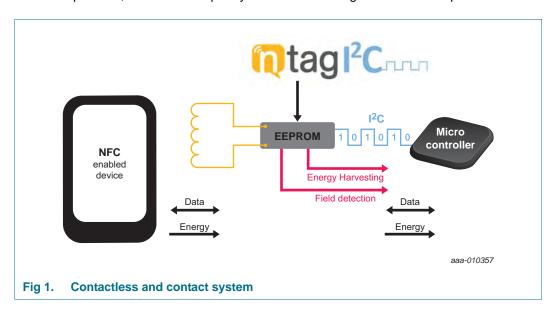

# 1. General description

Designed to be the perfect enabler for NFC in home-automation and consumer applications, this feature-packed, second-generation connected NFC tag is the fastest, least expensive way to add tap-and-go connectivity to just about any electronic device.

NXP NTAG I<sup>2</sup>C *plus* is a family of connected NFC tags that combine a passive NFC interface with a contact I<sup>2</sup>C interface. As the second generation of NXP's industry leading connected-tag technology, these devices maintain full backward compatibility with first-generation NTAG I<sup>2</sup>C products, while adding new, advanced features for password protection, full memory-access configuration from both interfaces, and an originality signature for protection against cloning.

The second-generation technology provides four times higher pass-through performance, along with energy harvesting capabilities, yet NTAG I<sup>2</sup>C *plus* devices are optimized for use in entry-level NFC applications and offer the lowest BoM of any NFC solution.

I<sup>2</sup>C and NFC communications are based on simple, standard command sets, and are augmented by the demo board OM5569/NT322E, which includes online reference source code. All that is required is a simple antenna design (see <u>Ref. 5</u>), with no or only limited extra components, and there are plenty of reference designs online for inspiration.

## 2. Features and benefits

### 2.1 Key features

- Interoperability

- ◆ ISO/IEC 14443 Part 2 and 3 compliant

- ◆ NFC Forum Type 2 Tag compliant

- Unique 7-byte UID

- GET\_VERSION command for easy identification of chip type and supported features

- Input capacitance of 50 pF

- Host interface

- ◆ I<sup>2</sup>C slave

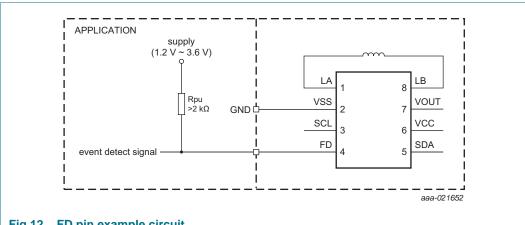

- Configurable event detection pin to signal NFC or pass-through data events

- Memory

- ◆ 888/1912 bytes of EEPROM-based user memory

- ◆ 64 bytes SRAM buffer for transfer of data between NFC and I<sup>2</sup>C interfaces with memory mirror or pass-through mode

- Clear arbitration between NFC and I<sup>2</sup>C memory access

- Data transfer

- Pass-through mode with 64-byte SRAM buffer

- FAST\_WRITE and FAST\_READ NFC commands for higher data throughput

- Security and memory-access management

- Full, read-only, or no memory access from NFC interface, based on 32-bit password

- ◆ Full, read-only, or no memory access from I<sup>2</sup>C interface

- NFC silence feature to disable the NFC interface

- Originality signature based on Elliptic Curve Cryptography (ECC) for simple, genuine authentication

- Power Management

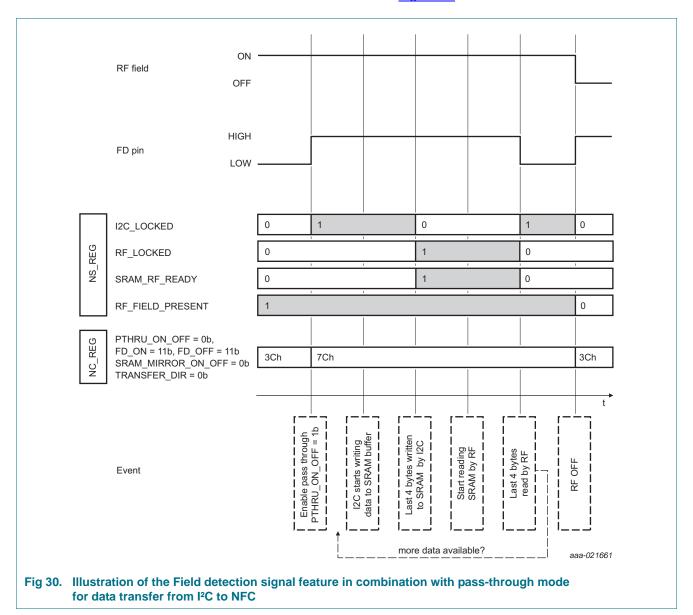

- Configurable field-detection output signal for data-transfer synchronization and device wake-up

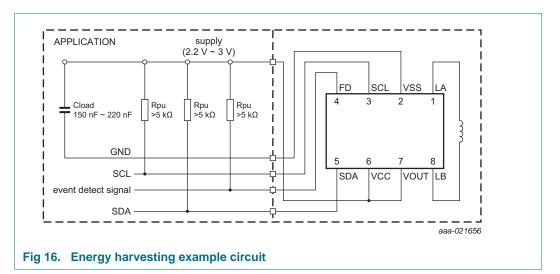

- Energy harvesting from NFC field, so as to power external devices (e.g. connected microcontroller)

- Industrial requirements

- ◆ Temperature range from -40 °C up to 105 °C

### 2.2 NFC interface

- Contactless transmission of data

- NFC Forum Type 2 Tag compliant (see Ref. 1)

- ISO/IEC 14443A compliant (see Ref. 2)

- 4 bytes (one page) written including all overhead in 4.8 ms via EEPROM or 0.8 ms via SRAM

- 64 bytes (whole SRAM) written including all overhead in 6.1 ms using FAST\_WRITE command

NT3H2111/NT3H2211

- Data integrity of 16-bit CRC, parity, bit coding, bit counting

- Operating distance of up to 100 mm (depending on various parameters, such as field strength and antenna geometry)

- True anticollision

- Unique 7 byte serial number (cascade level 2 according to ISO/IEC 14443-3 (see Ref. 2)

## 2.3 Memory

- 1912 bytes freely available with User Read/Write area (478 pages with 4 bytes per pages) for the 2k version

- 888 bytes freely available with User Read/Write area (222 pages with 4 bytes per pages) for the 1k version

- 64 bytes SRAM volatile memory without write endurance limitation

- Data retention time of minimum 20 years

- EEPROM write endurance minimum 500.000 cycles

### 2.4 I<sup>2</sup>C interface

- I<sup>2</sup>C slave interface supports frequencies up to 400 kHz (see Section 13.1)

- 16 bytes (one block) written in 4.5 ms (EEPROM) or 0.4 ms (SRAM pass-through mode) including all overhead

- RFID chip can be used as standard I<sup>2</sup>C EEPROM and I<sup>2</sup>C SRAM

### 2.5 Security

- Manufacturer-programmed 7-byte UID for each device

- Capability container with one time programmable bits

- Field programmable read-only locking function per page for first 12 pages and per 16 (1k version) or 32 (2k version) pages for the extended memory section

- ECC-based originality signature

- 32-bit password protection to prevent unauthorized memory operations from NFC perspective may be enabled for parts of, or complete memory

- Access to protected data from I<sup>2</sup>C perspective may be restricted

- Pass-through and mirror mode operation may be password protected

- Protected data can be safeguarded against limited number of negative password authentication attempts

### 2.6 Key benefits

- Full interoperability with every NFC-enabled device

- Smooth end-user experience with super-fast data exchange via NFC and I<sup>2</sup>C interface

- Zero-power operation with non-volatile data storage

- Lowest bill of materials and smallest footprint for NFC solution in embedded electronics

- Data protection to prevent unauthorized data manipulation

- Multi-application support, enabled by memory size and segmentation options

# 3. Applications

NXP NTAG I<sup>2</sup>C *plus* is a family of connected NFC tags that combine a passive NFC interface with a contact I<sup>2</sup>C interface. As the second generation of NXP's industry-leading connected-tag technology, these devices maintain full backward compatibility with first-generation NTAG I<sup>2</sup>C products, while adding new, advanced features for password protection, full memory-access configuration from both interfaces, and an originality signature for protection against cloning.

The second-generation technology provides four times higher pass-through performance, along with energy harvesting capabilities, yet NTAG I<sup>2</sup>C *plus* devices are optimized for use in entry-level NFC applications like:

- IoT nodes (home automation, smart home, etc.)

- Pairing and configuration of consumer applications

- NFC accessories (headsets, speakers, etc.)

- Wearable infotainment

- Fitness equipment

- Consumer electronics

- Healthcare

- Smart printers

- Meters

- Electronic shelf labels

# 4. Ordering information

Table 1. Ordering information

| Type number   | Package       |                                                                                                                                                                   |          |

|---------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|               | Name          | Description                                                                                                                                                       | Version  |

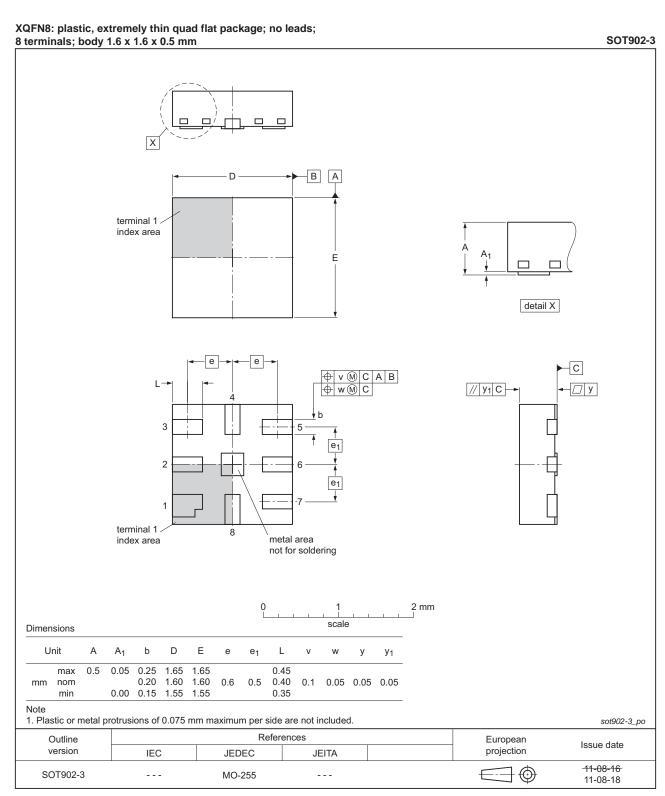

| NT3H2111W0FHK | XQFN8         | Plastic, extremely thin quad flat package; no leads; 8 terminals; body 1.6 x 1.6 x 0.6 mm; 1k bytes memory, 50pF input capacitance                                | SOT902-3 |

| NT3H2211W0FHK | XQFN8         | Plastic, extremely thin quad flat package; no leads; 8 terminals; body 1.6 x 1.6 x 0.6 mm; 2k bytes memory, 50pF input capacitance                                | SOT902-3 |

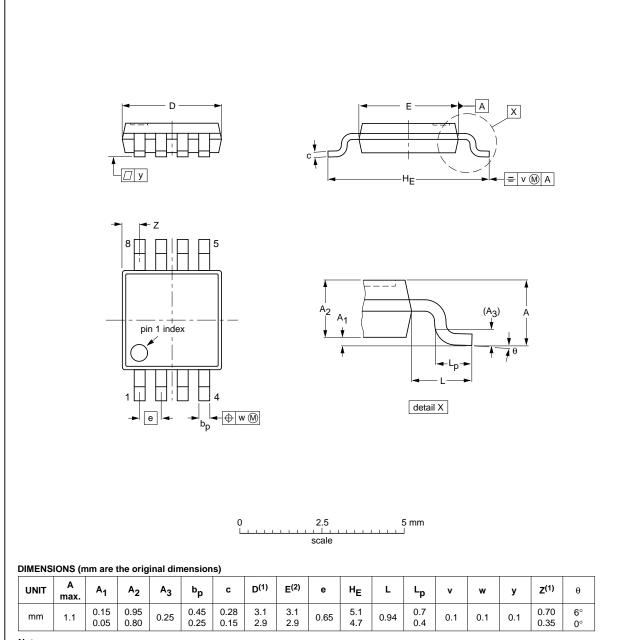

| NT3H2111W0FTT | TSSOP8        | Plastic thin shrink small outline package; 8 leads; body width 3 mm; 1k bytes memory; 50pF input capacitance                                                      | SOT505-1 |

| NT3H2211W0FTT | TSSOP8        | Plastic thin shrink small outline package; 8 leads; body width 3 mm; 2k bytes memory; 50pF input capacitance                                                      | SOT505-1 |

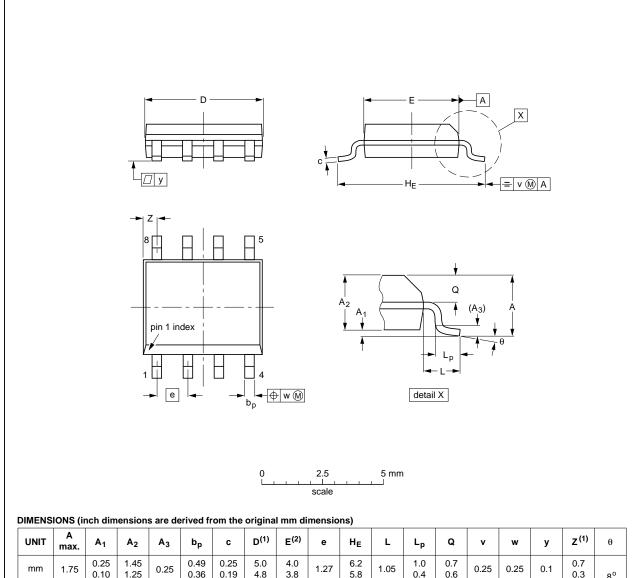

| NT3H2111W0FT1 | SO8           | Plastic small outline package; 8 leads; body width 3.9 mm, 1k bytes memory; 50pF input capacitance                                                                | SOT96-1  |

| NT3H2211W0FT1 | SO8           | Plastic small outline package; 8 leads; body width 3.9 mm, 2k bytes memory; 50pF input capacitance                                                                | SOT96-1  |

| NT3H2111W0FUG | FFC<br>bumped | 8 inch wafer, 150um thickness, on film frame carrier, electronic fail die marking according to SECS-II format), Au bumps, 1k Bytes memory, 50pF input capacitance | -        |

| NT3H2211W0FUG | FFC<br>bumped | 8 inch wafer, 150um thickness, on film frame carrier, electronic fail die marking according to SECS-II format), Au bumps, 2k Bytes memory, 50pF input capacitance | -        |

# 5. Marking

Table 2. Marking codes

| Table 21 Marking Codes |              |           |        |  |  |  |  |  |  |

|------------------------|--------------|-----------|--------|--|--|--|--|--|--|

| Type number            | Marking code |           |        |  |  |  |  |  |  |

| Type number            | Line 1       | Line 2    | Line 3 |  |  |  |  |  |  |

| NT3H2111FHK            | 211          | -         | -      |  |  |  |  |  |  |

| NT3H2211FHK            | 221          | -         | -      |  |  |  |  |  |  |

| NT3H2111W0FTT          | 32111        | DBSN ASID | yww    |  |  |  |  |  |  |

| NT3H2211W0FTT          | 32211        | DBSN ASID | yww    |  |  |  |  |  |  |

| NT3H2111W0FT1          | NT32111      | DBSN ASID | nDyww  |  |  |  |  |  |  |

| NT3H2211W0FT1          | NT32211      | DBSN ASID | nDyww  |  |  |  |  |  |  |

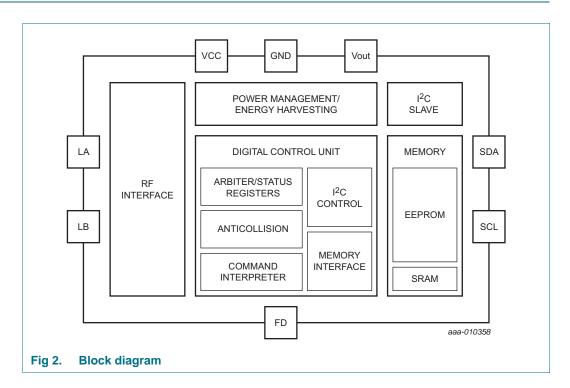

# 6. Block diagram

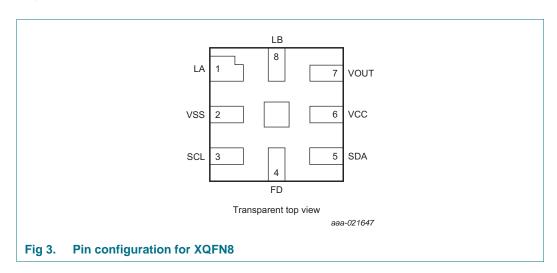

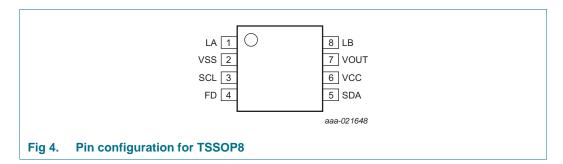

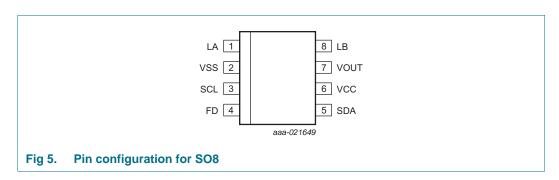

# 7. Pinning information

# 7.1 Pinning

### 7.1.1 XQFN8

### 7.1.2 TSSOP8

### 7.1.3 SO8

# 7.2 Pin description

Table 3. Pin description for XQFN8, TSSOP8 and SO8

| Pin | Symbol | Description                               |

|-----|--------|-------------------------------------------|

| 1   | LA     | Antenna connection LA                     |

| 2   | VSS    | GND                                       |

| 3   | SCL    | Serial clock I <sup>2</sup> C             |

| 4   | FD     | Field detection                           |

| 5   | SDA    | Serial data I <sup>2</sup> C              |

| 6   | VCC    | VCC in connection (external power supply) |

| 7   | VOUT   | Voltage out (energy harvesting)           |

| 8   | LB     | Antenna connection LB                     |

# 8. Functional description

## 8.1 Block description

NTAG I<sup>2</sup>C *plus* ICs consist of EEPROM, SRAM, NFC interface, Digital Control Unit (Command interpreter, Anticollision, Arbiter/Status registers, I<sup>2</sup>C control and Memory Interface), Power Management and Energy Harvesting Unit and an I<sup>2</sup>C slave interface. Energy and data are transferred via an antenna consisting of a coil with a few turns, which is directly connected to NTAG I<sup>2</sup>C *plus* IC.

### 8.2 NFC interface

The passive NFC-interface is based on the ISO/IEC 14443-3 Type A standard.

It requires to be supplied by an NFC field (e.g. NFC enabled device) always to be able to receive appropriate commands and send the related responses.

As defined in ISO/IEC 14443-3 Type A for both directions of data communication, there is one start bit (start of communication) at the beginning of each frame. Each byte is transmitted with an odd parity bit at the end. The LSB of the byte with the lowest address of the selected block is transmitted first.

For a multi-byte parameter, the least significant byte is always transmitted first. For example, when reading from the memory using the READ command, byte 0 from the addressed block is transmitted first, followed by bytes 1 to byte 3 out of this block. The same sequence continues for the next block and all subsequent blocks.

### 8.2.1 Data integrity

The following mechanisms are implemented in the contactless communication link between the NFC device and the NTAG I<sup>2</sup>C *plus* IC to ensure very reliable data transmission:

- 16 bits CRC per block

- · Parity bits for each byte

- Bit count checking

- Bit coding to distinguish between "1", "0" and "no information"

- Channel monitoring (protocol sequence and bit stream analysis)

The commands are initiated by the NFC device and controlled by the Digital Control Unit of the NTAG I<sup>2</sup>C *plus* IC. The command response depends on the state of the IC, and for memory operations, the access conditions valid for the corresponding page.

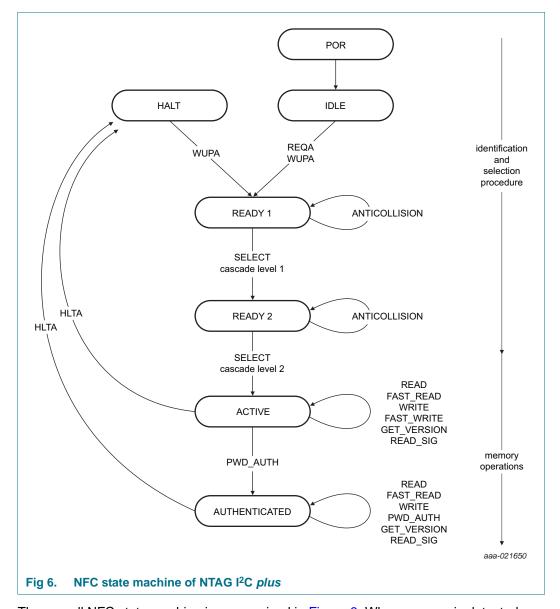

### 8.2.2 NFC state machine

The overall NFC state machine is summarized in <u>Figure 6</u>. When an error is detected or an unexpected command is received, in each state the tag returns to IDLE or HALT state as defined in ISO/IEC 14443-3 Type A.

#### 8.2.2.1 IDLE state

After a Power-On Reset (POR), the NTAG I<sup>2</sup>C *plus* switches to the default waiting state, namely the IDLE state. It exits IDLE towards READY 1 state when a REQA or a WUPA command is received from the NFC device. Any other data received while in IDLE state is interpreted as an error, and the NTAG I<sup>2</sup>C *plus* remains in the IDLE state.

#### 8.2.2.2 READY 1 state

In the READY 1 state, the NFC device resolves the first part of the UID (3 bytes) using the ANTICOLLISION or SELECT commands for cascade level 1. READY 1 state is correctly exited after execution of the following command:

SELECT command from cascade level 1 with the matching complete first part of the UID: the NFC device switches the NTAG I<sup>2</sup>C plus into READY 2 state where the second part of the UID is resolved.

### 8.2.2.3 READY 2 state

In the READY 2 state, the NFC device resolves the second part of the UID (4 bytes) using the ANTICOLLISION or SELECT command for cascade level 2. READY2 state is correctly exited after execution of the following command:

SELECT command from cascade level 2 with the matching complete second part of the UID: the NFC device switches the NTAG I<sup>2</sup>C plus into ACTIVE state where all application-related commands can be executed.

**Remark:** The response of the NTAG I<sup>2</sup>C *plus* to the SELECT command is the Select AcKnowledge (SAK) byte. In accordance with ISO/IEC 14443-3 Type A, this byte indicates if the anticollision cascade procedure has finished. If finished, the NTAG I<sup>2</sup>C *plus* is now uniquely selected and only this device will communicate with the NFC device even when other contactless devices are present in the NFC device field.

#### 8.2.2.4 ACTIVE state

All unprotected memory operations are operated in the ACTIVE and AUTHENTICATED states.

The ACTIVE state is exited with the PWD\_AUTH command and upon reception of a correct password, the NTAG I<sup>2</sup>C *plus* transits to AUTHENTICATED state after responding with PACK or with the HLTA command the NTAG I<sup>2</sup>C *plus* transits to the HALT state.

Any other data received when the device is in ACTIVE state is interpreted as an error. Depending on its previous state, the NTAG I<sup>2</sup>C *plus* returns to either to the IDLE or HALT state.

#### 8.2.2.5 AUTHENTICATED state

Protected memory operations are only operated in the AUTHENTICATED state, however access to the unprotected memory is possible, too.

The AUTHENTICATED state is exited with the HLTA command and upon reception, the NTAG I<sup>2</sup>C *plus* transits to the HALT state. Any other data received when the device is in AUTHENTICATED state is interpreted as an error. Depending on its previous state, the NTAG I<sup>2</sup>C *plus* returns to either to the IDLE or HALT state.

#### 8.2.2.6 HALT state

HALT and IDLE states constitute the two waiting states implemented in the NTAG I<sup>2</sup>C *plus*. An already processed NTAG I<sup>2</sup>C *plus* in ACTIVE or AUTHENTICATED state can be set into the HALT state using the HLTA command. In the anticollision phase, this state helps the NFC device distinguish between processed tags and tags yet to be selected.

The NTAG I<sup>2</sup>C *plus* can only exit HALT state upon execution of the WUPA command. Any other data received when the device is in this state is interpreted as an error, and NTAG I<sup>2</sup>C *plus* state remains unchanged.

## 8.3 Memory organization

The memory map is detailed in <u>Table 4</u> (1k memory) and <u>Table 5</u> (2k memory) from the NFC interface and in <u>Table 6</u> (1k memory) and <u>Table 7</u> (2k memory) from the I<sup>2</sup>C interface. The SRAM memory is not accessible from the NFC interface, because in the default settings of the NTAG I<sup>2</sup>C *plus* the pass-through mode is disabled. Please refer to <u>Section 11</u> for examples of memory map from the NFC interface with SRAM mapping.

The structure of manufacturing data, static and dynamic lock bytes, capability container and user memory pages are compatible with other NTAG products.

Any memory access which starts at a valid address and extends into an invalid access region will return 00h value in the invalid region.

### 8.3.1 Memory map from NFC perspective

Memory access from the NFC perspective is organized in pages of 4 bytes each. If password protection is not used, whole user memory is unprotected.

Table 4. NTAG I<sup>2</sup>C plus 1k memory organization from the NFC perspective

| Sector | Page a | ddress | E      | lyte number                  | Access cond.   | Access cond. |                   |                   |  |

|--------|--------|--------|--------|------------------------------|----------------|--------------|-------------------|-------------------|--|

| ddress | Dec.   | Hex.   | 0      | 1                            | 2              | 3            | ACTIVE state      | AUTH. state       |  |

| 0      | 0      | 00h    |        | Serial r                     | number         |              | READ              |                   |  |

|        | 1      | 01h    | (      | Serial number                | •              | Internal     | READ              |                   |  |

|        | 2      | 02h    | Inte   | rnal                         | Static lo      | ck bytes     | READ/R&W          |                   |  |

|        | 3      | 03h    |        | Capability Co                | ntainer (CC)   |              | READ8             | WRITE             |  |

|        | 4      | 04h    |        | Unprotected (                | user memory    |              | DEVD8             | WRITE             |  |

|        |        |        |        | Onprotected                  | user memory    |              | NLADO             |                   |  |

|        | AUTH0  | AUTH0  |        |                              |                |              |                   |                   |  |

|        |        |        |        | Protected us                 | ser memory     |              | READ <sup>1</sup> | READ&WRITE        |  |

|        | 225    | E1h    |        |                              |                |              |                   |                   |  |

|        | 226    | E2h    | Dyr    | namic lock by                | tes            | 00h          | R&W/              | READ              |  |

|        | 227    | E3h    | RFU    | RFU                          | RFU            | AUTH0        | READ <sup>1</sup> | READ&WRITE        |  |

|        | 228    | E4h    | ACCESS | RFU                          | RFU            | RFU          | READ <sup>1</sup> | READ&WRITE        |  |

|        | 229    | E5h    |        | PW                           | D <sup>2</sup> |              | READ <sup>1</sup> | READ&WRITE        |  |

|        | 230    | E6h    | PAC    | CK <sup>2</sup>              | RFU            | RFU          | READ <sup>1</sup> | READ&WRITE        |  |

|        | 231    | E7h    | PT_I2C | RFU                          | RFU            | RFU          | READ <sup>1</sup> | READ&WRITE        |  |

|        | 232    | E8h    |        | Configuration                | see 8.3.12     |              |                   |                   |  |

|        | 233    | E9h    |        | Corniguran                   | See <u>c</u>   | <u> </u>     |                   |                   |  |

|        | 234    | EAh    | 1.     | nvalid access                | roturno NA     | n.a.         |                   |                   |  |

|        | 235    | EBh    |        | Ivaliu access                | - returns mar  | `            | n.a.              |                   |  |

|        | 236    | ECh    |        | Session registers see 8.3.12 |                | 2.42         |                   |                   |  |

|        | 237    | EDh    |        | Session                      | registers      |              | see <u>c</u>      | see <u>8.3.12</u> |  |

|        | 238    | EEh    | 1.     | walid aaaaa                  | roturno NA     | ,            | _                 |                   |  |

|        | 239    | EFh    | 11     | nvalid access                | - returns inar | `            | n.                | a.                |  |

|        | 240    | F0h    |        |                              |                |              |                   |                   |  |

|        |        |        | lı     | nvalid access                | - returns NA   | (            | n.                | a.                |  |

|        | 255    | FFh    |        |                              |                |              |                   |                   |  |

| 1      |        |        | lı     | nvalid access                | - returns NA   | (            | n.                | a.                |  |

| 2      |        |        | lı     | nvalid access                | - returns NA   | (            | n.                | a.                |  |

| 3      | 0      | 00h    | 1.     | wolid cases                  | notures NIAI   | ,            | _                 |                   |  |

|        |        |        | li li  | nvalid access                | n.             | a.           |                   |                   |  |

|        | 248    | F8h    |        | N 41:                        |                |              |                   | 2.0.40            |  |

|        | 249    | F9h    |        | Mirrored session registers   |                |              |                   | <u>3.3.12</u>     |  |

|        |        |        |        | 1. 1                         | ,              | ,            |                   |                   |  |

|        | 255    | FFh    | li li  | nvalid access                | n.             | a.           |                   |                   |  |

<sup>2</sup> On reading PWD or PACK, NTAG I<sup>2</sup>C plus returns always 00h for all bytes

© NXP Semiconductors N.V. 2016. All rights reserved.

Product data sheet COMPANY PUBLIC

Table 5. NTAG I<sup>2</sup>C plus 2k memory organization from the NFC perspective

| Sector  | Page a | ddress | E                | lyte number v   | vithin a page           | е        | Access cond.      | Access cond.   |  |

|---------|--------|--------|------------------|-----------------|-------------------------|----------|-------------------|----------------|--|

| address | Dec.   | Hex.   | 0                | 1               | 2                       | 3        | ACTIVE state      | AUTH. state    |  |

| 0       | 0      | 00h    |                  | Serial n        | umber                   |          | RE                | AD             |  |

|         | 1      | 01h    | 9                | Serial number   |                         | Internal | RE                | READ           |  |

|         | 2      | 02h    | Inter            | rnal            | Static lo               | ck bytes | READ/R&W          |                |  |

|         | 3      | 03h    |                  | Capability Co   | ntainer (CC)            |          | READ8             | WRITE          |  |

|         | 4      | 04h    |                  | Unprotected u   | ser memory              |          | READ8             | WRITE          |  |

|         |        |        |                  | Onprotected t   | oci momory              |          | NE/ND0            |                |  |

|         | AUTH0  | AUTH0  |                  |                 |                         |          |                   |                |  |

|         |        |        |                  | Protected us    | er memory               |          | READ <sup>1</sup> | READ&WRITE     |  |

|         | 225    | E1h    |                  |                 |                         |          |                   |                |  |

|         | 226    | E2h    | Dyr              | namic lock byte | es                      | 00h      | R&W/              | READ           |  |

|         | 227    | E3h    | RFU              | RFU             | RFU                     | AUTH0    | READ <sup>1</sup> | READ&WRITE     |  |

|         | 228    | E4h    | ACCESS           | RFU             | RFU                     | RFU      | READ <sup>1</sup> | READ&WRITE     |  |

|         | 229    | E5h    | PWD <sup>2</sup> |                 |                         |          | READ <sup>1</sup> | READ&WRITE     |  |

|         | 230    | E6h    | PAC              | CK <sup>2</sup> | RFU                     | RFU      | READ <sup>1</sup> | READ&WRITE     |  |

|         | 231    | E7h    | PT_I2C           | RFU             | RFU                     | RFU      | READ <sup>1</sup> | READ&WRITE     |  |

|         | 232    | E8h    |                  | Configuratio    | 500                     | 3.3.12   |                   |                |  |

|         | 233    | E9h    |                  | Comiguratio     | 366 0                   | 5.5.12   |                   |                |  |

|         | 234    | EAh    | l,               | nvalid access   | n.a.                    |          |                   |                |  |

|         | 235    | EBh    | "                | Ivaliu access   | · ICIUIIIS INAI         | `        | 11.               | a.             |  |

|         | 236    | ECh    |                  | Session r       | ogietore                |          | see 8.3.12        |                |  |

|         | 237    | EDh    |                  | 362210111       | egisters                |          | See <u>6.3.12</u> |                |  |

|         | 238    | EEh    |                  |                 |                         |          |                   |                |  |

|         |        |        | Ir               | nvalid access   | returns NA              | <        | n.                | a.             |  |

|         | 255    | FFh    |                  |                 |                         |          |                   |                |  |

|         | 0      | 00h    |                  |                 |                         |          |                   |                |  |

| 1       |        |        | (U               | n-)protected u  | ser memory <sup>3</sup> | 3,4      |                   | user memory in |  |

|         | 255    | FFh    | •                |                 | ·                       |          | Sec               | tor u          |  |

| 2       |        |        | l <sub>v</sub>   | nvalid access   | roturne NAk             | ·        |                   | 2              |  |

|         |        | •••    | III.             | Ivaliu access   | · IEIUIIIS INAI         | `        | 11.               | a.             |  |

| 3       | 0      | 00h    | lr               | nvalid access   | returns NA              | <        | n.                | a.             |  |

|         |        |        |                  |                 |                         |          |                   |                |  |

|         | 248    | F8h    |                  | Mirrored sess   | ion registers           |          | see 8             | 3.3.12         |  |

|         | 249    | F9h    |                  |                 | .c.i iogiotoio          |          | 330 2             |                |  |

|         |        |        | Ir               | nvalid access   | returns NA              | <        | n                 | a.             |  |

|         | 255    | FFh    |                  | Traile doods    | TOTALIO INAL            |          |                   | <b>~</b> .     |  |

<sup>&</sup>lt;sup>1</sup> If NFC\_PROT bit is set to 1b, NTAG I<sup>2</sup>C plus returns NAK

<sup>&</sup>lt;sup>2</sup> On reading PWD or PACK, NTAG I<sup>2</sup>C plus returns always 00h for all bytes

<sup>&</sup>lt;sup>3</sup> If 2K\_PROT bit is set to 1b, complete Sector 1 of NTAG I<sup>2</sup>C *plus* is password protected

<sup>&</sup>lt;sup>4</sup> If NFC\_DIS\_SEC1 bit is set to 1b, complete Sector 1 of NTAG I<sup>2</sup>C plus is not accessible from NFC perspective

# NT3H2111/NT3H2211

NFC Forum Type 2 Tag compliant IC with I<sup>2</sup>C interface

# 8.3.2 Memory map from I<sup>2</sup>C interface

The memory access of NTAG  $I^2C$  *plus* from the  $I^2C$  interface is organized in blocks of 16 bytes each.

Table 6. NTAG I<sup>2</sup>C plus 1k memory organization from the I<sup>2</sup>C perspective

|       |        | Ву                                  | yte number v    | within a bloc   | ı        | , i         | Access conditions     |       |  |  |

|-------|--------|-------------------------------------|-----------------|-----------------|----------|-------------|-----------------------|-------|--|--|

|       | olock  | 0                                   | 1               | 2               | 3        |             | I <sup>2</sup> C_PROT |       |  |  |

| add   | ress   | 4                                   | 5               | 6               | 7        |             | 10_1101               |       |  |  |

|       |        | 8                                   | 9               | 10              | 11       | 00b         | 01b                   | 1xb   |  |  |

| Dec.  | Hex.   | 12                                  | 13              | 14              | 15       | 000         | UID                   | IXU   |  |  |

| 0     | 00h    | I <sup>2</sup> C addr. <sup>1</sup> | Ş               | Serial number   | r        |             |                       |       |  |  |

|       |        | 5                                   | Serial numbe    | r               | Internal |             | READ&WRITE            |       |  |  |

|       |        | Inter                               | rnal            | Static lo       | ck bytes |             | READQUAITE            |       |  |  |

|       |        |                                     | Capability Co   | ntainer (CC)    |          |             |                       |       |  |  |

| 1     | 01h    |                                     |                 |                 |          |             |                       |       |  |  |

|       |        | Į                                   | Unprotected     | user memory     |          |             | READ&WRITE            |       |  |  |

|       |        |                                     |                 |                 |          |             |                       |       |  |  |

| AUTH0 | AUTH0  |                                     |                 |                 |          |             |                       |       |  |  |

|       |        |                                     | Protected us    | eer momon?      |          | READ&WRITE  | READ                  | NAK   |  |  |

|       |        |                                     | Fiolected u     | sei memory      |          | READQUAITE  | READ                  | NAK   |  |  |

|       |        |                                     |                 |                 |          |             |                       |       |  |  |

| 56    | 38h    |                                     | Protected us    | ser memon/      |          | READ&WRITE  | READ                  | NAK   |  |  |

|       |        |                                     | i iolecteu u    | sei illeilloly  |          | READQUIRITE | NEAD                  | IVAIX |  |  |

|       |        | Dyr                                 | namic lock by   | tes             | 00h      |             |                       |       |  |  |

|       |        | RFU                                 | RFU             | RFU             | AUTH0    |             |                       |       |  |  |

| 57    | 57 39h | ACCESS                              | RFU             | RFU             | RFU      |             | READ&WRITE            |       |  |  |

|       |        |                                     | PW              | /D <sup>2</sup> |          |             | READOWNITE            |       |  |  |

|       |        | PAC                                 | CK <sup>2</sup> | RFU             | RFU      |             |                       |       |  |  |

|       |        | PT_I2C                              | RFU             | RFU             | RFU      |             |                       |       |  |  |

| 58    | 3Ah    |                                     | Configuration   | on registers    |          | see 8.3.12  |                       |       |  |  |

|       |        |                                     | Oomigaran       | on regiotore    |          |             | 000 0.0.12            |       |  |  |

|       |        | 00h                                 | 00h             | 00h             | 00h      |             | READ                  |       |  |  |

|       |        | 00h                                 | 00h             | 00h             | 00h      |             | KEKB                  |       |  |  |

| 59    | 3Bh    |                                     |                 |                 |          |             |                       |       |  |  |

| •••   |        | In                                  | valid access    | - returns NAI   | K        |             | n.a.                  |       |  |  |

| 247   | F7h    |                                     |                 |                 |          |             |                       |       |  |  |

| 248   | F8h    |                                     |                 |                 |          |             |                       |       |  |  |

|       |        |                                     | SRAM memo       | ory (64 bytes)  |          |             | READ&WRITE            |       |  |  |

| 251   | FBh    |                                     |                 |                 |          |             |                       |       |  |  |

|       |        | In                                  | valid access    | n.a.            |          |             |                       |       |  |  |

| 254   | FEh    |                                     | Session         | registers       |          |             | see 8.3.12            |       |  |  |

|       |        |                                     |                 | <u>-</u>        | I-       |             |                       |       |  |  |

|       |        | 00h                                 | 00h             | 00h             | 00h      |             | READ                  |       |  |  |

|       |        | 00h                                 | 00h             | 00h             | 00h      | NEAD        |                       |       |  |  |

|       |        | In                                  | valid access    | - returns NAI   | K        |             | n.a.                  |       |  |  |

<sup>&</sup>lt;sup>1</sup> The byte 0 of block 0 is always read as 04h. Writing to this byte modifies the I<sup>2</sup>C address.

<sup>&</sup>lt;sup>2</sup> On reading PWD and PACK, NTAG I<sup>2</sup>C plus returns always 00h for all bytes

Table 7. NTAG I<sup>2</sup>C plus 2k memory organization from the I<sup>2</sup>C perspective

|      |       | Ву                                  | yte number v    | within a bloc  | ı        | P                 | ccess conditions      |       |  |

|------|-------|-------------------------------------|-----------------|----------------|----------|-------------------|-----------------------|-------|--|

|      | olock | 0                                   | 1               | 2              | 3        |                   | I <sup>2</sup> C_PROT |       |  |

| add  | ress  | 4                                   | 5               | 6              | 7        |                   | 10_1101               |       |  |

|      |       | 8                                   | 9               | 10             | 11<br>15 | 00b               | 01b                   | 1xb   |  |

| Dec. | Hex.  | 12                                  | 13              | 14             |          | 000               | OID                   | IAU   |  |

| 0    | 00h   | I <sup>2</sup> C addr. <sup>1</sup> | 9               | Serial number  | r        |                   |                       |       |  |

|      |       | 5                                   | Serial number   | r              | Internal |                   | READ&WRITE            |       |  |

|      |       | Inter                               | rnal            | Static lo      | ck bytes |                   | READQWRITE            |       |  |

|      |       | (                                   | Capability Co   | ntainer (CC)   |          |                   |                       |       |  |

| 1    | 01h   |                                     |                 |                |          |                   |                       |       |  |

|      |       | ι                                   | Jnprotected (   | user memory    |          |                   | READ&WRITE            |       |  |

|      |       |                                     |                 |                |          |                   |                       |       |  |

| UTH0 | AUTH0 |                                     | Due to etc. d   |                |          | DE A D Q M DITE   | DEAD                  | NIAIZ |  |

|      |       |                                     | Protected us    | ser memory     |          | READ&WRITE        | READ                  | NAK   |  |

| 56   | 38h   |                                     | Protected us    | ser memory     |          | READ&WRITE        | READ                  | NAK   |  |

|      |       |                                     | Protected us    | ser memory     |          |                   |                       |       |  |

|      |       | Dyr                                 | namic lock by   | tes            | 00h      |                   |                       |       |  |

|      |       | RFU                                 | RFU             | RFU            | AUTH0    |                   |                       |       |  |

| 57   | 39h   | ACCESS                              | RFU             | RFU            | RFU      |                   | DE A DOMESTE          |       |  |

|      |       |                                     | PW              | /D²            |          |                   | READ&WRITE            |       |  |

|      |       | PAC                                 | CK <sup>2</sup> | RFU            | RFU      |                   |                       |       |  |

|      |       | PT_I2C                              | RFU             | RFU            | RFU      |                   |                       |       |  |

| 58   | 3Ah   |                                     | 0 " "           |                |          |                   | 0.0.40                |       |  |

|      |       |                                     | Configuration   | on registers   |          | see <u>8.3.12</u> |                       |       |  |

|      |       | 00h                                 | 00h             | 00h            | 00h      |                   | DEAD                  |       |  |

|      |       | 00h                                 | 00h             | 00h            | 00h      |                   | READ                  |       |  |

|      |       | In                                  | valid access    | - returns NAI  | K        |                   | n.a.                  |       |  |

| 64   | 40h   |                                     |                 |                |          |                   |                       |       |  |

|      |       | (L                                  | Jn-)protected   | l user memor   | у        | READ&WRITE        | READ                  | NAK   |  |

| 127  | 7Fh   |                                     |                 |                |          |                   |                       |       |  |

|      |       | In                                  | valid access    | - returns NAI  | K        |                   | n.a.                  |       |  |

| 248  | F8h   |                                     |                 |                |          |                   |                       |       |  |

|      |       |                                     | SRAM memo       | ory (64 bytes) |          |                   | READ&WRITE            |       |  |

| 251  | FBh   |                                     |                 |                |          |                   |                       |       |  |

|      |       | In                                  | valid access    | - returns NAI  | K        |                   | n.a.                  |       |  |

| 254  | FEh   |                                     | •               |                |          | see <u>8.3.12</u> |                       |       |  |

|      |       |                                     | Session         | registers      |          |                   |                       |       |  |

|      |       | 00h                                 | 00h             | 00h            | 00h      |                   |                       |       |  |

|      |       | 00h                                 | 00h             | 00h            | 00h      |                   | READ                  |       |  |

|      |       |                                     |                 | - returns NAI  |          |                   | n.a.                  |       |  |

<sup>&</sup>lt;sup>1</sup> The byte 0 of block 0 is always read as 04h. Writing to this byte modifies the I<sup>2</sup>C address.

<sup>&</sup>lt;sup>2</sup> On reading PWD and PACK, NTAG I<sup>2</sup>C plus returns always 00h for all bytes

### **8.3.3 EEPROM**

The EEPROM is a non-volatile memory that stores the 7 byte UID, the memory lock conditions, IC configuration information and the 1912 bytes of user memory (888 byte user memory in case of the NTAG I<sup>2</sup>C *plus* 1k version).

Sector 0 memory map looks totally the same for NTAG I<sup>2</sup>C *plus* 1k and 2k version, the only difference is the dynamic lock bit granularity.

NXP introduced with NTAG I<sup>2</sup>C *plus* the possibility to split the memory in an open and a password protected area see <u>Section 8.3.11</u>.

### 8.3.4 **SRAM**

For frequently changing data, a volatile memory of 64 bytes with unlimited endurance is built in. The 64 bytes are mapped in a similar way as done in the EEPROM, i.e., 64 bytes are seen as 16 pages of 4 bytes from NFC perspective.

The SRAM is only available if the tag is powered via the VCC pin.

The SRAM is located at the end of the memory space and it is always directly accessible by the I<sup>2</sup>C host (addresses F8h to FBh). An NFC device cannot access the SRAM memory in normal mode (i.e., outside the pass-through mode). The SRAM is only accessible by the NFC device if the SRAM is mirrored onto the EEPROM memory space.

With SRAM mirror enabled (SRAM\_MIRROR\_ON\_OFF = 1b - see <u>Section 11.2</u>), the SRAM can be mirrored in the User Memory from start page 01h to 74h for access from the NFC side.

The Memory mirror must be enabled once both interfaces are ON as this feature is disabled after each POR.

The register SRAM\_MIRROR\_BLOCK (see <u>Table 14</u>) indicates the address of the first page of the SRAM buffer. In the case where the SRAM mirror is enabled and the READ command is addressing blocks where the SRAM mirror is located, the SRAM byte values will be returned instead of the EEPROM byte values. Similarly, if the tag is not VCC powered, the SRAM mirror is disabled and reading out the bytes related to the SRAM mirror position would return the values from the EEPROM.

In the pass-through mode (PTHRU\_ON\_OFF = 1b - see Section 8.3.12), the SRAM is mirrored to the fixed address F0h - FFh for NFC access (see Section 11) in the first memory sector (Sector 0) for NTAG  $I^2C$  plus.

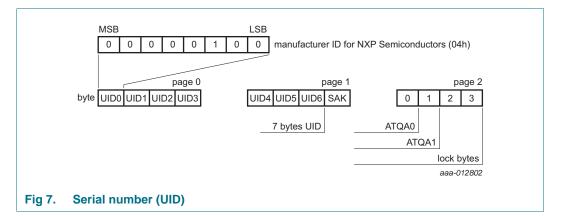

### 8.3.5 Serial number (UID)

The unique 7-byte serial number (UID) is programmed into the first 7 bytes of memory covering page addresses 00h and 01h - see <u>Figure 7</u>. These bytes are programmed and write protected during production.

UID0 is fixed to the value 04h - the manufacturer ID for NXP Semiconductors in accordance with ISO/IEC 14443-3.

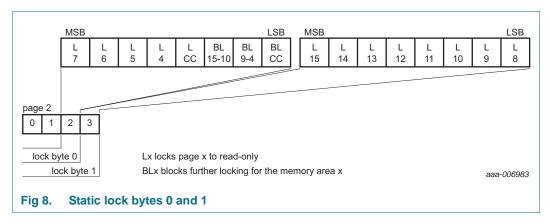

### 8.3.6 Static Lock Bytes

According to NFC Forum Type 2 Tag specification the bits of byte 2 and byte 3 of page 02h (via NFC) or byte 10 and 11 address 00h (via I<sup>2</sup>C) represent the field programmable, read-only locking mechanism (see <u>Figure 8</u>). Each page from 03h (CC) to 0Fh can be individually locked by setting the corresponding locking bit to logic 1b to prevent further write access. After locking, the corresponding page becomes read-only memory.

In addition NTAG I<sup>2</sup>C *plus* uses the three least significant bits of lock byte 0 as the block-locking bits. Bit 2 controls pages 0Ah to 0Fh (via NFC), bit 1 controls pages 04h to 09h (via NFC) and bit 0 controls page 03h (CC). Once the block-locking bits are set, the locking configuration for the corresponding memory area is frozen, e.g. cannot be changed to read-only anymore.

For example, if BL15-10 is set to logic 1b, then bits L15 to L10 (lock byte 1, bit[7:2]) can no longer be changed. The static locking and block-locking bits are set by the bytes 2 and 3 of the WRITE command to page 02h. The contents of the lock bytes are bit-wise OR'ed and the result then becomes the new content of the lock bytes. This process is irreversible from NFC perspective. If a bit is set to logic 1b, it cannot be changed back to logic 0b. From I<sup>2</sup>C perspective, the bits can be reset to 0b by writing bytes 10 and 11 of block 00h. As I<sup>2</sup>C address is coded in byte 0 of block 0, it may be changed unintentionally.

The contents of bytes 0 and 1 of page 02h (via NFC) are unaffected by the corresponding data bytes of the WRITE command.

The default value of the static lock bytes is 0000h.

### 8.3.7 Dynamic Lock Bytes

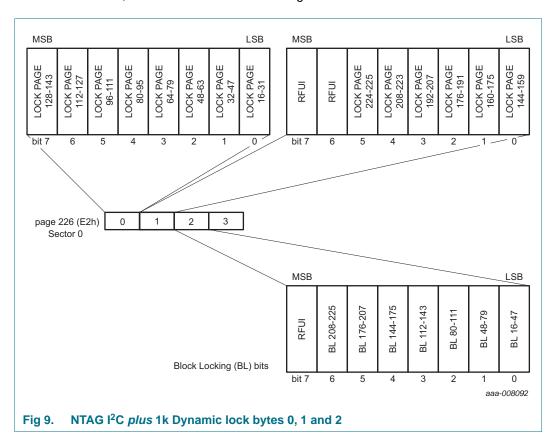

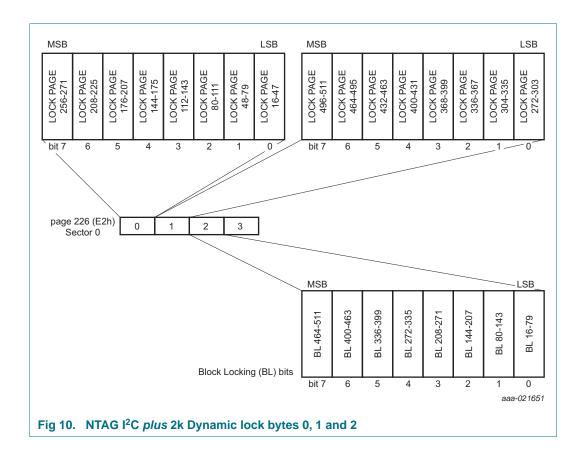

To lock the pages of NTAG I<sup>2</sup>C *plus* starting at page address 16 and onwards, the dynamic lock bytes are used. The dynamic lock bytes are located in Sector 0 at page E2h. The three lock bytes cover the memory area of 840 data bytes (NTAG I<sup>2</sup>C *plus* 1k) or 1864 data bytes (NTAG I<sup>2</sup>C *plus* 2k). The granularity is 16 pages for NTAG I<sup>2</sup>C *plus* 1k (see <u>Figure 9</u>) and 32 pages for NTAG I<sup>2</sup>C *plus* 2k (see <u>Figure 10</u>) compared to a single page for the first 48 bytes (see <u>Figure 8</u>).

NTAG I<sup>2</sup>C *plus* needs a Lock Control TLV as specified in NFC Forum Type 2 Tag specification to ensure NFC Forum Type 2 Tag compliancy.

When NFC Forum Type 2 Tag transition to READ ONLY state is intended, all bits marked as RFUI and dynamic lock bits related to the protected area shall be set to 0b when writing to the dynamic lock bytes.

The default value of the dynamic lock bytes is 000000h. The value of Byte 3 is always 00h when read.

Like for the static lock bytes, this process of modifying the dynamic lock bits is irreversible from NFC perspective. If a bit is set to logic 1b, it cannot be changed back to logic 0b. From I<sup>2</sup>C interface, these bits can be set to 0b again.

### 8.3.8 Capability Container (CC)

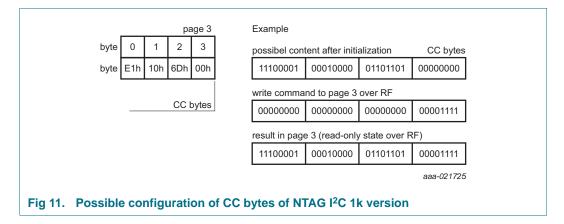

According to NFC Forum Type 2 Tag specification the CC is located on page 03h (see Ref. 1). To keep full flexibility to split the memory into an open and protected area, the default value of the CC is initialized with 00000000h during the IC production.

NDEF messages can only be written, when these CC bytes are set according to application-specific needs and NFC Forum specification by a WRITE command from the I²C or NFC interface. According to NFC Forum specification once set to 1b, an NFC Forum Device cannot set bits of the CC back to 0b. However, similar to the lock bits, setting these bits back to 0b is again possible from I²C perspective. As long as I²C address (byte 0) and static lock bytes (byte 10 and byte 11) are coded in block 00h, the I²C address may be changed unintentionally.

NXP recommends setting the size parameter of the CC only to values that the T2T\_Area ends at lock bit granularity boundaries when using only part of the memory for storing NDEF messages. Consequently T2T\_Area size should be 112 + 64\*N or 888 bytes with N less or equal to 13 for the 1k version, or 176 + 128\*N or 2032 bytes with N less or equal to 14 for the 2k version.

Note that the maximum NDEF Control TLV size is 883 bytes (5 bytes are needed for the Lock Control TLV) for the 1K version and 1902 bytes (5 bytes each for Lock Control TLV and Memory Control TLV to exclude 120 bytes reserved area at the end of sector 0) for the 2k version.

In <u>Figure 11</u> it is shown how the CC is changed when going from READ/WRITE to READ ONLY state according to NFC Forum.

### 8.3.9 User Memory pages

Pages 04h to E1h of Sector 0 via the NFC interface - Block 01h to 37h, plus the first 8 bytes of block 38h via the I<sup>2</sup>C interface is the user memory area for NTAG I<sup>2</sup>C *plus* 1k and 2k version.

In addition, complete Sector 1 (page 00h to FFh) via the NFC interface - block 40h to 7Fh via the I<sup>2</sup>C interface is used as user memory area for NTAG I<sup>2</sup>C *plus* 2k version.

### 8.3.10 Memory content at delivery

As described above the CC in page 03h is set to all 00h to keep the full flexibility. To allow NFC Forum NDEF message reading and writing page 03h (CC) and the following data page (NDEF TLV) of NTAG I<sup>2</sup>C *plus* need to be initialized by the user according to the NFC Forum Type 2 Tag specification (see <u>Ref. 1</u>). <u>Table 8</u> shows an example of NFC Forum-compliant content using the whole memory of sector 0 for NDEF messages.

**Remark:** The default content of the data pages from page 04h onwards is not defined at delivery.

Table 8. Minimum memory content to be in initialized state for NTAG I<sup>2</sup>C plus

| Page Address | Byte number within page |                 |     |     |  |  |  |  |

|--------------|-------------------------|-----------------|-----|-----|--|--|--|--|

|              | 0 1 2 3                 |                 |     |     |  |  |  |  |

| 03h          | E1h                     | 10h             | 6Dh | 00h |  |  |  |  |

| 04h          | 03h                     | 03h 00h FEh 00h |     |     |  |  |  |  |

### 8.3.11 Password and Access Configuration

NTAG I<sup>2</sup>C *plus* can be configured to have password protected memory areas.

If this feature is used, NXP recommends changing and diversify the PWD and PACK for every single chip.

The password and access configuration area of pages E3h to E7h (Sector 0 - see <u>Table 9</u>) via the NFC interface or blocks 38h and 39h via the I<sup>2</sup>C interface are used to configure the password and access conditions of the NTAG I<sup>2</sup>C *plus*. Those bit values are stored in the EEPROM. Their values can be read and written by both interfaces when applicable and when not locked by the register lock bits (see REG\_LOCK in <u>Table 13</u>).

AUTH0 defines the starting page address of the protected area in Sector 0. NXP recommends setting AUTH0 in a way always respecting the lock bit granularity. Setting AUTH0 greater EBh, disables password protection.

The NFC\_PROT bit is used to either only require a PWD\_AUTH for writing data to the protected area or even protect reading data from the protected area.

If password authentication is used, even the SRAM access can be protected by setting SRAM\_PROT bit to 1b.

I2C\_PROT enables the possibility to limit access to the protected area from I<sup>2</sup>C perspective to read only or no access at all.

AUTLIM value can be used to limit negative PWD\_AUTH attempts.

For the 2k version of NTAG I<sup>2</sup>C *plus* NFC\_DIS\_SEC1 bit can be used to disable the access to Sector 1 from NFC perspective with the 2K\_PROT bit password protection for Sector 1 can be enabled.

Once password protection is enabled, writing to Password and Access Configuration bytes is only possible after a successful password authentication. On reading the PWD or PACK, from NFC or I<sup>2</sup>C perspective, NTAG I<sup>2</sup>C *plus* always returns all 00h bytes.

A detailed description of the mechanism and how to program all the parameters is given in <u>Section 8.7</u>.

Table 9.

Password and Access Configuration Register

| NFC page a (Sector 0) | address | I <sup>2</sup> C block | address | Byte number from NFC perspective |              |        | ective |  |

|-----------------------|---------|------------------------|---------|----------------------------------|--------------|--------|--------|--|

| Dec                   | Hex     | Dec                    | Hex     | 0                                | 1            | 2      | 3      |  |

| 224                   | E0h     | 56                     | 38h     |                                  | User M       | N.A    |        |  |

| 225                   | E1h     |                        |         |                                  | USEI IV      | lemory |        |  |

| 226                   | E2h     |                        |         | Dyn                              | amic lock by | /tes   | 00h    |  |

| 227                   | E3h     |                        |         | RFU                              | RFU          | RFU    | AUTH0  |  |

| 228                   | E4h     | 57                     | 39h     | ACCESS                           | RFU          | RFU    | RFU    |  |

| 229                   | E5h     |                        |         |                                  | PV           | VD     |        |  |

| 230                   | E6h     |                        |         | PA                               | CK           | RFU    | RFU    |  |

| 231                   | E7h     |                        |         | PT_I2C                           | RFU          | RFU    | RFU    |  |

Table 10. Password and Access Configuration bytes

| Bit  | Field        | Access via NFC | Access via I <sup>2</sup> C | Default values | Description                                                                                                                                                               |

|------|--------------|----------------|-----------------------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      |              |                | I                           | Authenticati   | on Pointer (AUTH0)                                                                                                                                                        |

| 7-0  | AUTH0        | R&W            | R&W                         | FFh            | Page address of Sector 0 from which onwards the password authentication is required to access the user memory from NFC perspective, dependent on NFC_PROT bit.            |

|      |              |                |                             |                | If AUTH0 is set to a page address greater than EBh, the password protection is effectively disabled. Password protected area starts from page AUTH0 and ends at page EBh. |

|      |              |                |                             |                | Password protection is excluded for Dynamic Lock Bits, session registers and mirrored SRAM pages.                                                                         |

|      |              |                |                             |                | Note: From I <sup>2</sup> C interface, you have access to all configuration pages until REG_LOCK_I2C bit is set to 1b.                                                    |

|      |              | 1              | 1                           | Access Cor     | nditions (ACCESS)                                                                                                                                                         |

| 7    | NFC_PROT     | R&W            | R&W                         | 0b             | Memory protection bit:                                                                                                                                                    |

|      |              |                |                             |                | 0b: write access to protected area is protected by the password                                                                                                           |

|      |              |                |                             |                | 1b: read and write access to protected area is protected by the password                                                                                                  |

| 6    | RFU          | R              | R                           | 0b             | RFU - keep at 0b                                                                                                                                                          |

| 5    | NFC_DIS_SEC1 | R&W            | R&W                         | 0b             | NFC access protection to Sector 1                                                                                                                                         |

|      |              |                |                             |                | 0b: Sector 1 is accessible in 2k version                                                                                                                                  |

|      |              |                |                             |                | 1b: Sector 1 in inaccessible and returns NAK0                                                                                                                             |

| 4-3  | RFU          | R              | R                           | 00b            | RFU - keep at 00b                                                                                                                                                         |

| 2-0  | AUTHLIM      | R&W            | R&W                         | 000b           | Limitation of negative password authentication attempts. After reaching the limit, protected area is not accessible any longer.                                           |

|      |              |                |                             |                | 000b: limiting of negative password authentication attempts disabled.                                                                                                     |

|      |              |                |                             |                | 001b-111b: maximum number of negative password authentication attempts is 2 <sup>AUTHLIM</sup>                                                                            |

|      | 1            |                | 1                           | Pass           | word (PWD)                                                                                                                                                                |

| 31-0 | PWD          | R&W            | R&W                         | FFFFFFFh       | 32-bit password used for memory access protection.                                                                                                                        |

|      |              |                |                             |                | Reading PWD always returns 0000000h                                                                                                                                       |

|      | 1            | 1              | 1                           | Password Ad    | cknowledge (PACK)                                                                                                                                                         |

| 15-0 | PACK         | R&W            | R&W                         | 0000h          | 16-bit password acknowledge used during the password authentication process.                                                                                              |

|      |              |                |                             |                | Reading PACK always returns 0000h                                                                                                                                         |

|      |              |                | 1                           | Protection     | on bits-(PT_I2C)                                                                                                                                                          |

| 7-4  | RFU          | R              | R                           | 0000b          | RFU - keep at 0000b                                                                                                                                                       |

Table 10. ...continuedPassword and Access Configuration bytes

| Bit | Field     | Access via NFC | Access via I <sup>2</sup> C | Default values | Description                                                                                                     |  |

|-----|-----------|----------------|-----------------------------|----------------|-----------------------------------------------------------------------------------------------------------------|--|

| 3   | 2K_PROT   | R&W            | R&W                         | 0b             | Password protection for Sector 1 for 2k version                                                                 |  |

|     |           |                |                             |                | 0b: password authentication for Sector 1 disabled                                                               |  |

|     |           |                |                             |                | 1b: password authentication needed to access Sector 1                                                           |  |

| 2   | SRAM_PROT | R&W            | R&W                         | Ob             | ·                                                                                                               |  |

| 1-0 | I2C_PROT  | R&W            | R&W                         | 00b            | Access to protected area from I <sup>2</sup> C perspective                                                      |  |

|     |           |                |                             |                | 00b: Entire user memory accessible from I <sup>2</sup> C                                                        |  |

|     |           |                |                             |                | 01b: read and write access to unprotected user area, read only access to protected area                         |  |

|     |           |                |                             |                | 1Xb: read and write access to unprotected area, no access to protected area.                                    |  |

|     |           |                |                             |                | Note: Independent from these bits I <sup>2</sup> C has always R/W access to:                                    |  |

|     |           |                |                             |                | Session registers                                                                                               |  |

|     |           |                |                             |                | • SRAM                                                                                                          |  |

|     |           |                |                             |                | <ul> <li>Configuration pages including PWD Configuration area, but<br/>dependent on REG_LOCK_I2C bit</li> </ul> |  |

## 8.3.12 NTAG I<sup>2</sup>C configuration and session registers

NTAG I<sup>2</sup>C *plus* behavior can be configured and read in two separate locations depending if the configurations shall be effective within the communication session (use session registers) or by default after Power-On Reset (POR) (use configuration registers).

The configuration registers of pages E8h to E9h (Sector 0 - see <u>Table 11</u>) via the NFC interface or block 3Ah via the I<sup>2</sup>C interface are used to configure the default behavior of the NTAG I<sup>2</sup>C *plus*. Those bit values are stored in the EEPROM and represent the default settings to be effective after POR. Their values can be read and written by both interfaces when applicable and when not locked by the register lock bits (see REG\_LOCK in <u>Table 13</u>).

Table 11. Configuration register NTAG I<sup>2</sup>C plus

| NFC ac<br>(Secto | ddress<br>r 0) | I <sup>2</sup> C Ad | dress | Byte number from NFC perspective |                 |                   |        |  |

|------------------|----------------|---------------------|-------|----------------------------------|-----------------|-------------------|--------|--|

| Dec              | Hex            | Dec                 | Hex   | 0 1 2 3                          |                 |                   |        |  |

| 232              | E8h            | 58                  | 3Ah   | NC_REG                           | LAST_NDEF_BLOCK | SRAM_MIRROR_BLOCK | WDT_LS |  |

| 233              | E9h            |                     |       | WDT_MS                           | I2C_CLOCK_STR   | REG_LOCK          | RFU    |  |

The session register on pages ECh to EDh (Sector 0) via the NFC interface or block FEh via  $I^2C$ , see <u>Table 12</u>, are used to configure or monitor the values of the current communication session. Those bits are read only via the NFC interface but may be read and written via the  $I^2C$  interface.

For backward compatibility reasons the session registers are mirrored to Sector 3 (page F8h and F9h via the NFC interface).

Table 12. Session registers NTAG I<sup>2</sup>C plus

| NFC<br>address<br>(Sector 0) |     | I <sup>2</sup> C Address |     | Byte number |                 |                   |        |  |  |  |

|------------------------------|-----|--------------------------|-----|-------------|-----------------|-------------------|--------|--|--|--|

| Dec                          | Hex | Dec                      | Hex | 0           | 1               | 2                 | 3      |  |  |  |

| 236                          | ECh | 254                      | FEh | NC_REG      | LAST_NDEF_BLOCK | SRAM_MIRROR_BLOCK | WDT_LS |  |  |  |

| 237                          | EDh |                          |     | WDT_MS      | I2C_CLOCK_STR   | NS_REG            | RFU    |  |  |  |

Both, the session and the configuration registers have the same configuration options and parameters except the REG\_LOCK bits, which are only available in the configuration register and the NS\_REG bits which are only available in the session register. After POR, the content of the configuration register is loaded into the session register.

The values of both registers can be changed during a communication session. If the desired effect should be visible immediately, but only for the current communication session, the session registers must be used. After POR, the session registers values will again contain the configuration register values as before.

To change the default behavior, changes to the configuration register are needed, but the related effect will only be visible after the next POR.

To make the effect immediately and after next POR visible, changes to configuration and session registers are needed.

All registers and configuration default values, access conditions and descriptions are defined in Table 13 and Table 14.

Reading and writing the session registers via I<sup>2</sup>C can only be done via the READ and WRITE registers operation - see Section 9.8.

Table 13. Configuration bytes

| Bit                            | Field               | Access via NFC | Access<br>via I <sup>2</sup> C | Default values | Description                                                                                                                                                                                                                          |  |  |

|--------------------------------|---------------------|----------------|--------------------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Configuration register: NC_REG |                     |                |                                |                |                                                                                                                                                                                                                                      |  |  |

| 7                              | NFCS_I2C_RST_ON_OFF | R&W            | R&W                            | 0b             | Enables the NFC silence feature and enables soft reset through I <sup>2</sup> C repeated start - see Section 9.3                                                                                                                     |  |  |

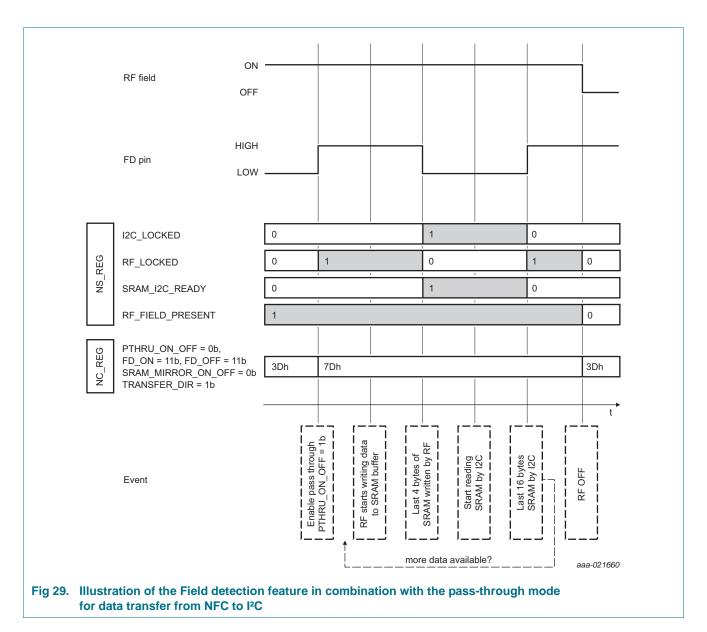

| 6                              | PTHRU_ON_OFF        | R%&W           | R&W                            | 0b             | 1b: pass-through mode using SRAM enabled and SRAM mapped to end of Sector 0. 0b: pass-through mode disabled                                                                                                                          |  |  |

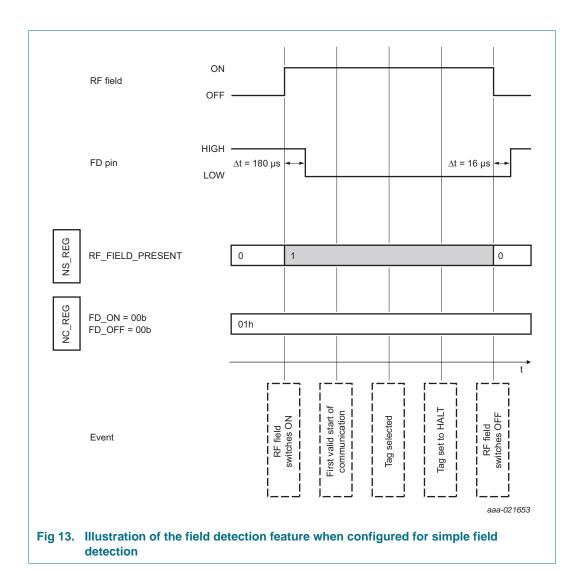

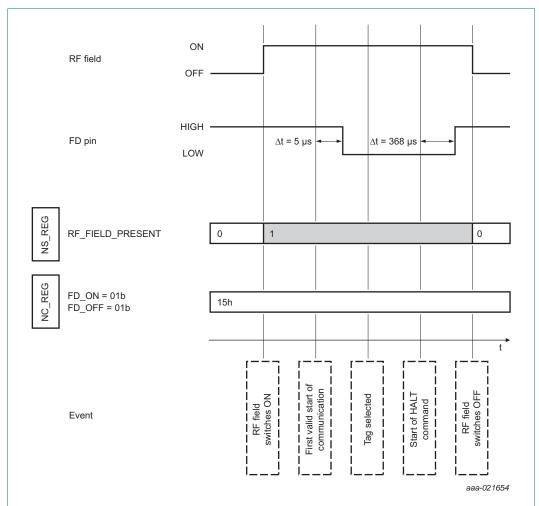

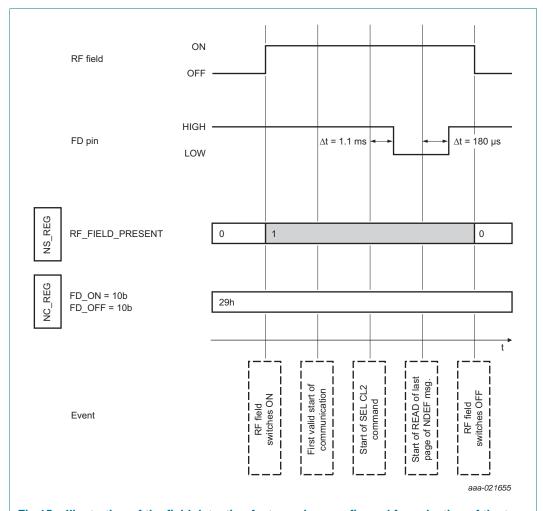

| 5-4                            | FD_OFF              | R&W            | R&W                            | 00b            | defines the event upon which the signal output on the FD pin is pulled up                                                                                                                                                            |  |  |

|                                |                     |                |                                |                | 00b: if the field is switched off                                                                                                                                                                                                    |  |  |

|                                |                     |                |                                |                | 01b: if the field is switched off or the tag is set to the HALT state                                                                                                                                                                |  |  |

|                                |                     |                |                                |                | 10b: if the field is switched off or the last page of the NDEF message has been read (defined in LAST_NDEF_BLOCK)                                                                                                                    |  |  |

|                                |                     |                |                                |                | 11b: (if FD_ON = 11b) if the field is switched off or if last data is read by I <sup>2</sup> C (in pass-through mode NFC> I <sup>2</sup> C) or last data is written by I <sup>2</sup> C (in pass-through mode I <sup>2</sup> C> NFC) |  |  |

|                                |                     |                |                                |                | 11b: (if FD_ON = 00b or 01b or 10b) if the field is switched off                                                                                                                                                                     |  |  |

|                                |                     |                |                                |                | See Section 8.4 for more details                                                                                                                                                                                                     |  |  |

| 3-2                            | FD_ON               | R&W            | R&W                            | 00b            | defines the event upon which the signal output on the FD pin is pulled down                                                                                                                                                          |  |  |

|                                |                     |                |                                |                | 00b: if the field is switched on                                                                                                                                                                                                     |  |  |

|                                |                     |                |                                |                | 01b: by first valid start of communication (SoC)                                                                                                                                                                                     |  |  |

|                                |                     |                |                                |                | 10b: by selection of the tag                                                                                                                                                                                                         |  |  |

|                                |                     |                |                                |                | 11b: (in pass-through mode NFC>l <sup>2</sup> C) if the data is ready to be read from the l <sup>2</sup> C interface                                                                                                                 |  |  |

|                                |                     |                |                                |                | 11b: (in pass-through mode I <sup>2</sup> C> NFC) if the data is read by the NFC interface                                                                                                                                           |  |  |

|                                |                     |                |                                |                | See Section 8.4 for more details                                                                                                                                                                                                     |  |  |

| 1                              | SRAM_MIRROR_ON_OFF  | R&W            | R&W                            | 0b             | 1b: SRAM mirror enabled and mirrored SRAM starts at page SRAM_MIRROR_BLOCK 0b: SRAM mirror disabled                                                                                                                                  |  |  |

| 0                              | TRANSFER_DIR        | R&W            | R&W                            | 1b             | defines the data flow direction for the data transfer                                                                                                                                                                                |  |  |

|                                |                     |                |                                |                | 0b: From I <sup>2</sup> C to NFC interface                                                                                                                                                                                           |  |  |

|                                |                     |                |                                |                | 1b: From NFC to I <sup>2</sup> C interface                                                                                                                                                                                           |  |  |