DISCRETE SEMICONDUCTORS

Product data sheet Supersedes data of 2003 Nov 04 2004 Apr 07

# PEMD6; PUMD6

#### FEATURES

- · Built-in bias resistors

- Simplified circuit design

- Reduction of component count

- Reduced pick and place costs.

#### APPLICATIONS

- Low current peripheral driver

- Replacement of general purpose transistors in digital applications

- Control of IC inputs.

#### DESCRIPTION

NPN/PNP resistor-equipped transistors (see "\_Data\_Sheet\_Remark Supersedes data of 2003 Nov 04" for package details).

#### QUICK REFERENCE DATA

| SYMBOL           | PARAMETER                    | TYP. | MAX. | UNIT |

|------------------|------------------------------|------|------|------|

| V <sub>CEO</sub> | collector-emitter<br>voltage | _    | 50   | V    |

| l <sub>o</sub>   | output current (DC)          | -    | 100  | mA   |

| TR1              | NPN                          | -    | -    | _    |

| TR2              | PNP                          | -    | -    | -    |

| R1               | bias resistor                | 4.7  | -    | kΩ   |

| R2               | open                         | -    | -    | _    |

#### **PRODUCT OVERVIEW**

| TYPE NUMBER | PACKAGE |       | MARKING CODE       | NPN/NPN    | PNP/PNP    |  |

|-------------|---------|-------|--------------------|------------|------------|--|

|             | PHILIPS | EIAJ  | MARKING CODE       | COMPLEMENT | COMPLEMENT |  |

| PEMD6       | SOT666  | _     | D6                 | PEMH7      | PEMB3      |  |

| PUMD6       | SOT363  | SC-88 | D*6 <sup>(1)</sup> | PUMH7      | PUMB3      |  |

#### Note

1. \* = p: Made in Hong Kong.

\* = t: Made in Malaysia.

#### SIMPLIFIED OUTLINE, SYMBOL AND PINNING

|              |                               |     | PINNING       |  |  |

|--------------|-------------------------------|-----|---------------|--|--|

| TYPE NUMBER  | SIMPLIFIED OUTLINE AND SYMBOL | PIN | DESCRIPTION   |  |  |

| PEMD6; PUMD6 |                               | 1   | emitter TR1   |  |  |

|              |                               | 2   | base TR1      |  |  |

|              |                               | 3   | collector TR2 |  |  |

|              |                               | 4   | emitter TR2   |  |  |

|              |                               | 5   | base TR2      |  |  |

|              |                               | 6   | collector TR1 |  |  |

|              | 1 2 3<br>Тор view             |     |               |  |  |

|              |                               |     |               |  |  |

#### Product data sheet

# NPN/PNP resistor-equipped transistors; R1 = 4.7 k $\Omega$ , R2 = open

# PEMD6; PUMD6

#### **ORDERING INFORMATION**

| TYPE        |                                                                          | PACKAGE     |         |  |  |

|-------------|--------------------------------------------------------------------------|-------------|---------|--|--|

| NUMBER NAME |                                                                          | DESCRIPTION | VERSION |  |  |

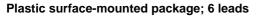

| PEMD6       | <ul> <li>plastic surface mounted package; 6 leads</li> </ul>             |             | SOT666  |  |  |

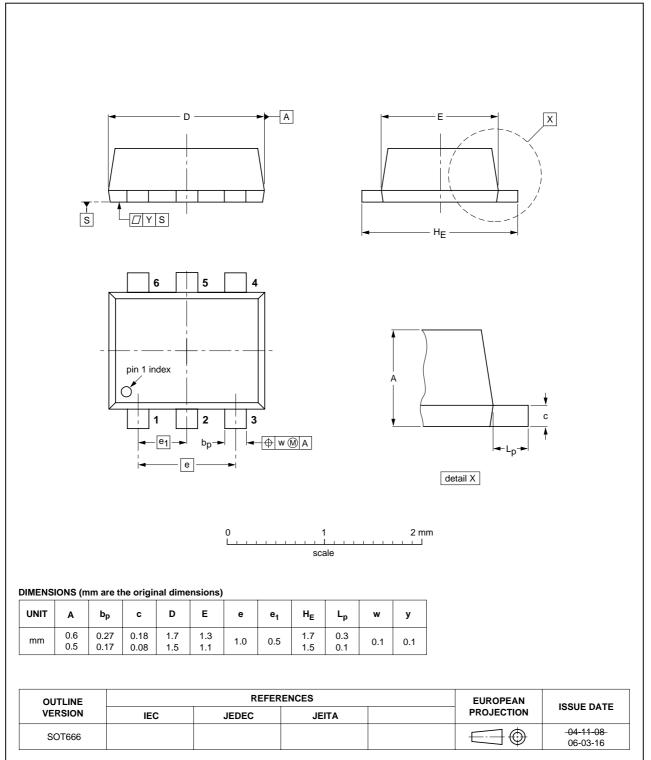

| PUMD6       | <ul> <li>plastic surface mounted package; 6 leads</li> <li>SO</li> </ul> |             | SOT363  |  |  |

#### LIMITING VALUES

In accordance with the Absolute Maximum Rating System (IEC 60134).

| SYMBOL           | PARAMETER                                                     | CONDITIONS                            | MIN. | MAX. | UNIT |  |  |  |

|------------------|---------------------------------------------------------------|---------------------------------------|------|------|------|--|--|--|

| Per transistor;  | Per transistor; for the PNP transistor with negative polarity |                                       |      |      |      |  |  |  |

| V <sub>CBO</sub> | collector-base voltage                                        | open emitter                          | -    | 50   | V    |  |  |  |

| V <sub>CEO</sub> | collector-emitter voltage                                     | open base                             | -    | 50   | V    |  |  |  |

| V <sub>EBO</sub> | emitter-base voltage                                          | open collector                        | -    | 5    | V    |  |  |  |

| I <sub>O</sub>   | output current (DC)                                           |                                       | -    | 100  | mA   |  |  |  |

| I <sub>CM</sub>  | peak collector current                                        |                                       | _    | 100  | mA   |  |  |  |

| P <sub>tot</sub> | total power dissipation                                       | $T_{amb} \le 25 \ ^{\circ}C$ ; note 1 |      |      |      |  |  |  |

|                  | SOT363                                                        | note 1                                | -    | 200  | mW   |  |  |  |

|                  | SOT666                                                        | notes 1 and 2                         | -    | 200  | mW   |  |  |  |

| T <sub>stg</sub> | storage temperature                                           |                                       | -65  | +150 | °C   |  |  |  |

| Tj               | junction temperature                                          |                                       | _    | 150  | °C   |  |  |  |

| T <sub>amb</sub> | operating ambient temperature                                 |                                       | -65  | +150 | °C   |  |  |  |

| Per device       | ·                                                             |                                       |      |      |      |  |  |  |

| P <sub>tot</sub> | total power dissipation                                       | $T_{amb} \le 25 \ ^{\circ}C$ ; note 1 |      |      |      |  |  |  |

|                  | SOT363                                                        | note 1                                | -    | 300  | mW   |  |  |  |

|                  | SOT666                                                        | notes 1 and 2                         | -    | 300  | mW   |  |  |  |

#### Notes

- 1. Transistor mounted on an FR4 printed-circuit board, single-sided copper, standard footprint.

- 2. Reflow soldering is the only recommended soldering method.

# PEMD6; PUMD6

#### THERMAL CHARACTERISTICS

| SYMBOL               | PARAMETER                                   | CONDITIONS | VALUE | UNIT |

|----------------------|---------------------------------------------|------------|-------|------|

| Per transi           | stor                                        | ·          | · · · |      |

| R <sub>th(j-a)</sub> | thermal resistance from junction to ambient | note 1     |       |      |

|                      | SOT363                                      |            | 625   | K/W  |

|                      | SOT666                                      |            | 625   | K/W  |

| Per device           | 9                                           |            |       |      |

| R <sub>th(j-a)</sub> | thermal resistance from junction to ambient | note 1     |       |      |

|                      | SOT363                                      |            | 416   | K/W  |

|                      | SOT666                                      |            | 416   | K/W  |

#### Note

1. Transistor mounted on an FR4 printed-circuit board, single-sided copper, standard footprint.

#### CHARACTERISTICS

$T_{amb}$  = 25 °C; unless otherwise specified.

| SYMBOL             | PARAMETER                                                     | CONDITIONS                                                                       | MIN. | TYP. | MAX. | UNIT |  |  |

|--------------------|---------------------------------------------------------------|----------------------------------------------------------------------------------|------|------|------|------|--|--|

| Per transis        | Per transistor; for the PNP transistor with negative polarity |                                                                                  |      |      |      |      |  |  |

| I <sub>CBO</sub>   | collector-base cut-off current                                | $V_{CB} = 50 \text{ V}; \text{ I}_{E} = 0$                                       | _    | _    | 100  | nA   |  |  |

| I <sub>CEO</sub>   | collector-emitter cut-off current                             | V <sub>CE</sub> = 30 V; I <sub>B</sub> = 0                                       | -    | -    | 1    | μA   |  |  |

|                    |                                                               | $V_{CE} = 30 \text{ V}; \text{ I}_{B} = 0; \text{ T}_{j} = 150 ^{\circ}\text{C}$ | -    | -    | 50   | μA   |  |  |

| I <sub>EBO</sub>   | emitter-base cut-off current                                  | $V_{EB} = 5 V; I_{C} = 0$                                                        | -    | -    | 100  | nA   |  |  |

| h <sub>FE</sub>    | DC current gain                                               | $V_{CE} = 5 \text{ V}; \text{ I}_{C} = 1 \text{ mA}$                             | 200  | -    | _    |      |  |  |

| V <sub>CEsat</sub> | collector-emitter saturation voltage                          | $I_{C} = 5 \text{ mA}; I_{B} = 0.25 \text{ mA}$                                  | -    | -    | 100  | mV   |  |  |

| R1                 | input resistor                                                |                                                                                  | 3.3  | 4.7  | 6.1  | kΩ   |  |  |

| C <sub>c</sub>     | collector capacitance                                         | $I_E = I_e = 0; V_{CB} = 10 V; f = 1 MHz$                                        |      |      |      |      |  |  |

|                    | TR1 (NPN)                                                     |                                                                                  | -    | _    | 2.5  | pF   |  |  |

|                    | TR2 (PNP)                                                     |                                                                                  | -    | -    | 3    | pF   |  |  |

#### PACKAGE OUTLINES

SOT666

# PEMD6; PUMD6

# PEMD6; PUMD6

### PEMD6; PUMD6

#### DATA SHEET STATUS

| DOCUMENT<br>STATUS <sup>(1)</sup> | PRODUCT<br>STATUS <sup>(2)</sup> | DEFINITION                                                                            |

|-----------------------------------|----------------------------------|---------------------------------------------------------------------------------------|

| Objective data sheet              | Development                      | This document contains data from the objective specification for product development. |

| Preliminary data sheet            | Qualification                    | This document contains data from the preliminary specification.                       |

| Product data sheet                | Production                       | This document contains the product specification.                                     |

#### Notes

- 1. Please consult the most recently issued document before initiating or completing a design.

- The product status of device(s) described in this document may have changed since this document was published and may differ in case of multiple devices. The latest product status information is available on the Internet at URL http://www.nxp.com.

#### DISCLAIMERS

**General** — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information.

**Right to make changes** — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

**Suitability for use** — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in medical, military, aircraft, space or life support equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors accepts no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

**Limiting values** — Stress above one or more limiting values (as defined in the Absolute Maximum Ratings System of IEC 60134) may cause permanent damage to the device. Limiting values are stress ratings only and operation of the device at these or any other conditions

above those given in the Characteristics sections of this document is not implied. Exposure to limiting values for extended periods may affect device reliability.

**Terms and conditions of sale** — NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at http://www.nxp.com/profile/terms, including those pertaining to warranty, intellectual property rights infringement and limitation of liability, unless explicitly otherwise agreed to in writing by NXP Semiconductors. In case of any inconsistency or conflict between information in this document and such terms and conditions, the latter will prevail.

**No offer to sell or license** — Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from national authorities.

**Quick reference data** — The Quick reference data is an extract of the product data given in the Limiting values and Characteristics sections of this document, and as such is not complete, exhaustive or legally binding.

# **NXP Semiconductors**

#### **Customer notification**

This data sheet was changed to reflect the new company name NXP Semiconductors, including new legal definitions and disclaimers. No changes were made to the technical content, except for package outline drawings which were updated to the latest version.

#### **Contact information**

For additional information please visit: http://www.nxp.com For sales offices addresses send e-mail to: salesaddresses@nxp.com

© NXP B.V. 2009

All rights are reserved. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner.

The information presented in this document does not form part of any quotation or contract, is believed to be accurate and reliable and may be changed without notice. No liability will be accepted by the publisher for any consequence of its use. Publication thereof does not convey nor imply any license under patent- or other industrial or intellectual property rights.

Printed in The Netherlands

R75/04/pp8

Date of release: 2004 Apr 07

Document order number: 9397 750 13085

# **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

NXP:

PEMD6,115 PUMD6,115 PUMD6,125 PUMD6,135 PUMD6/ZLX PUMD6/ZLF