# TM PFC with X-cap discharge and LLC resonant combo controller

Datasheet - production data

# **Applications**

- · Ac-dc adapter, open frame SMPS

- SMPS for LED TV, desktop and all-in-one PC

- Consumer and industrial SMPS compliant with "Energy Using Product" directive (EuP) Lot 6, DOE and European CoC ver. 5, Tier 2

- · LED street lighting

#### **Features**

- Common features

- SO20W package

- 800 V high voltage start-up with integrated input voltage sensing

- Active input filter capacitor discharge circuitry for reduced standby power compliant with IEC 62368-1

- Independent debug mode for both converters

- PFC controller features

- Enhanced constant on-time PFC with input voltage feedforward, THD optimizer

- Complete set of protections: ac brownin/out, inrush control, OVP, OCP, inductor saturation, feedback disconnection

- · LLC controller features

- Proprietary timeshift control for improved input ripple rejection and dynamic response

- Half-bridge operation up to 750 kHz with self-adjusting deadtime

- Complete set of protections: dc brown-out, two-level OCP, hard switching prevention (HSP) function for anti-capacitive mode protection and safe start-up

- Synchronous burst mode operation with PFC enhances light-load efficiency

Contents STCMB1

# **Contents**

| 1 | Desc  | ription                                                    | 4  |

|---|-------|------------------------------------------------------------|----|

| 2 | Bloc  | k diagrams                                                 | 5  |

| 3 | Pin c | connections and description                                | 6  |

| 4 | Elect | trical ratings                                             | 10 |

| 5 | Ther  | mal data                                                   | 10 |

| 6 | Elect | trical data                                                | 11 |

| 7 | Appl  | ication information                                        | 15 |

|   | 7.1   | HV start-up                                                | 15 |

|   | 7.2   | X-cap discharge                                            | 15 |

|   | 7.3   | Ac brown-out protection                                    | 16 |

|   | 7.4   | VCC pin                                                    | 17 |

|   | 7.5   | PFC section                                                | 17 |

|   | 7.6   | PFC: enhanced constant on-time control with THD optimizer  | 18 |

|   | 7.7   | PFC: error amplifier, regulation loop and V <sub>FF</sub>  | 21 |

|   | 7.8   | PFC: C <sub>TON</sub> calculation                          |    |

|   | 7.9   | PFC: light-load operation                                  | 23 |

|   | 7.10  | PFC: inductor current sensing on ground return and PFC OCP | 23 |

|   | 7.11  | PFC: zero-current detector                                 | 24 |

|   | 7.12  | Starter                                                    | 24 |

|   | 7.13  | PFC: Dynamic OVP and feedback failure protection (latched) | 25 |

|   | 7.14  | PFC gate driver                                            | 26 |

|   | 7.15  | Resonant HB section                                        | 26 |

|   | 7.16  | Dc brown-out function (HB enable and disable)              | 27 |

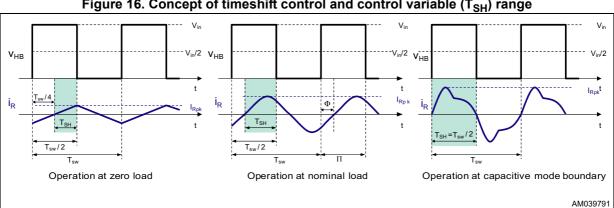

|   | 7.17  | HB: timeshift control basic concept                        | 28 |

|   | 7.18  | HB: oscillator                                             | 30 |

|   | 7.19  | HB: improved burst mode operation at light-load            | 32 |

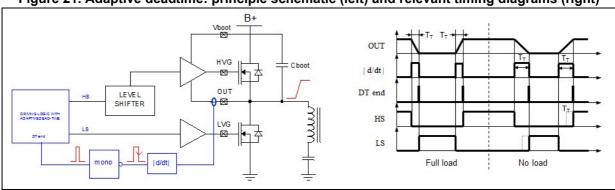

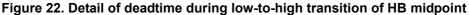

|   | 7.20  | HB: adaptive deadtime (ADT)                                | 33 |

|   |       |                                                            |    |

|    | 7.21  | HB: hard switching prevention (HSP) and anti-capacitive mode protection (ACP) | 36 |

|----|-------|-------------------------------------------------------------------------------|----|

|    | 7.22  | HB: Smooth start-up function                                                  | 37 |

|    | 7.23  | HB: OCP management with internal digital delay and restart                    | 39 |

|    |       | 7.23.1 First OCP protection                                                   | 40 |

|    |       | 7.23.2 Second level OCP protection                                            | 41 |

|    | 7.24  | HB: high voltage bootstrap section and HB gate drivers (HVG and LVG)          | 42 |

| 8  | Debu  | g modes                                                                       | 44 |

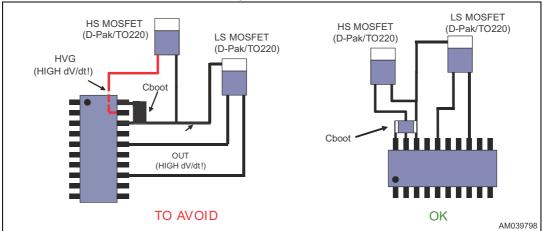

| 9  | STCN  | /IB1 layout hints                                                             | 44 |

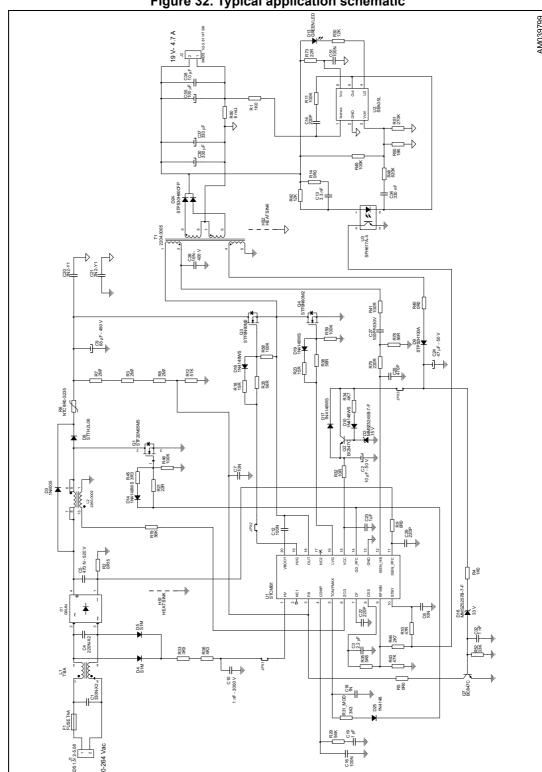

| 10 | Typic | al application schematic                                                      | 48 |

| 11 | Refer | ence                                                                          | 49 |

| 12 | Pack  | age information                                                               | 49 |

|    | 12.1  | SO20W package information                                                     | 49 |

| 13 | Revis | sion history                                                                  | 50 |

Contents

Description STCMB1

# 1 Description

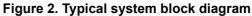

The STCMB1 device embodies a transition mode (TM) PFC, a high voltage double-ended controller for LLC resonant half-bridge, an 800 V-rated high voltage section and the glue logic that supervises the operation of these three blocks.

The PFC section uses a proprietary constant on-time control methodology that does not require a sinusoidal input reference, thereby reducing the system cost and external component count.

It includes also a complete set of protections: a cycle-by-cycle overcurrent (OCP), an output overvoltage (OVP), a feedback failure (FFP, latch-mode), an ac brown-out, boost inductor saturation and inrush current detection both at the start-up and after mains sags or missing cycles.

The half-bridge (HB) section provides two complementary outputs that drive the high-side and low-side MOSFET 180° out-of-phase. The deadtime inserted between the turn-off of an either switch and the turn-on of the other is automatically adjusted to ensure zero voltage switching and higher efficiency from low to full load.

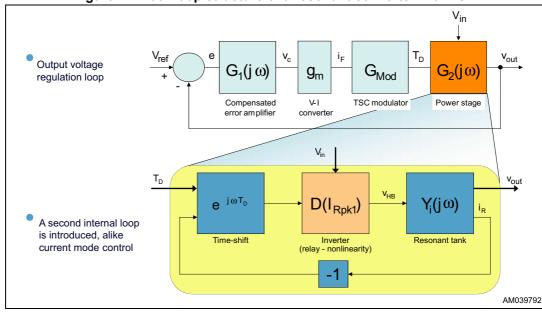

A proprietary control method, timeshift control - TSC, improves dynamic behavior and input ripple rejection resulting in a cleaner output voltage.

At the light-load the IC can be forced to enter a controlled burst mode operation where both the HB and the PFC work intermittently synchronized one to another. This helps to reduce the average switching frequency, thus keeping converter input consumption as low as possible.

At the start-up, in addition to the traditional soft-start based on the frequency-shift, a proprietary hard switching prevention (HSP) function controls the half-bridge to prevent hard switching in the initial cycles. Additionally, the HSP function prevents the converter from working in or too close to the capacitive mode to ensure soft-switching.

The HB is provided with a two-level OCP. The first level is with the frequency shift and delayed shutdown with an automatic restart. A fast shutdown with an automatic restart occurs if this first-level protection cannot limit the primary current. Finally, the device embeds the logic circuitry to coordinate the operation of the PFC, HB and HV start-up generator; in particular: the power-on/off sequencing, X-capacitor discharge, fault handling and synchronous burst mode operation. For the application debug purposes it is possible to externally disable one section at a time and have the other section working standalone.

STCMB1 Block diagrams

# 2 Block diagrams

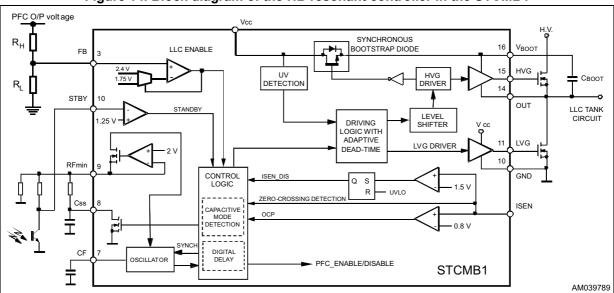

HV 中 HV start-up UVLO and bias U vcc and management X-CAP discharge GD\_PFC UBOOT Digital High-voltage ISEN PFC ⊢HVG Enhanced control unit resonant HB constant-ON- time TON/FX OUT controller with TM PFC controller LVG ZCD time-shift control COMP ☐ ISEN\_HB

Figure 1. STCMB1 block diagram

GND

STBY CF

CSS RFMIN

AM039782

FΒ

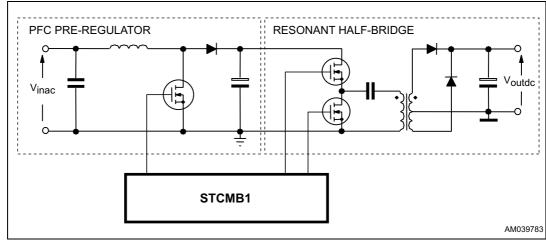

# 3 Pin connections and description

Figure 3. Pin connections, top view

Table 1. Pin description

| Pin<br>no. | Name | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | HV   | High voltage start-up generator / ac voltage sensing input. The pin, able to withstand 800 V, has to be connected to the ac side of the input bridge via a pair of diodes (1N400x type) to sense the ac input voltage.  If the voltage on the pin is higher than 20 V (typical value), an internal pull-up circuit charges the capacitor connected between the pin VCC and GND. Initially the current is low for safety in case of a shorted VCC, and then it goes to the normal level as far as the VCC pin reaches the start-up threshold. To reduce the hold-up requirement on the VCC cap, the generator is turned off when the half-bridge section starts up. In case of a fault that prevents the half-bridge from starting up, the HV generator is shut down after a timeout of 80 ms.  The generator is re-enabled when the voltage on the VCC pin falls below the UVLO threshold. In case of a latched shutdown, when the VCC cycles between the start-up threshold and the UVLO threshold, the current is reduced to keep power dissipation low. The same occurs in case of a restart after a fault to create a longer restart delay.  The pin is used also to sense the ac voltage, which is used by the input voltage feedforward and the ac brown-out functions. When a brown-out condition is detected any latched protection converging on the FB pin is cleared.  An internal logic circuit detects that the unit has been detached from the power line and activates the high voltage start-up generator to discharge the X-capacitors of the EMI filter to a safe level. This allows the unit to meet safety regulations (such as IEC 61010-1 or IEC 62368-1) without using the traditional discharge resistor in parallel to the X-capacitor, thus saving the associated power losses and enabling ultra-low consumption in standby conditions. |

| 2,<br>17   | N.C. | High voltage spacer. These pins are not internally connected to isolate the high voltage sections and ease compliance with safety regulations (creepage distance) on the PCB.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

6/51 DocID028958 Rev 2

Table 1. Pin description (continued)

|            | Table 1. Pin description (continued) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

|------------|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Pin<br>no. | Name                                 | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

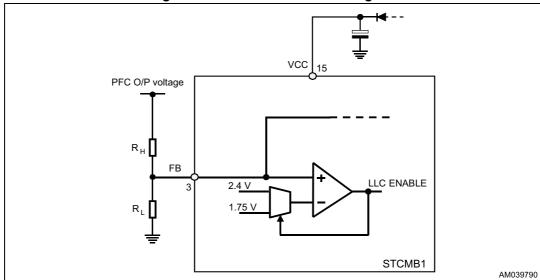

| 3          | FB                                   | Being the pin uncommitted, its voltage is proportional to the instantaneous output voltage of the PFC stage. Under steady state conditions the voltage on the pin sits at the internal reference of the error amplifier (2.5 V). If the voltage exceeds the steady state value by 7% (e.g.: due to an output voltage overshoot) switching is stopped until it gets back close to it. If the FB voltage falls below 0.5 V, a failure of the output divider is assumed and both the PFC stage and the half-bridge are latched off. The HV start-up generator is intermittently turned on to keep the device supplied. To restart the device it is necessary to disconnect the unit from the input source.  As the input voltage monitor for the half-bridge, the pin handles power-on and power-off sequencing. As the device is turned on, the PFC stage starts first and the half-bridge is kept disabled until the FB voltage exceeds 2.4 V. In case the voltage is already above 2.4 V as the PFC starts, the half-bridge waits 0.2 ms before starting, so to have always consistent power-on sequencing. The half-bridge is again inhibited as the voltage on the pin falls below 1.75 V (dc brown-out). |  |  |

| 4          | COMP                                 | To avoid an uncontrolled rise of the output voltage at the zero load, when the voltage on the pin falls below 1 V (typical value) the gate driver output will be inhibited (burst mode operation).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

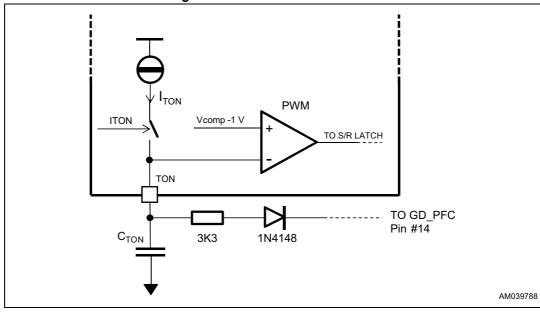

| 5          | TON                                  | Maximum on-time of the PFC MOSFET. A resistor and a capacitor in parallel are connected from this pin to ground. When the MOSFET of the PFC stage is ON an internal current generator produces a ramp that, along with the voltage on the pin COMP, determines the turn-off instant of the MOSFET.  A 3.3 k $\Omega$ (1/8 W) resistor and a small signal diode (e.g.: 1N4148 or similar) in series have to connect the Ton pin to the GD_PFC pin (#14). Details are displayed in <i>Figure 11 on page 22</i> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| 6          | ZCD                                  | Boost inductor's demagnetization sensing input. A negative-going edge triggers the PFC MOSFET's turn-on. The pin can be connected to an auxiliary winding of the boost inductor through a resistor or to the drain of the MOSFET via an RC series.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

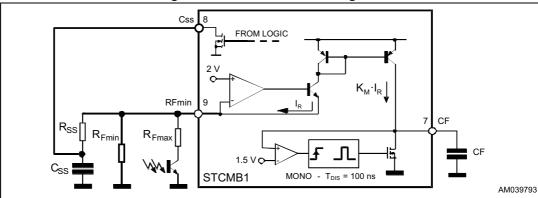

| 7          | CF                                   | Timing capacitor for HB oscillator. A capacitor connected from this pin to GND is charged by an internal current generator programmed by the external network connected to the pin RFMIN. In each half cycle the ramp starts as the tank current (sensed through the pin ISEN_HB) and the applied square wave voltage has the same sign (e.g.: ISEN_HB positive during the high-side MOSFET on-time and ISEN_HB negative during low-side MOSFET on-time). The ramp is reset as a fixed peak value is reached. This also causes the HB to be toggled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| 8          | CSS                                  | HB soft start. This pin connects an external capacitor to GND and a resistor to the pin RFMIN that set both the initial oscillator frequency and the time constant for the frequency shift that occurs as the chip starts up (soft-start). An internal switch discharges this capacitor every time the chip turns off (VCC < UVLO, FB < 1.75 V, ISEN_HB > 1.5 V) to make sure it will be soft-started next. Additionally the switch is activated when the voltage on the current sense pin (ISEN) exceeds 0.8 V or when the converter is working in the capacitive mode operation. As long as the voltage on the pin is lower than 0.3 V, the burst mode operation and second level OCP protection are inhibited.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| 9          | RFMIN                                | Timeshift setting. This pin provides an accurate 2 V reference, and a resistor connected from this pin to GND defines a current that is used to set the maximum timeshift. To close the feedback loop that regulates the converter output voltage by modulating the timeshift, the phototransistor of an optocoupler will be connected to this pin through a resistor. The value of this resistor will set the minimum timeshift. An R-C series connected from this pin to GND sets the timeshift at the start-up to prevent an excessive energy inrush (soft-start).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

Table 1. Pin description (continued)

| Table 1. Pin description (continued) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Name                                 | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| STBY                                 | Burst mode operation threshold for the HB. The pin senses some voltage related to the feedback control, which is compared to an internal reference (1.25 V). If the voltage on the pin is lower than the reference, the IC stops switching, enters an idle state and its quiescent current is reduced. The chip restarts switching as the voltage exceeds the reference by 40 mV. Soft-start is not invoked. When the HB is stopped the PFC is stopped as well; while the HB is switching the PFC stage is enabled and it switches or not depending on the level of the pin COMP.  Tie the pin to RFMIN if the burst mode operation is not used.                                                                                                                                                                                                                                                                          |  |  |  |

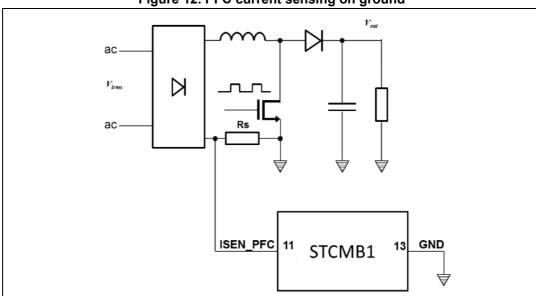

|                                      | The inductor current is sensed through a resistor RS on the current return side and the resulting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|                                      | negative voltage is applied to this pin through a limiting resistor.  When the power MOSFET is turned on an internal comparator enables the PWM ramp to start only when the voltage on the pin is lower than -35 mV (typical value), e.g.: when the inductor current is slightly positive.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| ISEN_PFC                             | If the voltage on the pin goes below -0.5 V the internal overcurrent comparator is triggered and terminates the conduction cycle of the external power MOSFET before the normal PWM circuit does. In this way, the peak inductor current is limited at a maximum of 0.5/RS.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

|                                      | A voltage on this pin higher than -35 mV (typical value) enables both power MOSFET's turn-on when a cycle is initiated by the demagnetization sensing circuit and when it is initiated by the internal starter. In this way, the unit stops during the current surges occurring at power up or after a mains dip or a missing cycle and restarts switching only when the surge is over.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| ISEN_HB                              | Current sense input for the HB. The pin senses the resonant current through a sense resistor or a capacitive divider for lossless sensing. If the voltage exceeds a 0.8 V threshold the soft-start capacitor connected to the pin CSS is internally discharged: the frequency increases hence limiting the power throughput. Under the output short-circuit, this normally results in a nearly constant peak primary current. This condition is allowed for a maximum time internally set at 40 ms minimum. If the current keeps on building up despite this frequency increase, a second comparator referenced to 1.5 V disables switching immediately. In both cases VCC is recycled before restarting (see the pin HV). As long as the voltage on the CSS pin is lower than 0.3 V, this second comparator is inhibited.  The pin is used also by the hard switching prevention (HSP) function. Do not short the pin to |  |  |  |

|                                      | ground; this would prevent the device from operating correctly.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

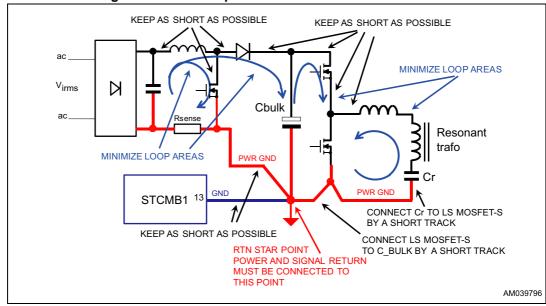

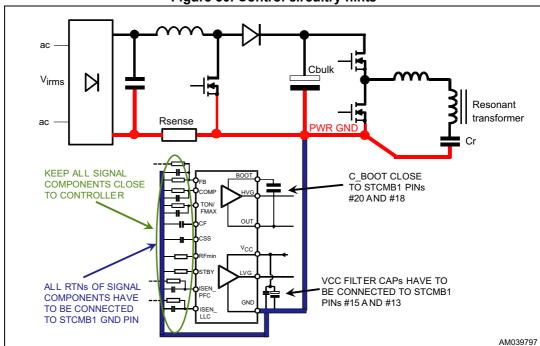

| GND                                  | Ground. Current return for signal parts of the IC, the PFC gate driver and the low-side gate driver of the half-bridge. Keep the PCB trace that goes from this pin to the sources of the PFC and the low-side MOSFETs separate from the trace that collects the grounding of the bias components.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| GD_PFC                               | PFC gate driver output. The totem pole output stage is able to drive power MOSFETs and IGBTs. It is capable of a 0.6 A source current and a 0.8 A sink current (minimum values). The pin is actively pulled to GND during UVLO.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| VCC                                  | Supply voltage of the signal part of the IC. An electrolytic capacitor of at least 22 $\mu$ F (typ. value) must be connected between the pin and GND. Sometimes a small bypass capacitor (0.1 $\mu$ F typ.) in parallel to the ELCAP might be useful to get a clean bias voltage for the signal part of the IC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| LVG                                  | Low-side gate drive output. The driver is capable of a 0.3 A source and a 0.8 A sink peak current (minimum values) to drive the lower MOSFET of the half-bridge leg. The pin is actively pulled to GND during UVLO.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| OUT                                  | High-side gate drive floating ground. Current return for the high-side gate drive current. Layout carefully the connection of this pin to avoid too large spikes below ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

|                                      | STBY  ISEN_PFC  GND  GD_PFC  VCC  LVG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

8/51 DocID028958 Rev 2

Table 1. Pin description (continued)

| Pin<br>no. | Name | Function                                                                                                                                                                                                                                                                    |

|------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 19         | HVG  | High-side gate drive output. The driver is capable of a 0.3 A source and a 0.8 A sink peak current (minimum values) to drive the upper MOSFET of the half-bridge leg. A resistor internally connected to OUT ensures that the pin is not floating during UVLO.              |

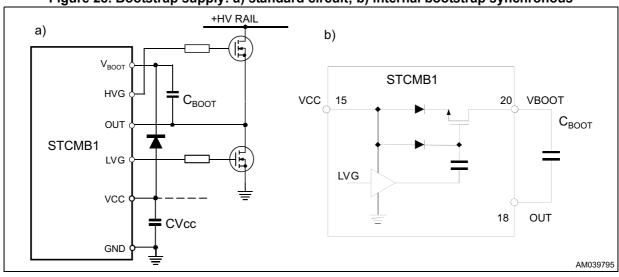

| 20         | воот | High-side gate drive floating supply voltage. The bootstrap capacitor connected between this pin and OUT is fed by an internal synchronous bootstrap diode driven in phase with the low-side gate drive. This patented structure replaces the normally used external diode. |

Electrical ratings STCMB1

# 4 Electrical ratings

Table 2. Absolute maximum ratings

| Symbol                 | Pin no.           | Parameter                                 | Value                                              | Unit |

|------------------------|-------------------|-------------------------------------------|----------------------------------------------------|------|

| V <sub>HV</sub>        | 1                 | Voltage range (referred to GND)           | -1 to 800                                          | V    |

| -                      | 3, 5, 7, 8, 9, 10 | Analog inputs and outputs voltage range   | -0.3 to 3.6                                        | V    |

| -                      | 4, 6              | Analog inputs and outputs voltage range   | -0.3 to 5.5                                        | V    |

| I <sub>ZCD</sub>       | 6                 | Zero current detector input max. current  | 3                                                  | mA   |

| I <sub>RFMIN</sub>     | 9                 | Maximum source current                    | 2                                                  | mA   |

| V <sub>ISEN_PFC</sub>  | 11                | Current sensing inputs voltage range      | -3 to 3.6                                          | V    |

| V <sub>ISEN_HB</sub>   | 12                | Current sensing inputs voltage range      | -3 to 5.5                                          | V    |

| $V_{GD\_PFC}, V_{LVG}$ | 14, 16            | Ground-referenced gate drivers            | -0.3 to V <sub>VCC</sub>                           | V    |

| V <sub>VCC</sub>       | 15                | IC supply voltage                         | -0.3 to 21                                         | V    |

| V <sub>OUT</sub>       | 18                | Floating ground voltage                   | $V_{VBOOT}$ - 21 to $V_{VBOOT}$ + 0.3              | V    |

| d <sub>VOUT</sub> /dt  | 18                | Floating ground max. slew rate            | 50                                                 | V/ns |

| V <sub>HVG</sub>       | 19                | High-side (floating) gate driver          | V <sub>OUT</sub> - 0.3 to V <sub>VBOOT</sub> + 0.3 | V    |

| V <sub>BOOT</sub>      | 20                | Floating supply voltage (referred to GND) | -1 to 620                                          | V    |

# 5 Thermal data

Table 3. Thermal data

| Symbol                | Parameter                                     | Value      | Unit |

|-----------------------|-----------------------------------------------|------------|------|

| R <sub>th j-amb</sub> | Max. thermal resistance, junction to ambient  | 90         | °C/W |

| P <sub>tot</sub>      | Power dissipation at T <sub>amb</sub> = 70 °C | 0.6        | W    |

| T <sub>j</sub>        | Junction temperature operating range          | -40 to 150 | °C   |

| T <sub>stg</sub>      | Storage temperature                           | -55 to 150 | °C   |

STCMB1 Electrical data

# 6 Electrical data

$T_{j}$  = -40 °C to +125 °C,  $V_{VCC}$  =  $V_{VBOOT}$  = 15  $V^{(a)}$ ,  $C_{F}$  = 470 pF;  $R_{RFMIN}$  = 22.5 k $\Omega$ ;  $C_{HVG}$  =  $C_{LVG}$  =  $C_{GD\_PFC}$  = 1 nF,  $C_{TON}$  = 470 pF unless otherwise specified.

**Table 4. Electrical characteristics**

| Symbol                 | Parameter                       | Test condition                                                                  | Min. | Тур. | Max. | Unit |

|------------------------|---------------------------------|---------------------------------------------------------------------------------|------|------|------|------|

| IC supply vo           | Itage                           |                                                                                 |      |      |      |      |

| V <sub>VCC</sub>       | Operating range                 | After turn-on                                                                   | 10   |      | 20   | V    |

| V <sub>VCCOn</sub>     | Turn-on threshold               | <sup>(1)</sup> Voltage rising                                                   | 15.5 | 16.5 | 17.5 | V    |

| V <sub>VCCOff</sub>    | Turn-off threshold              | <sup>(1)</sup> Voltage falling                                                  | 9    | 9.5  | 10   | V    |

| Supply curre           | ent                             |                                                                                 |      |      |      |      |

|                        |                                 | V <sub>FB</sub> = 1 V                                                           |      | 1.5  | 2.2  |      |

|                        |                                 | V <sub>FB</sub> = 2.5 V                                                         |      | 3    | 4    |      |

| Iq                     | Quiescent current after turn-on | Idle during burst mode $T_j = 25 ^{\circ}\text{C}$                              |      | 0.7  | 0.85 | mA   |

|                        |                                 | IC latched off                                                                  |      |      | 1.2  |      |

|                        | Operating supply current        | V <sub>FB</sub> = 1 V, GD_PFC only                                              |      | 2.5  | 3.3  | mA   |

| I <sub>CC</sub>        | at f <sub>sw</sub> = 75 kHz     | V <sub>FB</sub> = 2.5 V, all drivers                                            |      | 4.5  | 6    |      |

| High voltage           | start-up generator              |                                                                                 |      |      |      |      |

| V <sub>HV</sub>        | Breakdown voltage               | I <sub>HV</sub> < 100 μA                                                        | 800  |      |      | V    |

| V <sub>HVstart</sub>   | Start voltage (rising)          | <sup>(1)</sup> I <sub>VCC</sub> < 100 μA                                        | 10   | 18   | 25   | V    |

| V <sub>VCC_SO</sub>    | VCC switchover threshold        |                                                                                 | 1    | 1.5  | 2    | V    |

|                        | ON-state charge current         | V <sub>HV</sub> > V <sub>HVstart</sub> , V <sub>VCC</sub> < V <sub>VCC_SO</sub> | 0.5  | 1    | 1.6  |      |

| I <sub>HV, ON</sub>    |                                 | V <sub>HV</sub> > V <sub>HVstart</sub> , V <sub>VCC</sub> > V <sub>VCC_SO</sub> | 5    | 8    | 11   | mA   |

| TIV, ON                | J                               | IC latched off or restart after overload timeout                                | 3.5  | 4.5  | 5.5  |      |

| I <sub>HV, OFF</sub>   | Off-state leakage current       | V <sub>HV</sub> = 400 V                                                         |      | 20   | 24   | μΑ   |

| T <sub>TOUT</sub>      | Generator shutdown timeout      | After V <sub>VCC</sub> exceeds V <sub>VCCOn</sub>                               | 64   | 80   | 96   | ms   |

| IC debug fun           | ictions                         |                                                                                 | •    | •    | •    | •    |

| V <sub>ZCD_D</sub>     | PFC disable threshold           | At turn-on, voltage rising                                                      |      | 2.4  |      | V    |

| V <sub>ISEN_HB_D</sub> | HB disable threshold            | At turn-on, voltage rising                                                      |      | 2.4  |      | V    |

| X-capacitor of         | discharge function              | •                                                                               |      | •    | •    | •    |

| $V_{HVmin}$            | Peak residual voltage           | I <sub>HV, DIS</sub> > 4.2 mA                                                   |      |      | 45   | V    |

| I <sub>HV, DIS</sub>   | Discharge current               | V <sub>HV</sub> > 45 V                                                          | 4.2  |      |      | mA   |

a. Adjust  $\rm V_{\rm VCC}$  above  $\rm V_{\rm VCCOn}$  before setting at 15 V.

Electrical data STCMB1

Table 4. Electrical characteristics (continued)

| Symbol               | Parameter                     | Test condition                                     | Min.  | Тур.  | Max.  | Unit |

|----------------------|-------------------------------|----------------------------------------------------|-------|-------|-------|------|

| PFC - ac brow        | wn-out protection             | <u> </u>                                           |       | Į.    |       |      |

| V <sub>HVpk_BO</sub> | Brown-out threshold           | (1)Peak voltage falling                            | 92    | 98    | 104   | V    |

| V <sub>HVpk_BI</sub> | Brown-in threshold            | (1)Peak voltage rising                             | 106   | 113   | 120   | V    |

| T <sub>DB</sub>      | Brown-out debounce time       |                                                    | 32    | 40    | 48    | ms   |

| PFC - zero cu        | urrent detector               |                                                    |       |       |       | •    |

| V <sub>ZCDH</sub>    | Upper clamp voltage           | I <sub>ZCD</sub> = 2.5 mA                          | 2.8   | 3.3   |       | V    |

| V <sub>ZCDL</sub>    | Lower clamp voltage           | I <sub>ZCD</sub> = -2.5 mA                         | -0.3  |       | 0     | V    |

| V <sub>ZCDA</sub>    | Arming voltage                | <sup>(1)</sup> Positive-going edge                 |       | 0.5   |       | V    |

| V <sub>ZCDT</sub>    | Triggering voltage            | (1)Negative-going edge                             |       | 0.25  |       | V    |

| I <sub>ZCDb</sub>    | Input bias current            | V <sub>ZCD</sub> = 1 to 2.2 V                      |       |       | 5     | μΑ   |

| PFC - maxim          | um on-time                    |                                                    |       |       | •     | •    |

|                      | Charge current                | V <sub>TON</sub> = 3 V, V <sub>HV_pk</sub> = 160 V | 180   | 200   | 220   |      |

| I <sub>TON</sub>     | Charge current                | V <sub>TON</sub> = 3 V, V <sub>HV_pk</sub> = 320 V | 640   | 800   | 960   | μA   |

| V <sub>TON</sub>     | Linear operating range        |                                                    | 0     |       | 3     | V    |

| V <sub>TON</sub>     | On-time reference level       | GD_PFC goes low<br>V <sub>COMP</sub> = 3 V         |       | 2     |       | ٧    |

| R <sub>DSC</sub>     | Discharge resistance          |                                                    |       | 60    | 200   | Ω    |

| PFC - transco        | onductance error amplifier    |                                                    | •     |       |       |      |

| \/                   | Internal voltage reference    | T <sub>j</sub> = 25 °C                             | 2.475 | 2.5   | 2.525 |      |

| V <sub>ref</sub>     | Internal voltage reference    | <sup>(1)</sup> 10 V < V <sub>VCC</sub> < 21 V      | 2.44  |       | 2.58  | V    |

| I <sub>FB</sub>      | Input bias current            | V <sub>FB</sub> = 0 to 3 V                         | -1    | -0.2  | 1     | μΑ   |

| V <sub>COMPSAT</sub> | Upper clamp voltage           | I <sub>SOURCE</sub> = 20 μA                        | 3.8   | 4.5   |       | V    |

| I <sub>COMP</sub>    | Max. sink/source current      | V <sub>COMP</sub> = 3 V, V <sub>FB</sub> = 2.3 V   | 150   | 200   |       | μΑ   |

| 9 <sub>m</sub>       | Transconductance              | V <sub>FB</sub> = V <sub>ref</sub>                 | 160   | 200   | 240   | μS   |

| Ro                   | Output impedance              |                                                    | 2     |       |       | МΩ   |

| PFC - dynam          | ic and static OVP protections |                                                    | •     |       |       | •    |

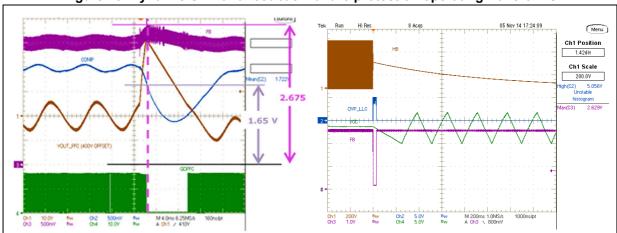

| \/                   | D. OV/D three hold            | T <sub>j</sub> = 25 °C                             | 2.595 | 2.675 | 2.755 | V    |

| V <sub>FB_S</sub>    | D_OVP threshold               | <sup>(1)</sup> 10 V < V <sub>VCC</sub> < 21 V      | 2.568 |       | 2.782 | V    |

| V <sub>FB_R</sub>    | Restart voltage after D_OVP   | (1)                                                | 2.47  | 2.55  | 2.63  | V    |

| T <sub>DB</sub>      | D_OVP debounce time           |                                                    | 40    | 50    | 65    | μs   |

| V <sub>COMP_S</sub>  | S_OVP threshold               | <sup>(1)</sup> Voltage falling                     | 0.9   | 1     | 1.1   | V    |

| V <sub>COMP_R</sub>  | Restart voltage after S_OVP   | (1)Voltage rising                                  | 0.92  | 1.02  | 1.15  | V    |

| PFC - feedba         | ck failure protection (FFP)   | ·                                                  |       |       |       |      |

| V <sub>FB_D</sub>    | Disable threshold             | <sup>(1)</sup> Voltage falling                     | 0.42  | 0.46  | 0.5   | V    |

| T <sub>DB</sub>      | FFP debounce time             |                                                    | 40    | 50    | 65    | μs   |

STCMB1 Electrical data

Table 4. Electrical characteristics (continued)

| Symbol                  | Parameter                                            | Test condition                                        | Min.  | Тур. | Max.  | Unit |

|-------------------------|------------------------------------------------------|-------------------------------------------------------|-------|------|-------|------|

| PFC - current           | sensing comparators                                  | 1                                                     | l     |      |       |      |

| I <sub>ISEN_PFC</sub>   | Input bias current                                   | VISEN_PFC = -0.5 V                                    |       |      | 4.3   | μA   |

| V <sub>ISEN_PFC</sub>   | OCP threshold                                        | (1)VCOMP = upper clamp                                | -0.46 | -0.5 | -0.54 | V    |

| td <sub>(H-L)</sub>     | Delay to output                                      |                                                       |       | 220  | 280   | ns   |

| V <sub>ISEN_PFC_Z</sub> | ZCD anticipation level and THD optimizer threshold   |                                                       |       | -25  |       | mV   |

| PFC - interna           | l start-up timer                                     |                                                       |       |      |       |      |

| t <sub>START_DEL</sub>  | Start-up delay                                       | After V <sub>ISEN_PFC</sub> > V <sub>ISEN_PFC_Z</sub> | 8     | 10   | 13    | μs   |

| PFC - GATE D            | DRIVER                                               |                                                       |       |      |       |      |

| V <sub>OL</sub>         | Output low voltage                                   | I <sub>sink</sub> = 100 mA                            |       | 0.4  | 0.7   | V    |

| V <sub>OH</sub>         | Output high voltage                                  | I <sub>source</sub> = 5 mA                            | 14.7  | 14.9 |       | V    |

| t <sub>f</sub>          | Voltage fall time                                    | From 15 to 1.5 V                                      |       | 30   | 70    | ns   |

| t <sub>r</sub>          | Voltage rise time                                    | From 0 to 10 V                                        |       | 60   | 110   | ns   |

|                         | UVLO saturation                                      | $V_{VCC} = 0$ to $V_{VCCon}$ , $I_{sink} = 1$ mA      |       |      | 1.1   | V    |

| HB - high-sid           | e floating gate drive supply                         | 1                                                     | ı     | I    | l     |      |

| R <sub>DS(on)</sub>     | Synchronous bootstrap diode on-<br>resistance        | V <sub>LVG</sub> = HIGH                               |       | 230  |       | Ω    |

| HB - input vo           | Itage sensing (dc brown-out)                         |                                                       |       |      |       |      |

| V <sub>FB_E</sub>       | Enable voltage                                       | <sup>(1)</sup> Voltage rising                         | 2.34  | 2.4  | 2.49  | V    |

| V <sub>FB_D</sub>       | Disable voltage                                      | (1)Voltage falling                                    | 1.7   | 1.75 | 1.8   | V    |

| HB - oscillato          | r                                                    |                                                       |       |      |       |      |

| \/                      | Dama and                                             | <sup>(1)</sup> V <sub>STBY</sub> > 1.34 V             | 1.44  | 1.5  | 1.56  | V    |

| $V_{CFp}$               | Ramp peak                                            | <sup>(1)</sup> V <sub>STBY</sub> < 1.26 V             | 1.775 | 1.85 | 1.925 |      |

| V <sub>CFv</sub>        | Ramp valley                                          |                                                       | 0     |      | 20    | mV   |

| \/                      | \/altaga_rafaranaa                                   | (1)                                                   | 1.93  | 2    | 2.08  | V    |

| $V_{RFMIN}$             | Voltage reference                                    | <sup>(1)</sup> I <sub>RFMIN</sub> = -2 mA             | 1.93  | 2    | 2.08  |      |

| D                       | Output duty cycle (HVG and LVG) <sup>(2)</sup>       | $V_{STBY} = 2 V$<br>$R_{RFMIN} = 5.15 kΩ$             | 49    | 50   | 51    | %    |

| _                       | T 1:0                                                | R <sub>RFMIN</sub> = 22.5 kΩ                          | 8.5   | 9    | 9.5   | - µs |

| T <sub>SH</sub>         | Time-shift                                           | $R_{RFMIN} = 5.15 \text{ k}\Omega$                    | 2.1   | 2.25 | 2.4   |      |

| f <sub>HB</sub>         | Max. operating frequency                             |                                                       | 500   |      |       | kHz  |

| K <sub>M</sub>          | Mirroring ratio I <sub>CF</sub> / I <sub>RFMIN</sub> |                                                       | 0.97  | 1    | 1.03  |      |

| R <sub>RFMIN</sub>      | Timing resistor range                                |                                                       | 1     |      | 100   | kΩ   |

| HB - adaptive           | deadtime function                                    | •                                                     |       |      |       |      |

| T <sub>D_max</sub>      | Maximum deadtime                                     |                                                       | 0.7   |      |       | μs   |

| T <sub>D_min</sub>      | Minimum deadtime                                     |                                                       |       | 0.22 |       | μs   |

Electrical data STCMB1

Table 4. Electrical characteristics (continued)

| Symbol                   | Parameter                         | Test condition                                                        | Min. | Тур. | Max. | Unit |

|--------------------------|-----------------------------------|-----------------------------------------------------------------------|------|------|------|------|

| HB - zero-cur            | rent comparator                   |                                                                       |      |      |      |      |

| .,                       |                                   | Negative-going edge                                                   |      | -35  |      | .,   |

| V <sub>ISEN_Z</sub>      | Threshold voltage                 | Positive-going edge                                                   |      | 35   |      | mV   |

| HB - overcurr            | ent comparator and overload d     | elays                                                                 |      | ı    | ı    | ı    |

| I <sub>ISEN_HB</sub>     | Input bias current                | V <sub>ISEN HB</sub> = 0 to 1.4 V                                     | -1   |      | 1    | nA   |

| V <sub>ISEN_HB_x</sub>   | Frequency shift threshold         | (1)Voltage rising                                                     | 0.76 | 0.80 | 0.84 | V    |

| V <sub>ISEN_HB_dis</sub> | Immediate stop threshold          | <sup>(1)</sup> Voltage rising                                         | 1.42 | 1.5  | 1.58 | V    |

| T <sub>OVL</sub>         | Minimum overload timeout          | V <sub>ISEN_HB</sub> > V <sub>ISENHB_X</sub>                          | 18   | 22   | 26   | ms   |

| HB - soft-star           | t function                        | <u> </u>                                                              |      | ı    |      |      |

| I <sub>leak</sub>        | Open state current                | V <sub>CSS</sub> = 2 V                                                |      |      | 0.5  | μA   |

| R                        | Discharge resistance              |                                                                       |      | 120  | 220  | Ω    |

| T <sub>DISCH</sub>       | Css discharge duration            | V <sub>ISEN_HB</sub> > V <sub>ISEN_HBx</sub>                          |      | 6    |      | μs   |

| V <sub>thHSP-SS</sub>    | SS discharge enable (HSP)         | <sup>(1)</sup> Voltage rising                                         | 1.77 | 1.85 | 1.94 | V    |

| HB - standby             | function                          |                                                                       |      |      | I    | I    |

| I <sub>STBY</sub>        | Input bias current                | V <sub>STBY</sub> = 1.3 V                                             | -1   |      | 1    | μA   |

| $V_{H}$                  | V <sub>CFp</sub> change threshold | <sup>(1)</sup> Voltage falling                                        | 1.26 | 1.3  | 1.34 | V    |

| $V_{H,Hys}$              | V <sub>H</sub> hysteresis         | Voltage rising                                                        | 30   | 40   | 50   | mV   |

| V <sub>L</sub>           | Disable threshold                 | (1)Voltage falling                                                    | 1.21 | 1.25 | 1.29 | V    |

| $V_{L,Hys}$              | V <sub>L</sub> hysteresis         | Voltage rising                                                        | 30   | 45   | 60   | mV   |

| Low-side gate            | driver (voltages referred to GN   | ID)                                                                   |      | •    |      |      |

| V <sub>OL</sub>          | Output low voltage                | I <sub>sink</sub> = 50 mA                                             |      | 0.5  | 0.9  | V    |

| V <sub>OH</sub>          | Output high voltage               | I <sub>source</sub> = 5 mA                                            | 14.7 | 14.9 |      | V    |

| t <sub>f</sub>           | Voltage fall time                 | From 15 to 1.5 V                                                      |      | 30   | 70   | ns   |

| t <sub>r</sub>           | Voltage rise time                 | From 0 to 10 V                                                        |      | 60   | 110  | ns   |

|                          | UVLO saturation                   | V <sub>VCC</sub> = 0 to V <sub>VCCon</sub> , I <sub>sink</sub> = 1 mA |      | 0.9  | 1.1  | V    |

| High-side gat            | e driver (voltages referred to Ol | UT)                                                                   |      | 1    | l    |      |

| V <sub>OL</sub>          | Output low voltage                | I <sub>sink</sub> = 50 mA                                             |      | 0.5  | 0.9  | V    |

| V <sub>OH</sub>          | Output high voltage               | V <sub>BOOT</sub> = V <sub>CC</sub> V, I <sub>source</sub> = 5 mA     | 14.7 | 14.9 |      | V    |

| t <sub>f</sub>           | Voltage fall time                 | From 15 to 1.5 V                                                      |      | 30   | 70   | ns   |

| t <sub>r</sub>           | Voltage rise time                 | From 0 to 10 V                                                        |      | 60   | 110  | ns   |

|                          | HVG-OUT pull-down                 |                                                                       | 22   | 27   | 36   | kΩ   |

<sup>1.</sup> Parameters tracking each other.

<sup>2.</sup>  $D_{HVG} + D_{LVG} = 100\%$ .

# 7 Application information

### 7.1 HV start-up

The STCMB1 is equipped with internal HV start-up circuitry dedicated to supply the IC during the initial start-up phase, before the self-supply winding is operating. An external electrolytic capacitor connected to the VCC pin is charged by the HV start-up circuitry, connected to the HV pin.

As soon as the voltage on the HV pin is higher than  $V_{HVstart}$  (20 V typ.), the HV start-up system turns on and the external  $V_{CC}$  capacitor is charged up to the turn-on threshold ( $V_{CCOn}$ , 16.5 V typ.), then to guarantee a reliable start-up of the STCMB1, the HV start-up system is turned off only after the half-bridge section starts up. In case of a fault that prevents the half-bridge section from starting up, the HV start-up system is automatically shut down after a timeout  $T_{TOUT} = 80$  ms.

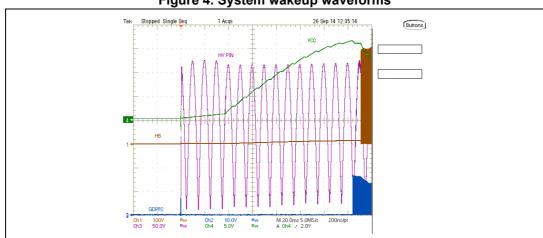

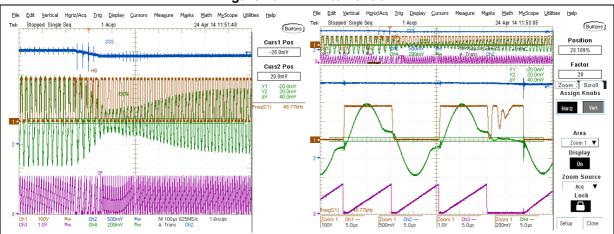

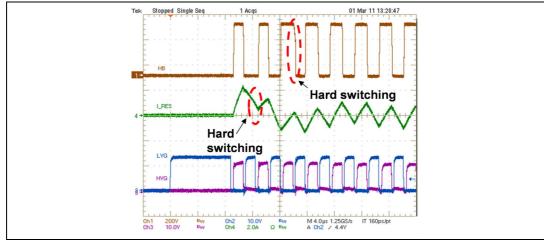

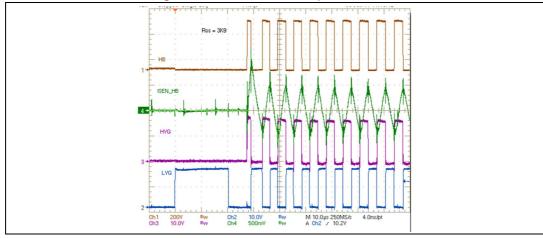

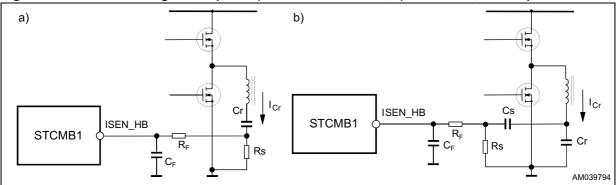

Figure 4. System wakeup waveforms

If for any reason the self-supply circuitry cannot power the STCMB1 the HV start-up will be reactivated once the  $V_{CC}$  reaches the turn-off threshold ( $V_{VCCOff}$ , 9.5 V typ.).

The HV start-up system performs an R-C charge of the VCC pin. A double time constant depending on the voltage value on the VCC pin is implemented to prevent damaging in case of shorts to GND of the  $V_{\rm CC}$  circuitry.

The HV startup generator is activated also after detection of the PFC feedback failure, ac brown-out or X-cap discharge condition. Different values of the charging current (IHV,ON) are supplied to the VCC pin according to the state, see *Table 4: Electrical characteristics on page 11*.

# 7.2 X-cap discharge

The compliance of consumer equipment with the safety regulation such as IEC 61010-1, IEC 62368-1, and others, requires that, when the converter mains connector is removed from the plug, the EMI filter capacitors connected across the line between the phase and the neutral wires (the so called X-caps) have to be discharged bringing their voltage at a safe level to avoid the user any risk of the electrical shock due to the energy stored in the

capacitors. This requirement is mandatory in case the total capacitance before the input bridge exceeds 100 nF.

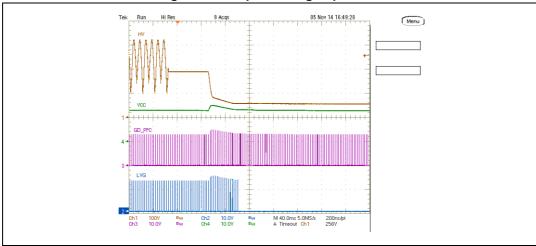

Figure 5. X-cap discharge operation

Typically this function is performed by means of a resistor in parallel but this method cannot be applied in case the converter requires very low power consumption during the light-load or no load operation, because the losses of the X-cap discharging resistor would be too high.

To overcome this issue, enabling the user to design a high performance power supply the STCMB1 device does this operation by means of the HV start-up system, allowing the removal of the traditional X-cap discharge resistor. The STCMB1 internal circuits detect the ac mains plug disconnection by sensing the voltage on the HV pin. After a detection time of 64 ms typical from the mains disconnection, the X-cap discharge operation is triggered and the HV start-up system is turned on: a discharge current (4.2 mA minimum) is drawn from the HV pin ensuring the X-cap discharge until the voltage on the HV pin falls below a safe level (45 V maximum), within the regulation maximum discharging time. The current from the HV pin will flow out from the VCC pin, to keep the IC correctly supplied until the end of the discharge. An internal 15 V clamp is activated to limit the voltage on the VCC pin by sinking the discharge current in excess of the IC consumption.

None additional component is needed by this function, totally embedded in the STCMB1.

# 7.3 Ac brown-out protection

The STCMB1 device is equipped with brown-out protection to prevent the operation at too low ac input voltage (typically when it falls below 70 V ac). When the brown-out protection is activated, the PFC and HB sections are turned off and the HV start-up is on until  $V_{CC}$  reaches the turn-on threshold  $V_{VCCon}$ . When  $V_{CC} = V_{VCCon}$ , the HV generator is turned off, the switching activity does not start and  $V(V_{CC})$  falls again. This VCC recycling operation goes on as long as the abnormal ac mains condition lasts. The brown-out protection is deasserted when the ac voltage goes above the brown-in threshold (typically 80 V ac).

The HV pin has an internally integrated high voltage divider sensing the ac mains voltage, and a peak detector. No any additional component is needed for the voltage sensing, we just suggest inserting an RC filter on the HV pin to clean up the voltage from noise or disturbances that could affect the on-off thresholds. **RC values can be as 8.2 k\Omega and 1 nF,**

16/51 DocID028958 Rev 2

the cut-off frequency of this filter can be in a range down to 3 kHz. RC components voltage rating has to be compatible with the HV pin operating voltage.

In order to avoid unexpected intervention of this protection in case of missing cycles or short dips of the ac mains, a debounce time is introduced; therefore during the operation if a brown-out condition is detected, the converter will stop the operation after 40 ms typ.

When a brown-out condition is detected, any latched protection is cleared.

Figure 6. Brown-in and brown-out operation

### 7.4 VCC pin

This pin is the supply voltage of the IC. An electrolytic capacitor of at least 22  $\mu$ F (typ. value) must be connected between the pin and GND in order to sustain the voltage during the start-up phase and supply the IC, before the self-supply circuitry from the half-bridge transformer deliver enough voltage. Place also a ceramic capacitor (0.1  $\mu$ F typ.) in parallel to the electrolytic capacitor to bypass the high frequency noise to GND and supply the STCMB1 device with a proper clean voltage.

The  $V_{CC}$  voltage is used also to supply the MOSFET gate drivers, not having a dedicated clamping, supplying the STCMB1 from the auxiliary (self-supply) winding from the resonant transformer may need a small BJT voltage regulator to keep the supply voltage regulated and avoid the aging of the gate oxide due to an excessive  $V_{CC}$ , or limit transients that could damage the IC as in case of dead shorts.

A typical V<sub>CC</sub> operating voltage is 12 - 13 V.

#### 7.5 PFC section

The STCMB1 device implements a transition mode PFC section using a proprietary constant on-time control methodology. This control mode does not require a sinusoidal input reference, thereby reducing the system cost and external component count.

It includes also a complete set of protections: the cycle-by-cycle overcurrent (OCP), output overvoltage (OVP), feedback failure (FFP), boost inductor saturation and inrush current detection both at the start-up and after mains sags or missing cycles.

The output voltage (Vout) is controlled by mean of a transconductance error amplifier and an accurate internal voltage reference; "Zero Current Detection" (ZCD) by sensing the voltage on the auxiliary winding on the PFC inductor allow achieving the TM operation.

The current sense on the return path is implemented in order to perform a continuous monitoring of the inductor current. A THD optimization is implemented too.

A "two-level" line voltage feedforward function is integrated too.

#### 7.6 PFC: enhanced constant on-time control with THD optimizer

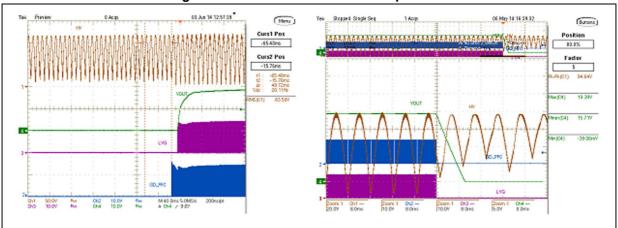

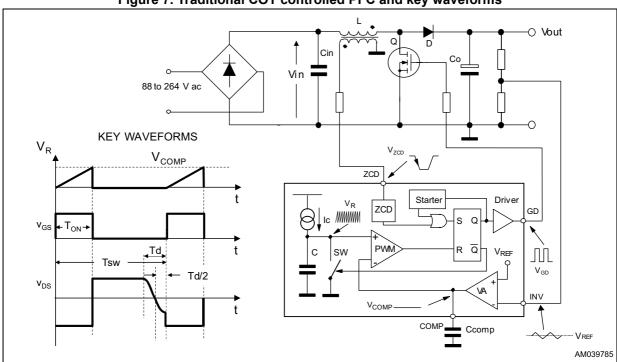

The PFC embedded in the STCMB1 is the transition mode (TM), where the switch is controlled by a constant on-time (COT), having some advantages with respect to other architectures such as simplicity and lower losses because it doesn't require the sensing of the ac mains voltage.

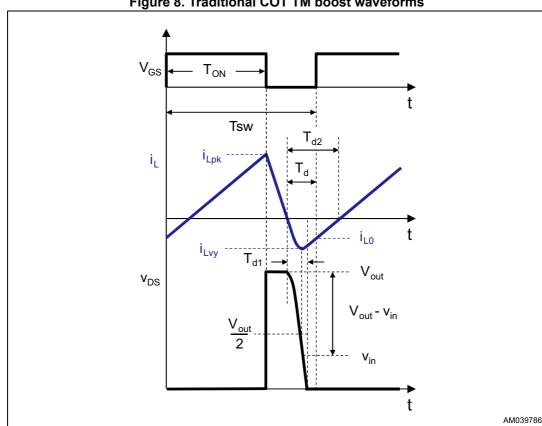

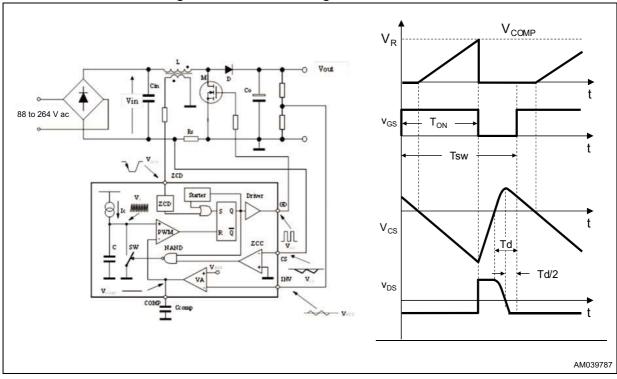

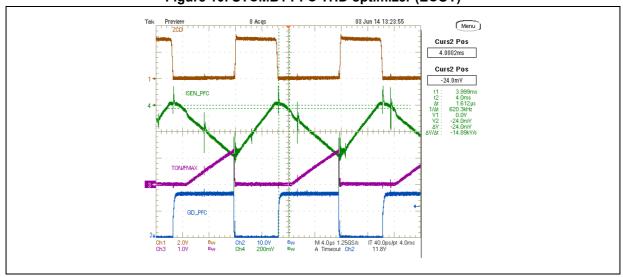

The TM is characterized by good efficiency for the intrinsic zero voltage switching even if the large ripple current requires bigger EMI filters. The COT is a common control technique where the turn-on duration of the power transistor is controlled based only on the output voltage of the converter and is slowly varying, or even constant, during each line cycle. The conjunction of the TM and COT is a very popular solution used in several PFC controllers for output power up to 300 W. The block diagram and key waveforms of the traditional approach are shown in Figure 7.

Figure 7. Traditional COT controlled PFC and key waveforms

The constant on-time control takes advantage of the fact that in the transition mode the current in the inductor at the turn-on is near zero and the slope of the current during on-time is proportional to the input voltage. The power MOSFET is switched on when the current in the inductor reaches zero. Since this causes a resonance between the inductor and the parasitic capacitances of the MOSFET and the diode, the event is usually detected by

18/51 DocID028958 Rev 2

sensing the voltage on an auxiliary winding on the inductor. The MOS is switched off when a sawtooth signal reaches the VCOMP signal, and then the control will wait for the next ZCD.

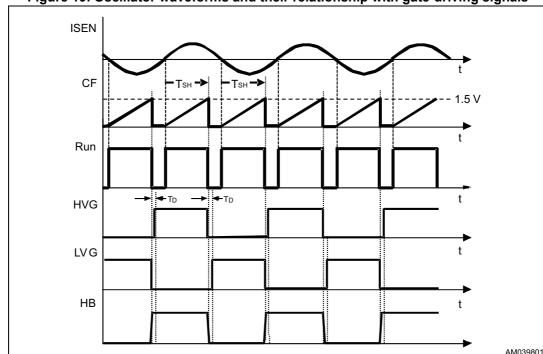

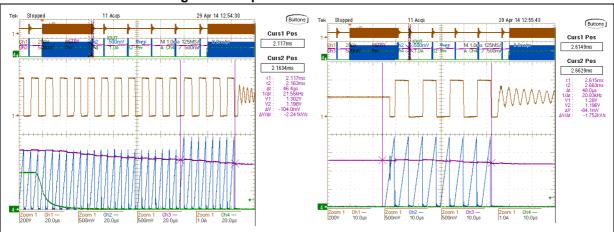

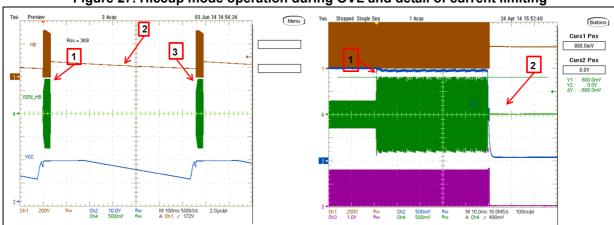

The input current value can be approximated as one half of the triangle inductor current. Additionally, because the instantaneous ac mains input voltage has a perfect linear relation with the current drawn by the circuit, the circuit would ideally provide a perfect unity power factor and no distortion.